11位高性能流水线ADC关键电路的分析

2013-09-26王嘉炜孙佳晶

王嘉炜,孙佳晶,徐 劼,张 力,李 豹

(合肥工业大学,安徽合肥 230009)

0 引言

针对11bit高性能流水线ADC,选择合适的系统架构以满足其高速高精度要求的同时使功耗和噪声指标较优,并确定各模块的设计指标;设计流水线ADC的关键电路,包括高性能采样保持电路,高速、高增益运算放大器,高精度采样开关等关键电路。

1 研究背景

所谓模拟转换器(ADC)即通过将相应模拟信号转换成为有效的数字信号的专业接口电路,其主要功能是将自然界中的模拟输入量依据一定规则转换成为与其相对应的有效数字编码。

ADC性能主要受其电路结构、版图设计以及单元电路性能等因素影响。流水线结构是一种既可实现高分辨率,又可实现高速的结构。当前,大带宽高速运算放大器以及相应高速比较强可以使得ADC转换率得到有效提升。而使用的混合信号版图设计以及自校正技术则有利于增强ADC分辨率。

2 研究设计

2.1 11位流水线ADC架构

确定首级精度时主要受以下一些方面影响:乘法运放增益、电容匹配、带宽以及流水线ADC输入噪声等。

结合精度对相应流水线ADC性能的实际影响,基本对本文流水线ADC的大体架构进行了确定:依据比较器失调电压的具体范围及其电容匹配要求,并结合OTA设计难度以及后级噪声衰减等诸多因素,选取了+2.5bit(第一级)+1.5bit*6(中间6级用1.5bit)+3bit flash 架构,其相应首级2.5bit精度约为2bit,而1.5bit精度约为1bit。0.5bit的冗余量给比较器的失调误差。

2.2 流水线ADC的工作原理

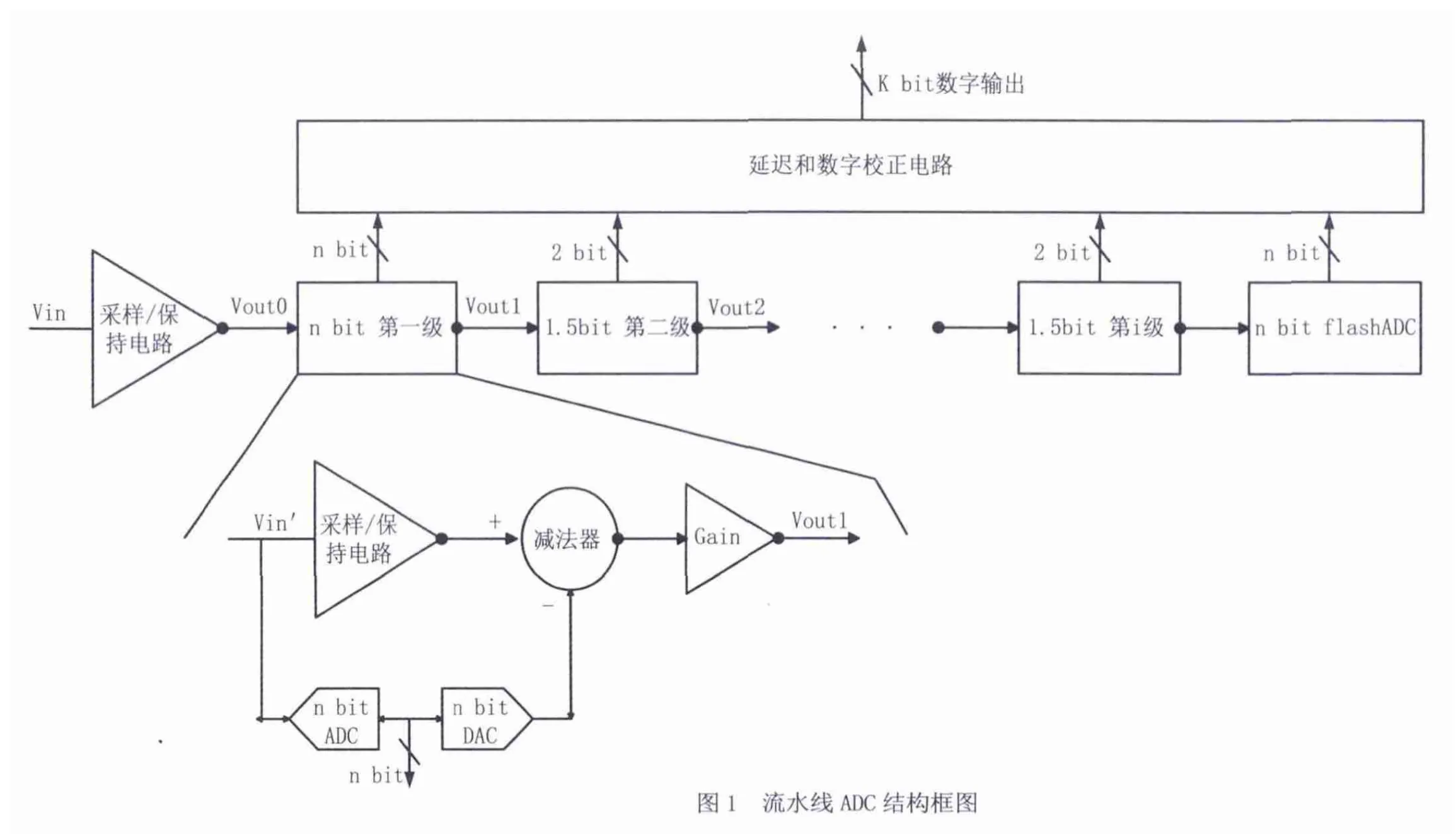

图1是典型流水线ADC系统结构框图,它主要由采样保持电路、多级流水线电路(包括多位的流水线第一级、1.5位流水线后级和最后一级多位快闪式ADC)以及延迟与数字校正电路组成[1]。其中每一级的流水线电路都包括一个子ADC和一个乘法型数模转换器(MDAC)。

一般来讲,流水线ADC之间的所有模块在相应两相非交叠时钟的实际控制之下连续运作,且在采样保持电路保持输出阶段,其流水线基本采取偶数级保持,奇数级采样;反之在采样保持电路采样阶段,流水线奇数级保持,偶数级采样。虽然流水线ADC转换一个采样值需要M个时钟周期(M由流水线级数决定),但是在延迟M个时钟周期后的每个时钟周期都能完成一次转换,因此其转换速率与每一模块的采样速率相同,这也能大大提高流水线ADC对输入信号的处理速度。

在各种结构的流水线ADC中,1.5bit/级带数字误差校正的结构是比较成功的一种,但是流水线电路第一级的分辨率往往比后级1.5bit/级的流水线要高一到两位来降低系统对后级流水线性能的要求[2]。在每一级的流水线电路中,模拟信号首先经过采样保持电路进入子ADC,其输出的粗量化值作为本级的数字输出进入延迟和数字校正电路,同时这个粗量化值被子DAC转化成模拟值与本级的输入模拟量相减,得到的余量经余量放大后作为下一级的输入,此过程由每级MDAC完成。以此类推,每一级的子模块都会产生一个交由数字校正电路处理的低分辨率数字量和一个输入到下一级的输出余量。由于最后一级流水线不需要再输出余量,因此多采用一个低分辨率的flash ADC来降低功耗和芯片面积。

理论上我们可以通过增加流水线级数和各个子模块的速度来增加流水线整体分辨率和速度,然而随着分辨率和速度的不断增加,流水线ADC整体功耗和芯片面积也会大幅度增加,同时噪声及其他非理想因素(如非线性、增益误差、失配等)的影响也会逐渐成为限制其性能的关键因素。

通过上述分析可知,当前流水线ADC由采样保持、数字校正、子ADC以及MDAC等关键电路组成。若能对该些模块的实际工作原理进行充分掌握和了解,对于整个流水线ADC建模来讲,有着重要意义。

2.3 电容翻转式采样保持电路

与电荷转移式采样保持电路相同,电容翻转式采样保持电路也能实现差模输入到输出的精确复制,同时由于只有一个电容,因此也不存在电容失配的影响。另外,电容翻转式采样保持的反馈系数,是电荷转移式采样保持的两倍。对于一个工作在闭环系统的运放来说,较高的反馈系数会使运放的建立时间更短,从而降低运放的功耗。同时电容翻转式采样保持只有一个电容Cs,相比较于电荷转移式,其所产生的KT/C噪声也会降低一倍。

2.4 MDAC 电路

2.5 bit/级的MDAC电路架构图,主要包括采样保持、减法、数模转换以及余量放大等功能。与采样保持电路相同,MDAC也包含两个主要相位:采样相和保持相。

2.5 sub-ADC电路

在式3-7中所示的2.5bit/级MDAC的传输函数中, n的值由sub-ADC决定。sub-ADC的主要功能就是将每级的输入模拟量进行粗量化,产生相应位数的数字码,来控制图3中连接Vref+和Vref-的一系列开关在保持时刻的断开和闭合状态。它实际上就是由锁存比较器、基准电压发生器和数字编码电路组成的一个flash ADC。

在流水线ADC中,sub-ADC一般采用开关电容控制的动态锁存比较器来降低静态功耗,同时获得比较高的速度。但是动态锁存比较器在正反馈节点的MOS管导通或者截止的瞬间会产生一个很大的电压尖峰,通过寄生电容影响到输入端,从而产生回踢噪声。在动态锁存比较器的前端加预放大级电路可有效降低回踢噪声对输入信号的影响,同时,预放大级电路还可放大输入信号,以达到降低比较器传输延时,提高比较速度的效果。

因flash ADC具备结构简单、速度快以及静态功耗低等优点,再加上流水线ADC中的最后一级无需进行余量放大输出,所以最后一级流水线多选择使用多为flash ADC来完成模数转换。

2.6 数字延迟校正电路

根据上面对流水线ADC工作原理的分析可知,流水线ADC前端采样保持和各级流水线是交替工作的,在上一级保持时期,下一级在采样。换言之,本级所处理的输入模拟信号在延迟半周期后才会由下一级输出。在对流水线输出码错位进行相加之前,应通过数字延迟电路来确保各级输出的相应数字量同步

开关电容动态锁存比较器有着低的静态功耗和较快的速度,但是它所引入的失调要比一般的静态比较器大,另外比较器采样电容失配以及sub-ADC与MDAC之间采样时间误差等都会引入失调,这就需要采用数字校正技术来消除这些失调的影响。可采用Stephen H Lewis 提出的数字校正算法来实现对失调误差的校正。这种校准算法的特点是使用错位相加的方法,将sub-ADC所产生的小于1/4Vref的误差消除掉。

3 实验仿真

3.1 流水线ADC整体性能仿真

流水线ADC主要性能指标包括动态性能和静态性能。动态性能指标主要有总谐波失真(THD)、有效位(ENOB)以及有信噪比;而静态性指标则主要有积分非线性(INL)以及微分非线性(DNL)。其中动态性能指标都可以通过对输出正弦信号进行傅里叶变换(DFT),从得到的频谱计算出,而静态指标则需要使用matlab程序对输出信号进行处理得到。SNR=63.2468dB,THD=78.7415dB,SFDR=80.0094dB,ENOB=10.196。

仿真时加入了电容失配误差、时钟抖动误差、运放有限增益误差、运放不完全建立误差、失调误差、开关电容热噪声和运放噪声等非理想因素,并且是在设计允许最高温度398K(125℃)的环境下进行仿真。

通过加入各种非理想因素的11位流水线ADC Simulink模型进行INL以及DNL仿真。进行仿真时,所输入信号约为10m正弦波,且将仿真时间设定为100ms来确保每个数字码采样不少于10个点,同时对最终所得的全部采样点台阶以及理想台阶相对比,来实施码密度分析,从而得出4096个实际台阶与其理想台阶之间的对应误差。而流水线ADC的INL与DNL分别约为-0.3—0.2LSB和-0.13—0.17LSB,以彻底满足相应11位流水线ADC性能要求。

4 总结

文章主要结合流水线ADC工作原理,对11位高性能流水线ADC关键电路进行研究与分析工作,为日后进一步做好ADC关键电路的研究工作提供了一定理论支持。

[1]Yun Chui,Paul R.Gray, Borivoje Nikolic. A 14 bit 12MS/s CMOS Pipeline ADC With Over 100-dB SFDR.IEEE Journal of Solid-State Circuits [J].2004,39(12).2139-2151

[2]R.Zhang,Y.S.Yin,S.Q.Liang,M.L.Gao,“A Multi-bit Digital-to-Analog Converter with Bi-directional overflow detection,” ICSICT.2010.427-429