基于RocketIO的SATA物理层实现

2013-09-17杨佳朋

杨佳朋,张 刚,郝 敏

(太原理工大学信息工程学院,山西太原 030024)

基于RocketIO的SATA物理层实现

杨佳朋,张 刚,郝 敏

(太原理工大学信息工程学院,山西太原 030024)

以Virtex-5系列FPGA内嵌的RocketIO收发器模块为平台,分析SATA(串行高级技术附件)协议的物理层功能,把RocketIO收发器的内部结构特点与协议要求相结合,设计了基于RocketIO收发器的SATA物理层电路。

Rocket IO;SATA协议;高速串行传输

随着硬盘等存储设备容量的增加,对数据传输的速度越来越高,传统的并口硬盘(PATA)的速度已达瓶颈(133 Mbit/s),进一步提高频率,将加大16根数据线间的干扰,使得串行数据传输技术应运而生。SATA(Serial Advanced Technology Attachment)[1],即一种串行数据传输协议,相比并传,改用串行线路进行信号传输,一次只传一位,干扰的降低可以在一定条件下大幅提高频率,一代传输速率已达到150 Mbit/s,再定义更加完善的校验措施使得SATA总线具有广阔的应用前景。但其串并传唤和高频传输增加了实现难度,Xilinx公司在其Virtex-5 LX 系列产品中推出的 RocketIO GTP[2],速率可高达3.125 Gbit/s,是一种可灵活可配置的千兆位级高速串行收发器,为SATA协议相关的传输要求提供了重要参考,简化了设计。

1 SATA协议物理层

本文参照的SATA协议是2001年由 Intel、APT、Dell、IBM、希捷、迈拓等几大厂商组成的 Serial ATA委员会正式确立的 Serial ATA 1.0[1]规范。

协议分4层架构,又下至上依次是物理层、链路层、传输层和命令层,如图1所示。上面3层交互通过物理层实现,故物理层的实现对上面3层的功能具有重要意义。物理层建立SATA信号传输的比特流通路,进行链路初始化、电源管理和热插拔等操作。链路层和传输层协同进行原语的收发、帧信息结构(FIS)[3]的编解码等工作。命令层代表大脑,向下发送读写命令,并接收下层的帧信息向主机端反馈。

图1 SATA架构

物理层位于协议的最底层,用于实现最基本的数据通信环境。内部结构包括模拟前端和控制模块,控制模块与链路层进行交互,向其反馈物理层的工作状态,把控制信号传给模拟前端。作为最基本的传输层,由于各种硬件具备不同的特性和来源,使它实现起来很复杂。采用Xilinx公司Virtex5芯片中的RocketIO收发器,可以简化设计。

2 RocketIO GTP简介及工作原理

2.1 RocketIO GTP 简介

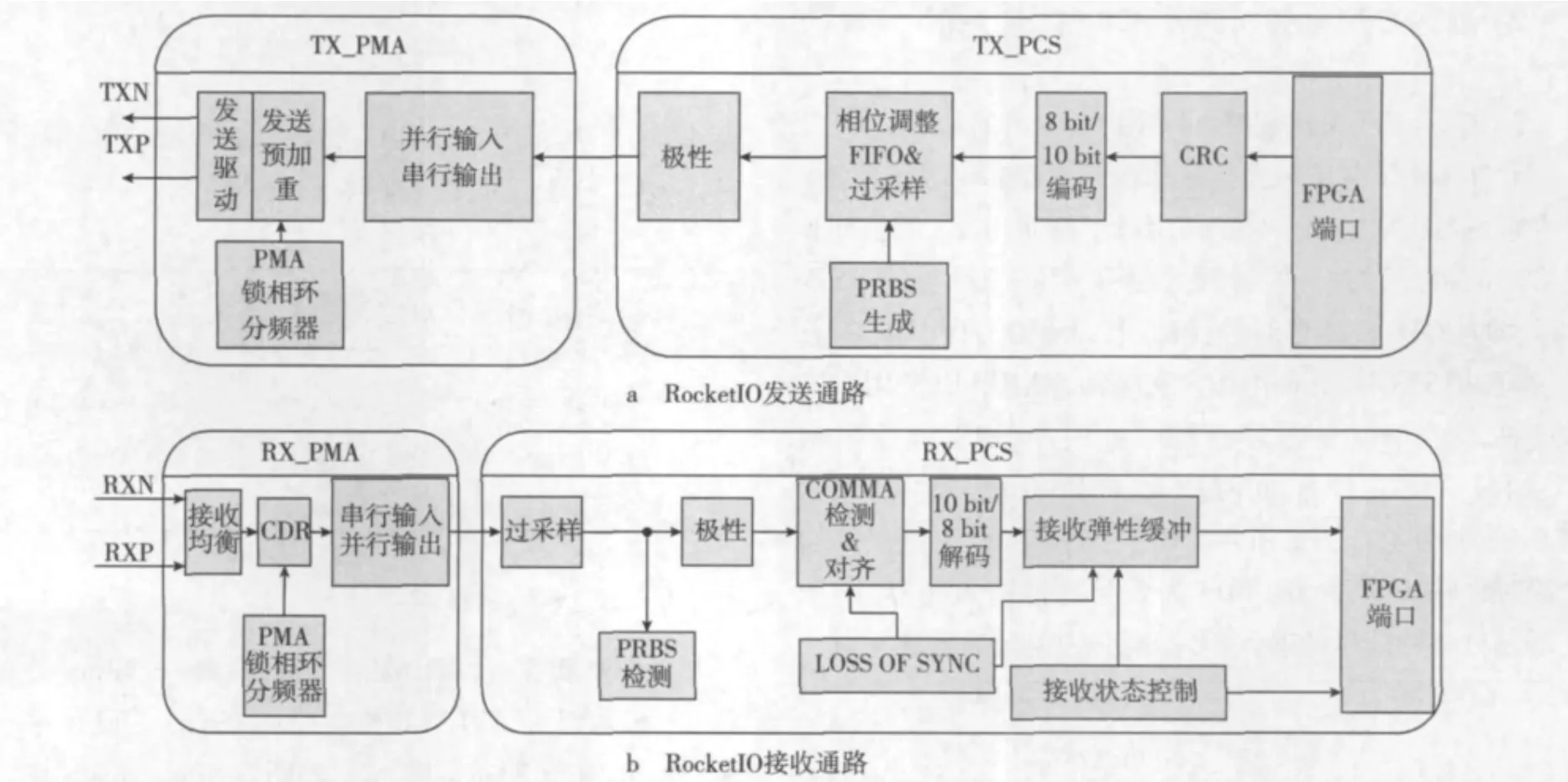

如图2所示,RocketIO GTP由物理介质附属子层(PMA)和物理编码子层(PCS)组成,内部结构紧凑,可根据设计需要自由配置。PMA主要实现串并变换和时钟优化功能,另外包括发送预加重、接收均衡器等在线配置技术以实现最优信号完整性。PCS部分负责编解码工作,包含8 bit/10 bit编解码器和支持通道绑定和时钟校正的弹性缓冲器[4-5],并支持 comma[3]字符检测,确保字节的准确接收。PRBS为伪随机二进制序列,用于测试高速串行通道传输的误码率。CDR(Clock and Data Recovery)为时钟数据恢复电路,和接收均衡器协同负责从一个复合的信号中把时钟和数据都正确地恢复出来。图中CRC校验在链路层实现,在本模块并不涉及。可见,RocketIO GTP的相关功能为SATA物理层内部关键模块的实现提供了重要技术支持。

图2 RocketIO结构

2.2 RocketIO GTP 工作原理

并行数据进入RocketIO GTP发送端经过8 bit/10 bit编码,写入到发送端FIFO,再转换成串行差分数据发送给设备。接收端的串行数据信号要首先经过均衡器处理,写入到接收端缓冲,恢复出接收时钟,在时钟的驱动下转换成并行数据,再次经过10 bit/8 bit解码,被写入弹性缓冲区,并做CRC检验后并行输出。简而言之,就是将输入的并行数据经过编码,转化为高速的差分串行信号;同时接收高速串行信号,进行时钟和数据恢复,转换成并行数据输出。

3 系统设计

SATA1.0协议[1]规定物理层的数据传输速率为1.5 Gbit/s,每个时钟周期传输一位,考虑8 bit/10 bit编码,故实际速率为150 Mbit/s,参考时钟设为150 MHz。OOB[6]信号为带外控制信号,分别为 COMWAKE,COMRESET,COMINIT,相对于数据传输具有优先级,实现初始化和电源管理模块。COMRESET只由主机发送,开始复位,COMWAKE双方都可以发送,交互中唤醒对方,COMINIT只由设备发送,表示初始化连接。配置过程中,每2个GTP0和1共用1个锁相环(PLL),构成1个 GTP_DUAL,根据开发板 Datasheet选用了 GTP_DUAL_X0Y0。RocketIO GTP端口参数配置如表1所示。

表1 GTP配置参数

并行数据位宽INTDATAWIDTH信号设置为10 bit。当选择SATA时,接收状态控制信号RXSTATUS[0]表示OOB信号操作完成,RXSTATUS[1]表示收到COMWAKE信号,RXSTATUS[2]表示收到 COMRESET或 COINIT信号。RX Termination配置终端,VTTRX表示参考内部电压摆幅。RXLOSSOFSYNC为0代表8bit/10bit错误,1代表弹性缓冲中的通道绑定序列。TXENOOB用于发送,RXSIGDET用于接收共同管理OOB控制信号,通过配置的RocketIO GTP作为SATA物理层[7]的模拟前端电路。

3.1 时钟控制

为提高时钟精度,降低抖动,满足GTP的高速运作,需要配置高精度的时钟。首先参考时钟分频产生锁相环时钟,借助于内嵌在GTP_DUAL中的共享PMA锁相环,驱动GTP收发器的发送和接受通路。参考时钟有3种方式提供:

1)使用外部振荡器驱动专用时钟布线;

2)通过专用时钟布线使用相邻 RocketIO模块的时钟;

3)使用 FPGA 内部时钟(GREFCLK[2])。

由于GREFCLK数据传输率低于1 Gbit/s,不予考虑。综合前两种时钟方式,本文采用以下解决方案:150 MHz的参考时钟经过差分时钟输入缓存(IBUFDS)生成REFCLK作为GTP的参考时钟;根据RocketIO GTP内部四通道绑定,把TXOUTCLK用作发送时钟,RXREFCLK用作接收时钟,两个时钟信号经全局时钟缓冲(BUFG)输出到TX_CLK和RX_CLK,同时作为 TXUSRCLK和 RXUSRCLK的时钟源,如图3所示。BUFG为Xilinx用户提供的全局时钟输入缓存,IBUFDS为差分时钟输入缓存,用于外部差分时钟信号的输入,可提高时钟信号的驱动能力。

图3 时钟分布图

3.2 复位模块

复位分为发送部分和接收部分,分别维护系统的稳定。以发送模块为例,如图4所示,为了抑制外部复位信号输入时的抖动情况,对GTP_RESET信号进行两级移位寄存器与操作,产生2个时钟周期的延迟,保证足够的复位时间,这样该信号使能时的抖动就基本被滤除,配合时钟信号从而保证整个系统逻辑的稳定可靠。

3.3 数据通路

由于只是模拟物理层,没有上层架构发送数据,故在发送时钟tileo_txusrclk0_i的驱动下,由计数器发数、由RAM存储。在接收时钟的触发下,由接收端接收、由串口模块显示。构成GTP_DUAL的0和1两端口复用相同资源,只列举0端口重要的参数,如表2所示。

图4 复位模块

表2 端口配置

4 验证及总结

整个流程采用VHDL语言编写,基于Xilinx公司的Vritex-5系列XC5VLX110T芯片在ISE10.1设计平台上完成综合、仿真和布局布线。如图5所示,txdata在计数器的驱动下发送数据,rxdata0和rxdata1为2条接收通道,经过系统预设的20,65,85,6B后从BC开始接收数据,与发送端数据一致,实现了正确接收。通过验证,本文对时钟部分的设计可以正确接收发送的数据,同时符合SATA1.0协议,集成度高、稳定性强。

图5 仿真图(截图)

5 小结

高速串行传输技术把时钟与数据合并发送,再利用同步检测正确恢复出时钟,解决了高速数据传输过程中的抖动问题,降低设计复杂性和成本。本文基于Xilinx公司的Virtex 5 LX系列FPGA器件中内嵌的Rocket IO IP核具有配置灵活、集成度高等优点,把它用于SATA物理层,实现了高效稳定的数据传输,具有重要的现实意义。

:

[1]Serial ATA:High Speed Serialized ATAttachment Rev.1.0a[EB/OL].[2012-06-01].http://www.doc88.com/p-015901791536.html.

[2]Xilinx.Virtex-5 FPGA RocketIO GTP Transceiver User Guide[EB/OL].[2012-06-01].http://wenku.baidu.com/view/f76b533210661 ed9ad51f34f.html.

[3]邓焰,戎蒙恬.基于FPGA的3.125Gbit/s串行通道设计实验[J].电子工程师,2004,30(11):16-18.

[4]李江涛.RocketIO高速串行传输原理与实现[J].雷达与对抗,2004,23(4):48-50.

[5]武荣伟,苏涛,梁中英.RocketIO在高速数据通信中的应用[J].通信技术,2010,43(11):9-11.

[6]欧阳科文,黎福海,唐纯杰.基于RocketIO的SATA物理层高速串行传输实现[J]. 计算机测量与控制,2009,17(5):937-938.

[7]胡锦,彭成,谭明.基于RocketIO的高速串行协议设计与实现[J].微计算机信息,2008,24(18):196-197.

Implementation of SATA Physical Layer on RocketIO

YANG Jiapeng,ZHANG Gang,HAO Min

(College of Information Engineering,Taiyuan University of Technology,Taiyuan 030024,China)

The functional requirements of SATA(Serial Advanced Technology Attachment)protocol physical layer is analyzed in this paper.On the Virtex-5 family of FPGA embedded RocketIO transceiver platform,it combines the characteristics of the internal structure with the protocol demand and designs the physical layer circuit based on the RocketIO.

RocketIO;SATA protocol;high-speed serial transmission

TP393.04

A

【本文献信息】杨佳朋,张刚,郝敏.基于RocketIO的SATA物理层实现[J].电视技术,2013,37(3).

国家自然科学基金项目(60772101)

杨佳朋(1988— ),硕士生,主研嵌入式与通信;

张 刚(1953— ),教授,博士生导师,主研视频编码与嵌入式系统;

郝 敏(1988— ),硕士生,主研视频监控。

责任编辑:魏雨博

2012-06-29