用于星载图像高速传输的千兆以太网接口设计

2013-09-17宋光磊祝海江

刘 鑫,宋光磊,温 靖,祝海江,李 茂

(1.北京化工大学信息科学与技术学院,北京 100029;2.中国空间技术研究院 513所北京研发中心,北京 100191;3.北京系统工程研究所,北京 100076)

用于星载图像高速传输的千兆以太网接口设计

刘 鑫1,宋光磊2,温 靖2,祝海江1,李 茂3

(1.北京化工大学信息科学与技术学院,北京 100029;2.中国空间技术研究院 513所北京研发中心,北京 100191;3.北京系统工程研究所,北京 100076)

基于TI公司的TMS320C6455芯片及外围PHY芯片设计并实现了DSP的千兆以太网接口,为演示样机的性能检测提供了通道。设计采用的PHY芯片为低功耗CMOS工艺的ET1011芯片,在DSP/BIOS嵌入式操作系统上通过调用TI公司提供的NDK开发套件完成TCP/IP协议栈,最终实现数字信号的以太网传输。在DSP千兆以太网软件设计时还编制了底层http协议和相应的网络访问线程,可以通过PC机直接访问所建立的千兆网平台主页面。

TMS320C6455;千兆以太网接口;DSP/BIOS;NDK

【本文献信息】刘鑫,宋光磊,温靖,等.用于星载图像高速传输的千兆以太网接口设计[J].电视技术,2013,37(3).

随着信息技术和网络技术的飞速发展,嵌入式系统的网络化也是大势所趋,如何实现嵌入式系统的高速率和高准确率数据传输逐渐成为近年嵌入式系统的研究热点。由于千兆以太网容易集成而且具有速率快、距离远和向下兼容10 M/100 M以太网等特性,因此研究DSP千兆以太网对于实现系统网络化具有重要的实际意义[1]。目前,基于TMS320C6455的百兆以太网传输效率高达98%(98 Mbit/s)左右,而普通千兆以太网传输效率仅为25%(250 Mbit/s),因此基于该芯片的千兆以太网接口的传输效率还有很大的提升空间。

本课题设计用于演示验证星载高速图像并行处理器,由于卫星遥感图像的信息量巨大,采用并行处理架构时,处理器模块间需要很高的传输速率进行数据交互,一般高于1 Gbit/s,这就要求硬件平台能够提供稳定高速率的工作环境。本文结合智能性、时效性和快速响应性的应用需求,采用TI公司推出的TMS320C6455芯片和ET1011芯片设计并实现了DSP的千兆以太网接口,为星载海量图像处理系统提供演示验证的数据传输通道,实现并行处理模块间的高速数据传输,并通过速率测试验证了设计的可行性。该接口保证演示样机所搭建的整个并行处理系统可以进行稳定且高速率的图像处理和数据传输,并且提供了演示样机性能的检测通道,为下一步研制星载功能样机实现奠定了基础。

1 硬件接口的设计与实现

TI公司推出的TMS320C6455芯片是一款高性能、定点数字信号处理器,其最高工作频率为1.2 GHz。由于该芯片内部集成了千兆以太网接口模块,因此可以结合PHY芯片及外围电路实现系统的千兆以太网通信功能。

ET1011芯片采用的过采样架构与传统架构相比具有更强的从信道获取信号能力。这些获取的额外信号使得它能够提供更加稳定的工作平台,节约成本并且降低了整体功耗。与此同时,这种过采样架构实现了更优的均衡使得芯片具有更强的抗时钟抖动能力,从而改善了误码率。

TMS320C6455与 ET1011芯片都提供了 RGMII,GMII,MII接口,两者之间可以在IEEE802.3标准基础上实现无缝连接。本方案EMAC模块连接框图如图1所示[2-3]。

图1 千兆以太网接口框图

方案设计中DSP和ET1011都工作在GMII模式。设计充分考虑到过冲、欠冲、串扰等对系统时序的影响,故通过Cadence软件对系统信号完整性和时序进行仿真。方案设计要求尽量减小传输线效应,缩小PCB面积,然而高密度的设计将会延长开发周期并给调试增加难度,故方案最终在以上两个方面做了折中。

2 千兆以太网接口软件设计

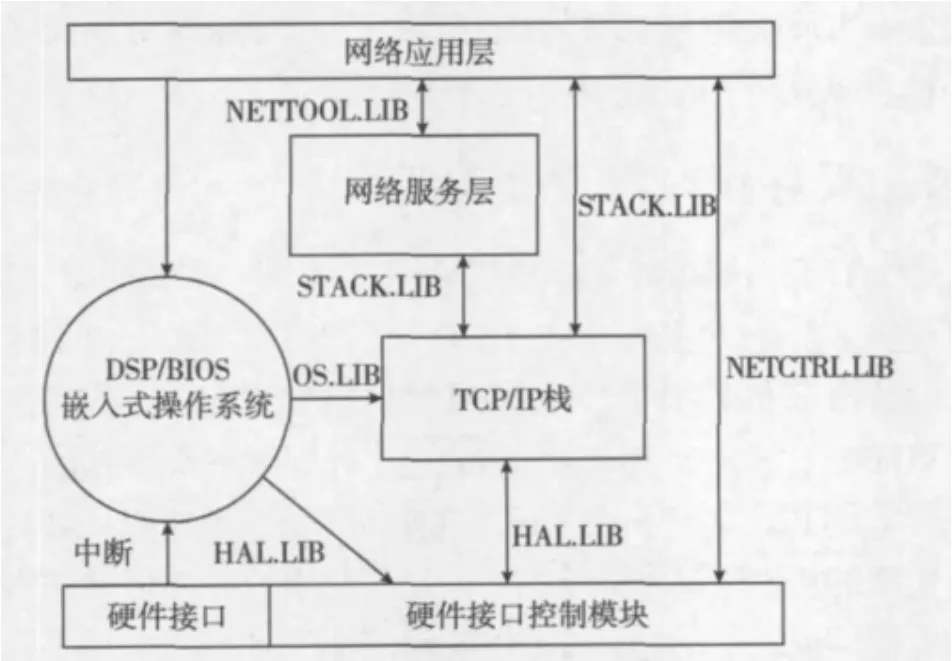

DSP上的软件设计主要包括:接口驱动程序、配置运行TCP/IP协议栈以及用户应用测试程序3个部分。接口驱动程序主要完成对EMAC模块以及MDIO模块的配置,包括复位、中断使能、部分寄存器的初始化等,并且完成硬件模块与TCP/IP协议栈通信需要的操作接口。配置TCP/IP协议栈主要是基于CCS3.3中提供的DSP/BIOS操作系统,通过调用TI公司提供的NDK开发套件实现。整体结构框图如图2所示。

图2 千兆以太网软件结构

2.1 DSP/BIOS工作原理

DSP/BIOS是一个尺寸可伸缩的实时内核。它可以满足实际应用中的实时线程调度与同步、主机与目标DSP之间通信及实时监测等要求。与此同时,DSP/BIOS还提供了抢占式多(RTOS)线程、硬件抽象、实时分析和配置工具等。在抢占式任务切换中,始终保证优先级最高的任务立即执行[4]。

本方案设计中编写了数据发送线程和网页访问线程,为了保证传输速率不受影响,设置数据发送线程优先级高于网页访问线程,即只有当数据发送线程处于终止态时才可以进入网页访问线程。

2.2 基于NDK开发套件的TCP/IP栈建立

NDK套件主要包括:支持TCP/IP协议栈程序库、示范程序以及支持用户文档3个部分。仅用200~250 kbyte程序空间和95 kbyte数据空间即可支持常规的TCP/IP服务,包括应用层的 Telnet,DHCP,HTTP 等[5]。

考虑到NDK对CCS中链接目标函数和库文件的顺序非常敏感,故程序设计时尽量按照推荐的顺序添加NETCTRL.LIB和STACK.LIB等文件。其中NETCTRL.LIB管理所有网络事件、协调操作系统与硬件驱动;HAL.LIB提供对硬件的支持;NETTOOL.LIB提供网络服务;STACK.LIB提供了顶层至底层的所有功能;OS.LIB提供与DSP/BIOS操作系统的接口,可以根据需要打开和关闭OS网络接口功能。

2.3 整体程序设计流程图

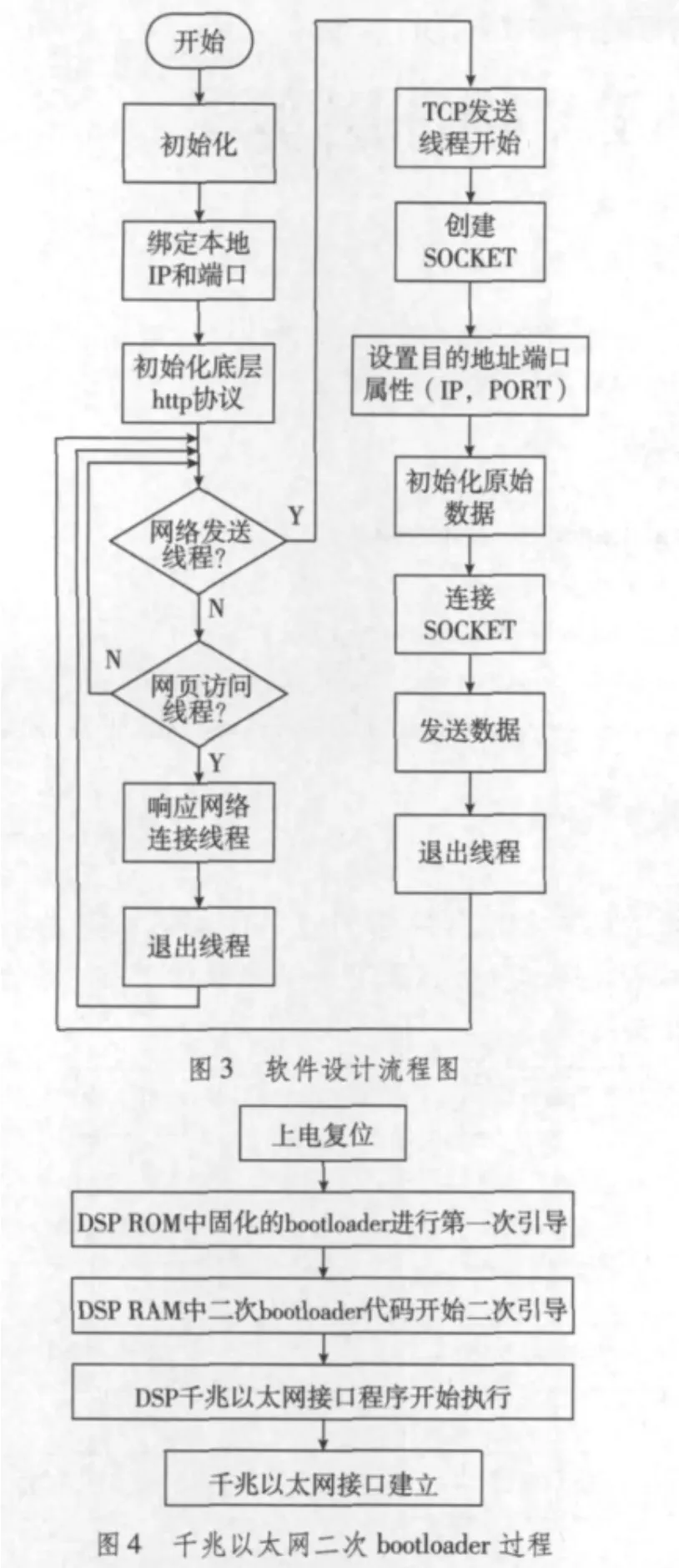

当成功建立GMII端口后,绑定本地IP地址和端口,初始化底层的http协议并编制简单的网络页面,程序则开始监测有无网络传输线程和网页访问线程。当有传输线程接入,则进入该线程开始发送数据。发送数据线程结束后可以响应访问页面线程,此时通过PC机可以访问平台界面。整个程序在DSP/BIOS操作系统上采用C语言及汇编语言编写,结合调用DSP/BIOS的功能函数实现。具体程序流程图如图3所示。

3 NOR Flash烧写

电路设计中采用的NOR Flash型号为S29ALD32D。处于Flash引导模式下的TMS320C6455上电时其内部ROM中固化的“bootloader”将自动完成Flash的第一次引导。由于上述DSP自动引导的内容仅仅包含Flash ROM的前1 kbit地址空间,而本方案所设计的DSP千兆以太网接口代码包含bios段(支持DSP/BIOS内核的运行)、cinit段(C语言的运行环境)、text段(可执行二进制代码)等共16段代码,其大小远远超过1 kbit。因此,需要在DSP的第一次引导基础上进行NOR Flash的二次加载,该二次加载完成程序中16段代码的搬移工作并最后跳转至程序入口,最终完成DSP千兆以太网接口程序上电自启动。整个加载过程如图4所示。

通过添加了二次bootloader代码并且修改了cmd文件后的工程在CCS3.3下生成out文件,此out文件中含有一些只能被仿真器识别的头文件以及定位信息等,而NOR Flash则不能识别这些内容,因此还需要利用TI公司提供的十六进制转换工具将所生成的out文件转换成Flash可以识别的二进制hex文件。最后通过TI的第三方软件Flashburn完成该hex文件的烧写。

4 测试结果及分析

DSP与PC机之间通过网线连接,PC机端的IP地址应设置成与DSP端所建立的网口IP地址在同一网段内。PC机操作系统为Windows XP,网卡是Broadcom NetLink(TM)Gigabit Ethernet。传输线程中设定DSP向PC机发送100 000包数据,每包包含32 kbyte纯数据。多次数据传输速率测试结果如表1所示。

表1 数据传输测试结果 Mbyte/s

通过表中测试结果可知所建立的千兆以太网口传输速率在45 Mbyte/s左右,峰值速率可达50 Mbyte/s(400 Mbit/s),峰值传输效率达到40%。根据智能化在轨数据处理系统技术指标要求,将遥感图像通过千兆以太网接口分发至两个处理模块进行并行处理,传输速率可以满足图像处理帧周期为2.9 s、每帧700 Mbit像素的图像处理需求,故本方案所搭建的千兆以太网接口能够支持演示样机的验证工作。

5 结束语

结合TI公司提供的DSP/BIOS操作系统以及NDK开发套件设计并实现了TMS320C6455的千兆以太网接口,并且通过最终测试所建立的千兆以太网口能够进行稳定且高速率的工作,从而为模拟样机与上位机Internet实现高速大数据量传输奠定了基础,扩展了系统的网络通信功能,为模拟样机的性能检测提供了测试通道。

:

[1]IEEE 802.3-2005_COR1-2006,IEEE Standard for Information technology-Part 3:Carrier Sense Multiple Access With Collision Detection(CSMA/CD)Access Method and Physical:Layer Specifications[S].2006.

[2]ET1011C Gigabit Ethernet Transceiver[EB/OL].[2012-05-10].http://www.lsi.com/products/networkingcomponents/Pages/ET1011C.aspx.

[3]TMS320C64x 定点 DSP[EB/OL].[2012-05-10].http://www.ti.com.cn/lsds/ti_zh/dsp/c6000_dsp/c64x/products.page.

[4]TMS320C6000 DSP/BIOS 5.31 Application Programming Interface(API)Reference Guide[EB/OL].[2012-05-10].http://www.doc88.com/p-491988328884.html.

[5]TMS320C6000 Network Develop’s Kit(NDK)Software User’s Guide[EB/OL].[2012-05-10]. http://wenku.baidu.com/view/a74d6dc24028915f804dc27d.html.

[6]罗军舟,黎波涛,杨明,等.TCP/IP协议及网络编程技术[M].北京:清华大学出版社,2006.

宋光磊(1979— ),高级工程师,主研星载计算机卫星测控系统;

温 靖(1981— ),工程师,主研雷达信号处理;

祝海江(1971— ),副教授,主研计算机视觉,信号处理及检测;

李 茂(1980— ),工程师,主研运载火箭信息应用与网络控制。

Design of Gigabit Ethernet Interface Used on Highspeed Transmission of Spaceborne Images

LIU Xin1,SONG Guanglei2,WEN Jing2,ZHU Haijiang1,LI Mao3

(1.College of Information Science&Technology,Beijing University of Chemical Technology,Beijing 100029,China;2.Beijing R&D Center,No.513 Institute,China Academy of Space Technology Corporation,Beijing 100191,China;3.Beijing Institute of Systems Engineering,Beijing 100076,China)

The Gigabit Ethernet interface based on TI chip TMS320C6455 and PHY chip is designed and implemented in this paper,which provided a channel for the performance testing of the demonstrator.Based on DSP/BIOS embedded system and cooperating with TI Network Developer’s Kit(NDK),the chip with low power consumption CMOS technology ET1011 PHY is used to complete TCP/IP protocol stack and finally transports digital signal through Ethernet.When designing software of DSP Gigabit Ethernet,the bottom HTTP protocol and its corresponding network access thread is written,through which it can access the mainpage of gigabit platform with PC.

TMS320C6455;Gigabit Ethernet interface;DSP/BIOS;NDK

TP393

A

刘 鑫(1989— ),硕士生,主研DSP图像处理系统及图像处理算法;

责任编辑:魏雨博

2012-06-13