基于HDLC协议的列车网络接口单元设计与实现

2013-09-17贺竹林王东响朱琴跃

贺竹林,王东响,朱琴跃

0 引言

HDLC(High-Level Data Link Control)协议是一种面向比特的高级数据链路控制规程,由于其通信速率高、差错检测能力强、支持透明传输等优点,广泛应用于包括列车控制网络在内的诸多现场总线通信领域[1]。目前,国内应用于列车通信网络中的HDLC设备大多从国外引进,而国内部分研发机构也基于FPGA对HDLC协议控制器进行了设计[2-5]。随着国内列车通信网络中HDLC通信接口设备应用的日益广泛,对相关产品的国产化研究就显得尤为必要。为此,本文在深入研究HDLC协议标准的基础上,对基于该协议的列车网络接口单元的设计和实现进行了研究,以期为该产品下一步真正应用于列车通信网络系统打下基础。

1 HDLC网络通信原理

1.1 HDLC协议链路结构

根据ISO13239国际标准,HDLC协议主要有NRM(Normal Response Mode)、ARM(Asynchronous Response Mode)、ABM(Asynchronous Balanced Mode)3种工作模式,它们分别针对非平衡链路结构和平衡链路结构的网络工作情况[6]。

本设计主要针对HDLC网络工作在NRM方式下进行研究。在该方式中,整个网络由一个主站和多个从站组成。主站主要功能是发送命令(包括数据信息)帧、接收响应帧,并负责对整个链路控制系统的初启、流程的控制、差错检测或恢复等;从站主要功能是接收由主站发来的命令帧,向主站发送响应帧,并且配合主站参与差错恢复等链路控制。主站与从站之间采用RS485通信,一个主站最多可以挂载31个从站,在半双工模式下通信速率最高可达10Mbit/s。HDLC协议的网络拓扑结构,如图1所示:

图1 HDLC网络拓扑图

1.2 HDLC基本帧格式

HDLC协议是一种面向比特的数据链路规程,在通信过程中报文的收发以HDLC帧的形式进行。根据ISO13239国际标准,HDLC报文帧由起始段、地址段、控制段、信息段、校验段、终止段构成,其基本帧格式,如表1所示:

表1 HDLC基本帧格式

在HDLC基本帧格式中,起始段和终止段均为0x7E;地址段存放发送站或接收站的地址;控制段包含对整个链路的控制信息;信息段存放的则是用户待发送的数据;校验段的内容是从地址段到信息段的校验和,根据实际需求可选用CRC-8、CRC-16、CRC-32 3种校验方式。从地址段到校验段的比特位均参与透明传输,即在数据帧收发过程中,发送端进行 5 连‘1’插‘0’操作,接收端进行 5 连‘1’删‘0’操作。

1.3 HDLC帧类型及功能

根据数据帧中控制字段的比特指派不同,可以将HDLC帧分成I帧、S帧和U帧3种类型。I帧主要用于信息的传输;S帧负责数据帧传输过程中的流控制;而U帧用于数据链路的建立和拆除。HDLC帧控制段的比特指派与帧类型的对应关系,如表2所示:

表2 帧类型与控制段编码

其中,在数据帧收发过程中,具体可以通过RR帧、RNR帧、REJ帧、SREJ帧4种S帧来实现流控制,这4种帧的具体功能如下。

RR帧——接收准备好,准备接收N(R)帧,前N(R)-1帧已正确接收。

RNR帧——接收未准备好,暂停接收N(R)帧,前N(R)-1帧已正确接收。

REJ帧——拒绝接收,重新发送N(R)及其以后各帧,前N(R)-1帧已正确接收。

SREJ帧——选择拒绝接收,只要求重新发送第N(R)帧,其它帧均已正确接收。

2 网络接口单元硬件设计

2.1 硬件总体结构设计

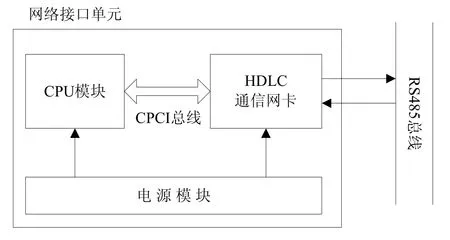

网络接口单元主要由嵌入式CPU模块、HDLC通信网卡以及电源三大部分组成。其中CPU模块主要负责对HDLC通信网卡的调度与数据收发控制;HDLC通信网卡负责HDLC帧的封装和解析,以及对整个数据链路的控制;电源模块用于对CPU模块和HDLC通信网卡供电。网络接口单元内部的CPU模块与HDLC通信网卡之间基于CPCI总线进行连接,该网络接口单元采用RS485通信接口与其它单元进行通信,具体硬件总体结构,如图2所示:

图2 网络接口单元硬件框图

2.2 HDLC通信网卡设计

本通信网卡主要基于协议控制器SAB82532进行设计。SAB82532是西门子公司开发的一款增强型高级多协议串行通信控制器(ESCC),它能够实现高级链路控制协议的同步或异步串行通信,最高传输速率可达到10Mbit/s[7]。

在本文设计的HDLC通信网卡中,协议控制器SAB82532向上通过CPCI总线与嵌入式主控CPU相连,向下通过RS485总线收发器与其他网络接口单元的HDLC网卡进行通信,相应网卡的硬件框图,如图3所示:

图3 HDLC网卡硬件框图

本网卡硬件设计中主控CPU采用存储器映射方式对外围器件进行寻址。系统中CPU通过CPCI总线为SAB82532分配的地址空间为0x83002000~0x830021FF,并采用译码器进行地址选择。SDRAM选用MT48LC2M32B2-7,它是一款具有2M*32bit存储容量的随机存储器,最高工作频率可达143MHz,能够满足系统对存储深度和存储速度的要求。RS485总线收发器采用MAX485,网络节点之间的通信采用半双工方式,通过协议控制器的/RTS信号来控制RS485收发器的数据接收和发送。由于SAB82532是双通道,故每个接口单元都连接两个MAX485芯片。

3 网络接口单元软件设计与实现

在上述硬件设计的基础上,本网络接口单元的软件主要从HDLC通信网卡板级通道驱动软件和应用层通信软件两方面进行设计。

3.1 HDLC通信网卡板级驱动软件设计

3.1.1 SAB82532初始化设置

SAB82532协议控制器支持HDLC、ASYNC、BISYNC 3种通信协议,该器件还拥有两个独立的通道,每个通道在HDLC通信协议下都有4种不同的工作模式,通过配置寄存器参数可以实现通信协议和工作模式的选择,并且还可以设定通信波特率、CRC校验方式、地址字段大小等参数。其中,SAB82532在HDLC协议下的4种工作模式分别为:

(1)自动模式:自动识别地址字段,地址字段为8位或16位,窗口尺寸为1,报文长度不限,能够自动处理S帧和I帧。

(2)非自动模式:自动识别地址字段,地址字段为8位或16位,窗口尺寸不限。

(3)透明模式:自动识别地址字段,地址字段为8位或16位。

(4)扩展的透明模式:全透明传输,FLAG、CRC、Info字段以及位填充可以自己定义,灵活性大。

表3为HDLC通信采用透明模式进行信息输时协议控制器相关寄存器参数配置情况,如表3所示:

表3 SAB82532寄存器参数配置

其中,SAB82532的波特率设置有标准型和增强型,标准型中N=(BR9~BR0)D,XTAL时钟分频因数为k=(N+1)*2,分 频 范 围 为 2~2048; 增 强 型 中 N=(BR5~BR0)D,M=(BR9~BR6)D,XTAL时钟分频因数为k=(N+1)*2^M,分频范围为1~2097152。本文为了达到高速通信的目的,采用20MHz晶振,工作在标准波特率生成方式下,因此通信速率范围为10Kbit/s~10Mbit/s,用户可以通过人机界面灵活设定。

另外,HDLC网络工作在NRM时,通信节点地址的设置如下:本节点地址应写在RAL1和RAL2寄存器中,并且RAL1=RAL2;主站发送帧的目标地址根据命令帧和响应帧不同分别写在XAD1和XAD2中;从站发送响应帧的目标地址只能是主站,故从站XAD1=主站RAL1=主站RAL2;从站无需发送命令帧,故从站的XAD1无需设定。

3.1.2 HDLC通道数据收发软件设计

SAB82532协议控制器在通信过程中均通过发送缓存器XFIFO和接收缓存器RFIFO分别进行数据帧的发送和接收,其每个通道的数据发送和接收流程分别,如图4、图5所示:

图4 HDLC数据发送流程

图5 HDLC数据接收流程4.2网络接口单元通信软件的设计与实现

由图4、图5可知,当发送HDLC数据帧时,首先需要读入超时定时器t1的时间间隔和超时重传次数n1,并使能发送寄存器XFIFO,而后产生一个中断,并判断上次启动的定时器是否超时,若超时则重传,直至超过重传次数n1;而接收HDLC数据帧时,首先需使能接收寄存器RFIFO,而后读出RFIFO中的数据帧,判断该帧格式和帧编号是否错误,若错误则丢弃,否则将该帧中信息解析后上交,并清空RFIFO寄存器。

网络接口单元应用层的通信软件基于VC++开发平台进行设计。通过调用Windows系统底层提供的一些API函数以及HDLC通信网卡所提供的板级驱动函数,用户可以很方便地设计友好的人机界面实现通信节点的参数配置和数据的收发功能。一般地,网络接口单元应用层的数据通信软件流程,如图6所示:

图6 网络接口单元通信流程

3.2.1 基本API函数设计

由图6可知,网络接口单元在上电后需对协议控制器进行各个寄存器的复位、通道检测以及寄存器相应参数的配置工作。为了使用户能在应用层对多达几十个寄存器直接进行访问操作,而屏蔽掉每个寄存器底层不同硬件地址的差异,本软件中采用DeviceIoControl()函数实现对各个寄存器的直接访问,该函数的原型如下:

其中,设备句柄用来标识所访问的设备,通过设置不同的控制码,可以调用设备驱动程序的不同类型的功能。本函数设定的参数以结构体的形式放在输入缓冲区中,该结构体将SAB82532用到的32个寄存器定义为无符号整型。

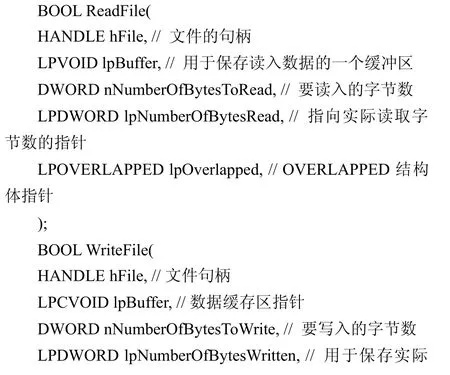

类似地,为了便于在应用层对协议控制器的XFIFO和RFIFO进行直接访问从而实现数据的发送和接收功能,软件中采用WriteFile()函数来实现将待发数据写入SAB82532的XFIFO寄存器,并由协议控制器负责将数据封装成帧发送出去,其中XFIFO大小为32字节。同理,数据接收功能则采用ReadFile()函数予以实现,具体实现时,采用单独的读线程实时检测RFIFO的状态,当RFIFO非空时就读取其中的数据,RFIFO寄存器的大小也为32字节。WirteFile()函数和ReadFile()函数的原型分别如下:

3.3 其它API函数封装设计

为了方便用户进行通信过程软件的二次编程开发,本设计在原API函数基础上封装设计了一些常用的输入输出函数分别如下:

int OpenPort(int PortNumber); //端口打开函数,PortNumber取值为0或1,端口打开成功返回1,失败返回0,PortNumber设置错误时返回-1。

int ClosePort(int PortNumber); //端口打开函数,PortNumber取值为0或1,端口关闭成功返回1,失败返回0,PortNumber设置错误时返回-1。

BOOL InitSet(int PortNumber, int BaudRate, int CheckSum,BYTE LocalAddress);//板卡初始化函数,初始化成功返回TRUE,失败返回FALSE。

BOOL TransmitData(int PortNumber,Byte TargetAddress,CString Data);//发送数据函数,TargetAddress为发送数据的目标节点地址,大小为一个字节,Data为所要发送的字符串数据,大小不限。数据发送成功返回TRUE,失败返回FALSE。

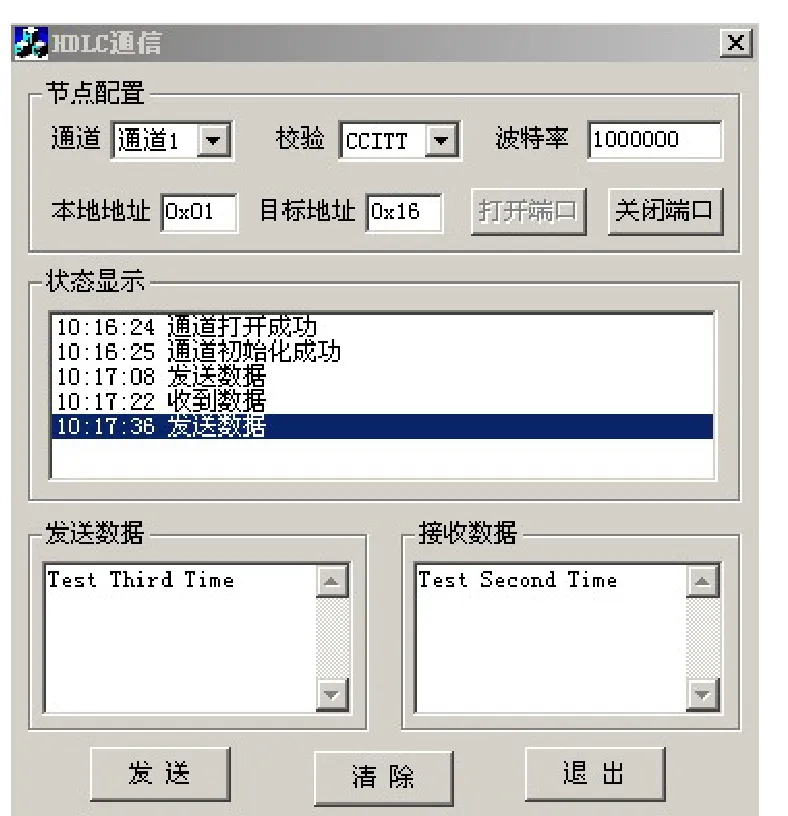

根据上述封装设计后的函数,用户可以很方便地对HDLC网络接口单元应用层的通信软件进行设计。基于上述函数设计并实现的HDLC通信测试软件运行截图,实际通信测试表明上述驱动API函数的设计和封装是可行的,如图7所示:

图7 通信测试软件运行截图

4 结论

基于上述原理设计并完成的列车通信网络接口单元,实现了HDLC协议所规定的基本通信功能。通过实验室环境下通信性能的长期运行和测试,表明该通信接口单元在各方面的性能均达到了预期的目标,这为下一步真正应用到实际列车通信网络打下了基础。

[1]叶星星.地铁列车诊断系统中央控制单元的设计与实现[D].北京:北京交通大学,2011.

[2]应三从,张行.基于FPGA的HDLC协议控制器[J].四川大学学报,2008,40(3):116-120.

[3]陈金华.基于HDLC协议的RS485通信设备的研制[J].测控技术,2010,29(6):98-101.

[4]邓凤军,张龙,王益忠.基于PCI总线的HDLC通信卡的设计与实现[J].电子技术应用,2012,38(8):30-32.

[5]罗文翰,张剑锋.基于MPC860的HDLC通道驱动程序的设计与实现[J].电子技术应用,2005,31(5):66-68.

[6]ISO/IEC 13239.Information technology-Telecommu nications and information exchange between systems-High- level data link control (HDLC)procedures[S]. Switzerland International Electro-technical Commission,2002.

[7]SAB82532 User’s Manual . Enhanced Serial Communication Controller[Z].Germany:Siemens,2007.