PEEL器件在AMIGO调频音频处理器中的应用

2013-09-04肖红宇,陈海

PLD(Programmable Logic Device)是一种可由使用者自行设置的逻辑器件,内部包含了组合逻辑电路和时序逻辑电路,使用者根据所需逻辑功能通过布尔代数法、真值表法或状态图法等来设置完成一片PLD,以实现所需组合逻辑和时序逻辑电路功能。PEEL是继通用阵列逻辑GAL(Generic Array Logic)后出现的新一代可编程逻辑器件PLD,它的密度比普通GAL大得多,在电路设计中,仅用一片PEEL就能实现数片标准TTL或CMOS器件的逻辑功能,大大减少了电路中的IC使用数量,提高了系统的可靠性,同时可使印刷电路板的面积相对的缩小,减少布线及设计时间,降低了成本,因此得到了广泛的应用。

一、 PEEL22CV10简介

1. 器件基本组成及特点

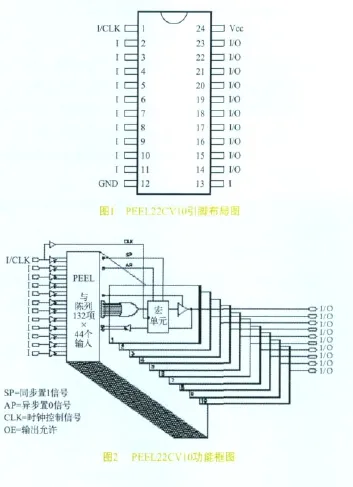

PEEL22CV10由输入缓冲器、与门阵列、或门阵列、输出逻辑宏单元、输出三态缓冲器等构成。图1为24引脚DIP封装形式的PEEL22CV10的引脚布局图,图2为PEEL22CV10的功能框图。

PEEL22CV10在逻辑结构方面具有如下特点:

(1)带有10个输出逻辑宏单元OLMC(Output Logic Macrocell),每个OLMC带有1个或门,每个或门都带有相应的乘积项数目,或门所带的乘积项为2×8,2×10,2×12,2×14,2×16,共有120项乘积项。每个宏单元有1 个触发器,每个触发器的输出都与二选一反馈多路开关相连并通过一个三态缓冲器反馈到与门阵列。

(2)可编程与门阵列共有44个输入变量,其中12个专用输入端为24个变量,10个反馈输入端为20个变量。

(3)所有的乘积项共有132项。其中或门带120项;三态输入缓冲器的使能端OE需要1个乘积项,10个宏单元共需要10个乘积项;所有宏单元中的触发器共用的一个同步置1信号SP需要1个乘积项;所有宏单元中的触发器共用的一个异步置0信号AR需要1个乘积项。

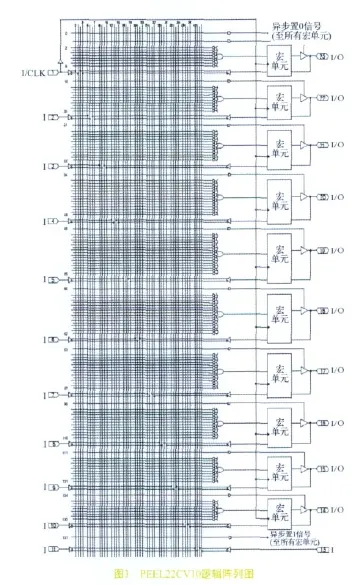

从图3可以看出,输入缓冲器的逻辑作用是把输出变量转换成原变量和反变量,为与门阵列提供输入信号。同时,由于采用CMOS工艺,使其输入阻抗很高,这样所要求的输入驱动电流就大大低于普遍双极型器件,使驱动电路可有很高的扇出系数,且电平也可同TTL电路兼容。

众所周知,所有组合逻辑都可由与一或表达式(又称为“积之和”式)来表示,在PEEL器件中,与一或门阵列所完成的就是与一或逻辑运算。与一般中小规模集成电路不同的是PEEL器件中,与门和或门的数量很大,每个OLMC的输入端又很多,且排成阵列。在PEEL22CV10中,与门的个数多达132个。又因为该器件采用与门阵列可编程,或门阵列是固定连接的逻辑结构,所以对与门阵列进行编程就可决定各个与门的输入信号,从而实现所需功能。此外,PEEL22CV10还提供了24位的电子标签和一个保密位。电子标签可存储用户定义的任何信息(如:产品制造商识别码、编程日期、线路形式识别码、产品代码等),而且这些信息不受芯片保密位的影响,随时可以读出。为了防止他人未获允许而抄袭芯片的逻辑电路设计,则可通过设置保密位来禁止对芯片作进一步编程或验证,只有对芯片整体擦除时才能将此保密位擦除掉。

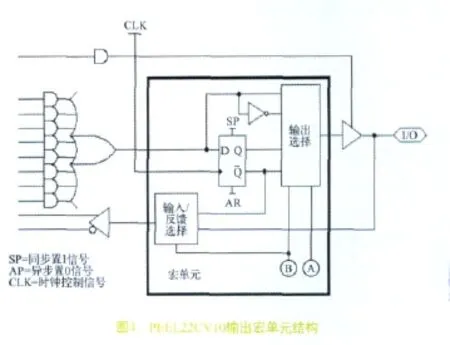

2. 输出逻辑宏单元OLMC结构

PEEL22CV10器件的输出宏单元OLMC结构如图4所示。每个0LMC包含或门阵列中一个或门,或门的每一个输入对应一个乘积项(与门阵列中一个与门的输出),或门的输出为各乘积项之和。D触发器作为状态存贮器使用,以使PEEL器件适合于时序逻辑电路。每一个0LMC包括两个实现信号选择的多路开关,其中四选一多路开关用来选择输出方式和输出极性,二选一多路开关用来选择反馈信号。这两个多路开关的控制信号是相关的,其中一个是时序/组合控制信号,另一个是输出高有效/低有效控制信号。通过编程,使每一个OLMC工作于需要的模式。输出三态缓冲器的作用有二,一是提高带负载能力,二是使电路可输出高电平、低电平和高阻态三种状态 。

二、 PEEL22CV10芯片的具体应用

AMIGO调频音频处理器是由一款具有双频带自动增益控制器、可变预加重多频带限幅器、数字合成立体声编码器、平衡阻挡带音频输入、AUX输出和BNC复合输出等功能的高性能立体声音频处理系统。它的立体声编码器部分是在08-8300-01印刷电路板上,该印刷电路板上共用到3片PEEL22CV10芯片(U7,U8,U14),分别实现如下功能:

⊙ U7产生19kHz的数字合成导频信号和立体声指示灯控制信号,并为U14提供一个同步信号,以确保所产生的19kHz的导频相位和38kHz的副载波相位的一致。

⊙ U8对3.648MHz晶体震荡器频率进行12次分频,并将产生的304kHz频率信号作为U7及U14的时钟信号。

⊙ U14为脉冲幅度调制器PAM(Pulse Amplitude Modulator),它通过控制2片双向模拟开关芯片U9及U10(CD4066)来数字合成产生一个频率为38kHz的近似正弦波作为立体声副载波。

三、结束语

必须说明的是,应用可编程逻辑器件,必须具备软件开发工具和硬件工具。对于软件开发工具常采用CUPL,ABEL,PLACE这些高级开发软件,这些软件都具有自动逻辑化简的功能,都属于编译型软件。而硬件工具则是编程器,它用来将编译产生的熔丝图文件(JED文件)固化到PLD芯片上。有关PLD器件的开发工具的使用,请参考有关资料。