基于HMC820的低相噪频率源设计*

2013-08-29刘治君李蓬蓬李柏渝孙广富

刘治君,李蓬蓬,李柏渝,孙广富

(国防科学技术大学电子科学与工程学院,湖南 长沙410073)

0 引 言

GNSS接收机本振信号和采样时钟引入的相位噪声,都会对载波跟踪环和延迟锁定环的跟踪和测距性能造成影响。对于亚纳秒级的测量,相位噪声的影响是不可忽略的[1]。要降低相位噪声对测量精度的影响,可以从射频前端和信号处理两个方面进行。文献[2]提出了利用改进卡尔曼滤波算法和多通道中相位噪声的相关性,抑制相位噪声的影响。而射频前端主要是研究低相噪的频率源。

介绍了锁相环的工作原理及相位噪声传递和Hittite公司的HMC820的特点及内部结构,设计了一个基于该芯片的低相噪锁相环电路,并针对该芯片,通过实验验证了鉴相频率和环路带宽对锁相环输出信号的相位噪声的影响。

1 锁相环工作原理及相位噪声传递

用于频率综合的锁相环的工作原理如图1所示。用于频率合成的锁相环由鉴相器、环路滤波器、VCO和N分频器组成,实际上是一个反馈环路。锁相环的输出信号的相位噪声由式(1)所示[3]:

图1 锁相环原理框图

式中:Sout(f)为输出相噪的单边带功率谱;N为分频比;H(f)为锁相环的闭环传递函数;SCU(f)为参考频标的相位噪声;SVCO(f)为VCO的相位噪声。

由式(1)可知,锁相环的输出相位噪声由参考频标、VCO和闭环传递函数,即环路滤波器共同决定。参考频标对于输出相位噪声的影响体现在两个方面,首先是参考频标的频率,对于同一个输出频率,参考频率越高,N越小,从而使式(1)中的第一项减小;另外是参考频标的相位噪声,由于H(f)呈低通特性,所以输出信号的近端相位噪声主要由参考频标和H(f)的带宽决定,远端相位噪声主要由VCO决定。

2 HMC820特点及内部结构

HMC820是Hittite推出的一款低相噪、内部集成VCO的锁相环芯片,其内部结构如图2所示。

图2 HMC820的内部结构

参考频标首先经过R分频器,然后送到鉴相器。鉴相器的输出经过电荷泵后,由管脚CP输出至外接环路滤波器,滤波后,经管脚VTUNE来控制VCO,VCO产生的信号经过一个可编程的分频器后对外输出,可以输出1 095~1 275MHz,2 190~2 550MHz和4 380~5 100MHz三个频带的信号。

HMC820有以下特点:

1)高集成度。内部集成了低相噪VCO、自校准VCO谐振系统、低相噪数字鉴相器、高精度电荷泵和三个可编程分频器。高集成度使外围电路极简单。通常,电路设计只需要考虑环路滤波器即可。

2)高鉴相频率。对于同样的RF频率,较高的鉴相频率可以减小式(1)中的N,从而降低输出信号的近端相位噪声。HMC820的最高鉴相频率可以达到100MHz,而一般的锁相环芯片的鉴相频率要小得多,如国家半导体公司的LMX2531系列的芯片,最高鉴相频率仅为32MHz.

3)高频率准确度。当芯片工作在精确模式下时,输出频率几乎可以达到零误差。

4)短的频率锁定时间。采用跳周抑制技术,大大缩减了锁定时间。

5)采用数字锁定检测技术,相对于传统的模拟检测技术,可以通过串口对芯片内部的状态进行更细致的检测。

3 电路设计

对于内部集成VCO的锁相环芯片,VCO的相噪特性不能改变,而参考频标往往由原子钟或高稳晶振提供,因此,电路设计主要考虑参考频标的频率和环路滤波器的设计。

3.1 鉴相频率选择

当目标频率一定时,鉴相频率决定了分频比N,由式(1)可知,分频比越大,近端相噪越低,同时,由于H(f)是非理想的,N也会对远端相噪产生一定影响。

3.2 环路滤波器设计

由于鉴相器、VCO和分频器都集成在芯片内部,所以环路滤波器就成了电路设计的重点。环路滤波器设计最重要的参数是环路带宽,它不仅是影响相位噪声的重要参数,还与动态范围、锁定时间等相关。其定义为开环传递函数幅度的3dB带宽。

锁相环最终输出的相位噪声可以看做是VCO的相位噪声曲线与参考频标的相位噪声曲线的组合,两条曲线的交点由环路滤波器决定。在仅考虑相位噪声的情况下,最理想的情况是环路带宽取在两条曲线的交叉点附近。对于含有除N分频器的频率合成器,还必须考虑参考信号的噪声恶化[4]。

3.3 编程

HMC820通过SPI编程控制内部寄存器及监视工作状态。

对HMC820的编程主要包括配置R-分频器、N-分频器、电荷泵和VCO子系统。R-分频器对参考频标进行分频,分频过后的信号作为鉴相频率输入到鉴相器;N-分频器的取值由目标频率与鉴相频率决定;电荷泵的设置会影响输出相噪和锁定指示;VCO子系统编程是对内部VCO调谐。

可通过读操作来读取内部寄存器状态。LD_SDO管脚是一个通用输出口,进行读操作时,输出相应的寄存器值,其他时间的输出可编程。

4 应用实例

某项目中,需要1 114MHz的本振信号,因此,选择HMC820的f0/2工作模式。

电路选用4阶无源滤波器,通过改变鉴相频率和环路参数,验证二者对以HMC820为基础的电路的输出相位噪声的影响。

测试主要从两个方面进行。首先固定环路带宽,改变鉴相频率,观察鉴相频率的影响,以验证鉴相频率的影响;其次固定鉴相频率,改变环路带宽,以验证环路带宽的影响。

测试仪器采用罗德施瓦茨的FSUP8.

保持环路带宽为190kHz不变,改变鉴相频率,得到结果如图3所示。

图3 相噪随鉴相频率的变化

由图中可以得到以下结论:

1)当鉴相频率增大时,相位噪声降低,这与理论是相符的;

2)当鉴相频率增大到一定程度后,相位噪声降低的幅度越来越小,80MHz与100MHz鉴相的输出相噪相差已经很小,这是因为式(1)取对数后,相噪随分频比按对数关系增长;

3)对于同一个环路参数,不同的鉴相频率,相噪曲线的拐点不同。

固定鉴相频率为100MHz,改变环路带宽,得到测量结果如图4所示。

图4 相噪随环路带宽的变化

由图中可以得到以下结论:

1)环路带宽对近端相噪影响较小(1Hz处的差异可认为是相噪仪的测量误差造成的);1MHz处的相噪也几乎不随环路带宽变化,这是因为远端的相噪由VCO决定;

2)而曲线拐点附近的相噪随环路带宽变化较大,这是因为|H(f)|2是非理想的,存在过渡带,在拐点附近的相位噪声由参考频标和VCO分别以|H(f)|2和|1-H(f)|2加权得到的;

3)以100MHz鉴相时,190kHz的环路带宽对应的鉴相曲线过渡比较平滑,相位噪声比较理想;

4)随着环路带宽增大,相噪曲线的拐点对应的频率变大,但与环路带宽不相等,而大约是环路带宽的1/3.同时,由图3可知,这种对应关系还与鉴相频率相关。

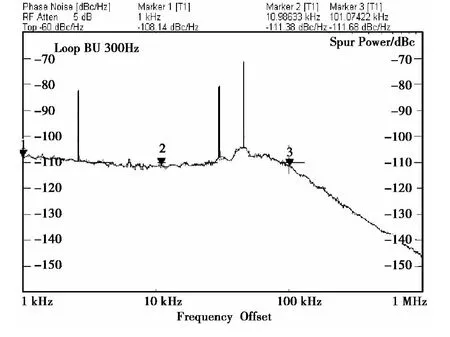

经过比较,当鉴相频率为100MHz,环路带宽为190kHz时,HMC820的输出相位噪声较好,其实测图如图5所示。

图5 1114MHz信号的相噪实测图

国家半导体公司的LMX2531系列芯片在相近频率的相噪如表1所示[5]

表1 LMX2531的相位噪声

与之相比,HMC820的相位噪声降低了10dB以上,证明了HMC820在相位噪声指标上的优越性。

5 结 论

介绍了锁相环的工作原理及相位噪声的传递过程,以HMC820为基础,搭建了锁相环电路,分析了鉴相频率和环路带宽对HMC820的锁相环电路的影响,得到了一些有工程意义的结论,并给出了较优的鉴相频率和环路带宽设置。实测结果表明:与同类芯片相比,HMC820在相位噪声指标上确实有较大优势。

[1]朱祥维.卫星导航系统时间同步关键技术研究[D].长沙:国防科技大学,2007.

[2]王江安,庄奕琪,周清军,等.利用改进卡尔曼滤波算法抑制GPS接收机相位噪声[J].数据采集与处理,2010,25(5):611-614.

[3]REBEYROL E,MACABIAU C,JULIEN O.Signal distortions at GNSS payload level[J].ION GNSS ITM,2006:26-29.

[4]王兴春,刘 亮.低相位噪声参考信号发生器的设计[J].应用天地,2007,26(11):74-77.

[5]李彩华,李柏渝.LMX2531在信号源射频电路设计中的应用[J].微处理机,2008(4):2-3.