RFID系统中的CRC算法的研究与设计

2013-08-28陈燕,郭锋

陈 燕,郭 锋

(郑州轻工业学院计算机与通信工程学院,河南郑州450002)

射频识别(Radio Frequency IDentification,RFID)技术是一种非接触式的自动识别技术,具有数据量大、保密性好、抗干扰能力强等优点,被广泛应用于物流管理、高速公路的收费、图书馆自助借阅系统、电子门票等领域[1-3].RFID 系统中阅读器的设计方案有多种,FPGA以其高集成度、高可靠性、设计周期短等优点成为设计方案的一种.尤其在超高频环境中,数据传输的速率高达几十kbps,高速的FPGA器件可利用其流水线技术,完成阅读器基带信号编码、解码、校验等的处理.

在RFID系统中数据的传输不可避免地会产生差错,而循环冗余校验(Cyclic Redundancy Check,CRC)是一种检错率高、编码简单的检错方法,故在RFID系统中数据传输常采用CRC.RFID系统中,CRC的计算作用于SOF后的所有字节,并将计算得到的CRC附加在每一帧内EOF前的两字节上用于每一次请求和应答.当收到来自阅读器的请求时,电子标签将校对CRC的值是否有效.如果无效,电子标签将丢掉该帧,并不做回答(调制).

CRC在FPGA上的实现,可采用串行和并行两种实现方式[4-6].采用串行方式时,编码按位逐位输入线性反馈移位寄存器组(LSFR)中,当所有位输入完后触发器的状态就是所输入编码的CRC的校验码.采用串行方式电路结构简单,但每次只能处理一位二进制数据,也很难满足速度较高的场合.而当数据传输的速度很高,或者是多位数据并行传输时,需要引入并行计算的实现方法.并行计算的实现方法可以在同一个时钟内对多位数据进行编码,从而提高CRC的计算速度.

1 RFID系统中的循环冗余校验

假设要传送 k 位二进制数据,即 dk-1,dk-2,…,d1,d0,则k位二进制数据序列可表示为:

式中:G(x)为生成多项式;余数R(x)为所求的r位校验位.发送端将r位校验码附加在传输的数据流后边构成一个新的二进制码序列(共k+r位),然后将其发送出去.在接收端也进行同样的除法过程,如果接收端的除法结果不为零,则表明数据传输产生了差错,数据接收端自动请求重发,实现纠错.

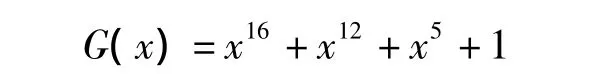

在RFID 系统中,ISO/IEC 14443,ISO/IEC 15693,ISO/IEC 18000—6中长命令多采用CRC-CCITT国际标准,其生成多项式为G(x)=x16+x12+x5+1.ISO/IEC 18000—6中,短命令采用CRC—5,其生成多项式为G(x)=x5+x3+1.

2 多字节的并行CRC算法

2.1 单字节的CRC并行算法

以CRC-CCITT国际标准生成的多项式

为例,通用的CRC串行编码器采用LSFR,其串行编码器如图1所示.

图1 CRC串行编码器

编码前先将所有的寄存器置0,之后将信息序列从高位到低位依次从input端输入.信息序列全部输入后,寄存器中的值就是所要求的余数,即CRC的校验码.串行的方法虽然可以计算各种CRC,但是一个时钟周期只能计算一位数据,效率比较低,只适用于低速的串行输入输出系统.如果可以在同一个时钟周期内并行处理若干位数据,便可以大大地提高速度,因此在串行处理的基础上推导出了并行算法.

先输入高位,再输入低位,当经过8个时钟信号,即一个字节(d7d6d5d4d3d2d1d0)的所有信息位都输入后,寄存器的输出即为该字节的CRC校验码.寄存器的输出结果如下:

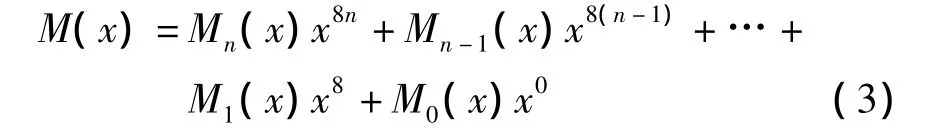

2.2 n个字节的CRC的并行算法

n个字节的二进制数据序列可表示为:

其中:

式中:G(x)为生成多项式;Rn,H(x)为Rn(x)的高8位;Rn,L(x)为 Rn(x)的低 8 位.

由式(4)知,对于CRC-16,本字节的CRC的校验码=(上一字节的CRC校验码的高8位+本字节)的CRC校验码xor(上一字节的CRC校验码左移8位).

3 基于FPGA的CRC校验码的实现

3.1 关键代码

下面是用VHDL代码实现循环冗余校验的主要源程序.

3.2 运行结果及性能分析

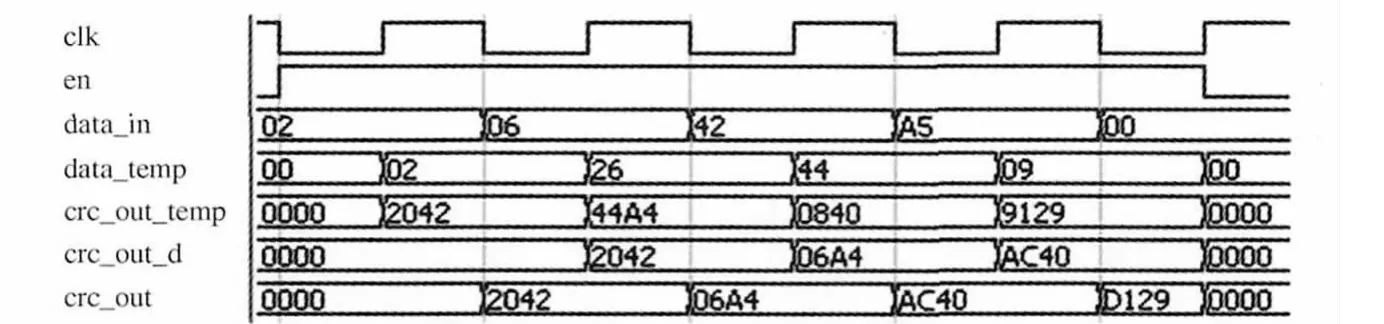

选用的FPGA芯片是Altera公司开发的Cyclone系列的FLEX10K10LC84-3,输入端输入数据流为(02,06,42,A5),高位在前,低位在后.采用图1串行编码器和笔者提出的算法(初始值取00H)分别在modelsim SE 6.5中进行仿真,波形分别如图2和图3所示.

图3 多字节的并行算法运行结果

从图2和图3可以看出:计算结果都为D129,与式(2)的理论结果一致,符合CRC算法规则;在接收完最后一个数据A5后,多字节的并行算法在延时1个clk就计算出了所输入字节的CRC,运算速度较快.虽然该并行算法使用了38个逻辑单元,比只使用了16个逻辑单元的串行方式多用了一倍的资源,但求解速度却提高了很多,较好地做到速度与资源的平衡.采用更高端的FPGA芯片,速度更高,完全可以满足超高频和微波段的CRC计算.

4 结语

CRC是数据通信中应用广泛的差错控制算法,检错能力强,占用系统资源少,是RFID系统中重要的错误检测和恢复机制.通过对CRC原理的分析,研究了一种可求解多字节的并行CRC算法,并采用VHDL设计实现.该算法首先通过分析经过8个时钟信号后线性反馈移位寄存器的输出状态与输入的字节、寄存器的初始状态的关系,从而得到单字节的并行CRC算法;然后通过计算CRC的公式推导出当前字节的CRC与当前字节、上一字节的CRC的关系,从而得到多字节的并行CRC算法.仿真实验证明了该算法的正确性和高效性,提高了RFID系统的编解码速度.

[1]单承赣,单玉峰,姚磊,等.射频识别(RFID)原理与应用[M].北京:电子工业出版社,2008.

[2]汪浩.物联网的触点——RFID技术及专利的案例应用[M].北京:科学出版社,2010.

[3]蔡孟欣.图书馆RFID研究[M].北京:国家图书馆出版社,2010.

[4]莫元劲,黄水永.并行CRC在FPGA上的实现[J].电子设计工程,2011,19(15):133 -135.

[5]罗志聪,孙奇燕.CRC-16算法与FPGA实现[J].四川兵工学报,2010,31(5):89 -92.

[6]范文兵,李建华,禹士鹏,等.RFID系统数据传输中CRC算法的分析与实现[J].郑州大学学报:工学版,2010,31(2):97 -101.