用FPGA实现LED大屏幕的扫描

2013-08-16郑宝华韩桂杰孙万懿

郑宝华 韩桂杰 孙万懿

(1.吉林化工学院,吉林 吉林132022;2.吉林信息工程学校,吉林 吉林132022)

0 引言

LED 大屏幕是由许多相互独立的发光二极管排列而成的,由于发光管的离散性,决定了其发光控制和驱动只能以数字方式进行[1]。大屏幕的显示控制方式可以静态驱动也可以动态扫描驱动。相比较而言,动态扫描驱动方式可以节省大量的硬件成本,所以,一般情况下均采用动态扫描驱动方式。为了能显示稳定的图像,对扫描电路的速度要求很高,特别是实现灰度控制时,要求就更高了。所以,精心地设计扫描电路是提高图像稳定性的关键。

本文给出了以FPGA 器件为核心的大屏幕动态扫描电路,其数据点时钟可达20MHz 。提高了图像的稳定性,并且使每个扫描单元可控制较大面积的屏体。

1 屏体显示电路

屏体显示电路俗称 “灯板”,最常用的是采用8*8 LED 点矩阵构成。这就决定了扫描行周期只能为8 的整数倍,基于亮度和硬件成本的综合考虑,一般采用16 行为一扫描周期[2]。发光器件选用D05881 行共阳点矩阵构成,扫描单元的每行二极管共阳连接,由扫描电路输出的行地址经4:16 译码控制。由于扫描单元的每行二极管共阳连接电流比较大,如果用单只大功率管子驱动,会使局部电流很大而增加制版的难度。这里采用多支小功率P946 并联驱动,由于P946 在物理上是分开的,这样可使大电流分散,并且不增加硬件成本。

行数据由扫描控制电路从显示存储器中读出,串行输出到灯板,当每行数据串行发送完之后输出锁存信号和行地址信号。电路如图1所示。

2 扫描电路及动态扫描的实现

2.1 动态扫描电路结构

动态扫描电路包括显示存储器和扫描电路,动态扫描由FPGA 器件来控制实现,显示存储器由双端口静态存储器构成(图2)。FPGA 要按时序形成对双端口显示存储器读操作,其中包括地址信号(add_1)和读(rd)信号,读入数据后要进行并/串转换后输出到显示电路。同时,为完成扫描显示扫描电路要按时序形成数据移位时钟信号(clk_1)、锁存信号(suocun)、行地址信号(add_2),这是动态扫描实现的。

传统的扫描控制多由单片机构成,笔者曾用12 片华邦的78E58(24MHz)单片机实现9 平方米大屏幕的扫描,虽然精心设计了指令代码,但在扫描速度上还是捉襟见肘。采用FPGA 实现扫描则很容易实现数据点时钟20MHz 或更高,并且在一片器件上可实现多路数据输出,实现并行多路扫描,很好地改善了单片机扫描速度慢的问题,提高了显示图像的稳定度。

2.2 用FPGA 实现动态扫描

FPGA 的设计方法与传统的数字逻辑设计方法不同,是采用自上而下的设计流程。同时,在设计过程中可通过仿真手段验证电路功能的正确性[3]。采用VHDL 等硬件描述语言的输入方法设计,使系统的实现过程更为灵活。

本系统以16*32 点阵单元为例进行设计并测试。顶层原理图文件由两个模块构成(图3)。其中,74165 模块调用了max2libmf 库中的74165 模块,完成数据的并/串转换。READ_1 模块完成读显示存储器、 控制扫描输出等功能。READ_1 模 块 由VHDL 编 程[4],实 现 将数据在时钟控制下串行发送到屏体,当一行数据发送完成之后输出锁存(suocun)脉冲,之后输出扫描地址(add_2),完成一行扫描,扫描以16 行为一扫描周期。

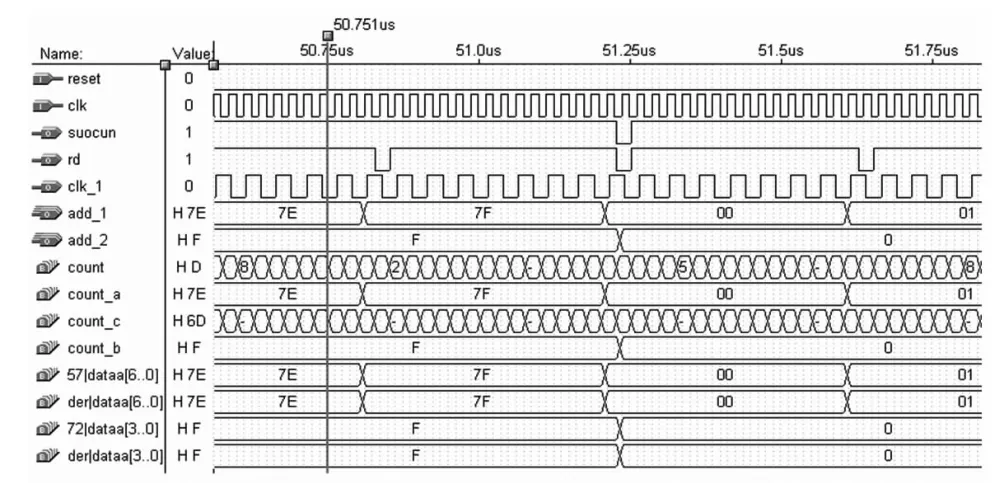

2.3 动态扫描的仿真

图4 给出了扫描控制模块READ_1 的仿真波形,reset 复位后进入扫描,clk 是模块的工作时钟,2 分频后的clk_1 为点数据输出时钟,当读出的一个字节数据发送完成后显示存储器地址(add_1)增量,并输出读信号rd 读取下一个字节数据。当一行数据串行发送完成后输出suocun 信号,将一行数据并行输出,完成一行的扫描,同时地址(add_2)也要增量。当扫描地址增加到第16 行(地址add_2 为F)后一个扫描周期完成,下一个周期返回到第1 行(地址add_2 为0)继续扫描,如图4 上51.25us 处所示。

3 结束语

本文给定的扫描电路点时钟clk_1 为20MHz,它是普通单片机串行时钟的20 倍。并且在同一芯片上可实现多路串行输出。这样,一片FPGA 可控制较大面积的屏体。通过实验,扫描图像非常稳定,充分体现了FPGA 器件应用在高速、复杂数字系统中的优势。

[1]刘泽民.大屏幕视频真彩色显示技术[J].电子技术,1997(4):19-21.

[2]张艺.LED 智能显示屏驱动显示电路电子技术[J].1994,4.

[3]侯伯亨,股新.VHDL 硬件描述语言与数字逻辑电路设计[M].西安电子科技大学出版社,2000.

[4]甘历.北京VHDL 应用与开发实践[M].出版社,2000.