ATCA架构中多网口后板的高效设计

2013-08-13王江

王 江

(上海贝尔股份有限公司 P&RD,上海 200125)

先进的电信计算平台ATCA(Advanced Telecom Computing Architecture)是国际工业计算机制造者联合会PICMG(PCI Industrial Computer Manufacturer's Group)标准历史上最重大的革新。它的设计初衷是针对电信运营级应用,为下一代通信及数据网络应用提供一个高性价比、模块化、兼容性强、扩展性好的硬件构架,为新一代电信运营设备提供一个“可靠、可用、适用”的解决方案。

ATCA不仅能因其总线的开放性而降低电信设备总体部署成本,而且最大限度地提升了不同厂商产品之间的兼容性。ATCA设备在降低网络建设和维护成本的同时,还可以通过更换板卡快速支持新应用和新业务,灵活性更强。由于这些优点,ATCA架构不仅在电信运营领域得到了广泛应用,也逐渐在仪器仪表、军事和航空航天等领域受到关注。

1 多网口后板的设计所面临的问题

符合ATCA标准的系统由一个或多个热插拔线卡(即模块)组成,这些线卡也称为现场可替换单元FRU(Field Replacable Unit)。在基于ATCA的网络设备中,为了提供数量多且性能高的网络接口,往往在前板安装先进的网络处理器NPU(Network Process Unit)或CPU,而在同槽位的后板(RTM)上布置多个网络接口连接器(如RJ45或者SFP插槽),用于连接外部网线或光纤。

RJ45接口最高支持1 000 Mb/s的以太网速率,接口电缆是铜电缆,不适应电信设备“光进铜退”的发展趋势。而 SFP(Small Form-factor Pluggable transceiver)插槽由于既能容纳RJ45接口的电模块(Copper SFP),也能容纳FiberJack接口的光模块(Fiber SFP),灵活性好,速率可达10 Gb/s,因此越来越得到设计师的青睐。但是如何管理这些SFP模块,对设计师而言,在硬件和软件方面,面临如下问题:

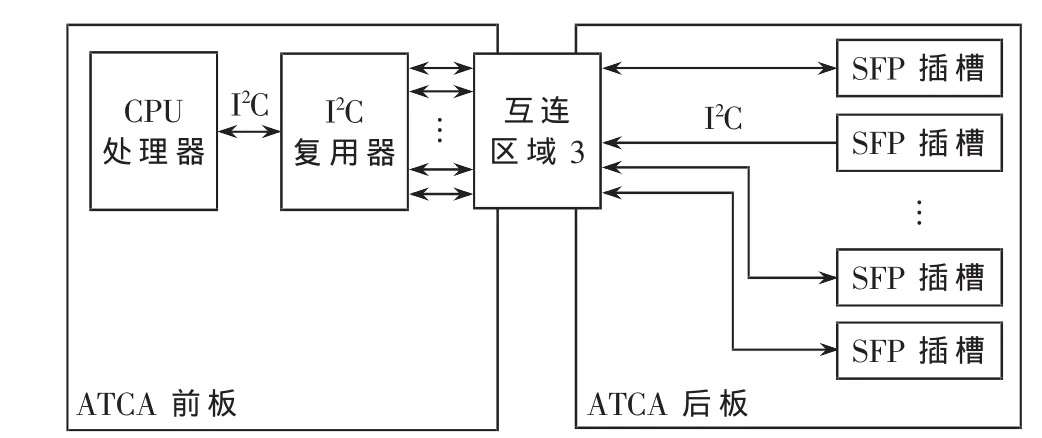

(1)硬件方面:因为 ATCA标准[1]规定,前板通往后板和背板的连接器分为 3个区域:区域 1、区域 2和区域3。其中,区域1用于电源和管理信号,连接到背板;区域2负责前板之间的数据通路,也连接到后板;区域3用于前后板的连接,信号自定义,而前后板的连接无需经过背板,采用共面互连技术。区域3最多允许安放3个高速连接器,因为前后板之间的连接信号数量有限,所以在利用这些互联信号时需要精打细算。互连信号越少,就越能节省昂贵的高速连接器,降低产品成本。按照SFP标准[2],每个SFP模块都提供了一个符合I2C标准的管理接口,通过I2C接口,系统可以获得模块的型号、参数和工作状态等信息。

图1 多网口后板的管理通道设计

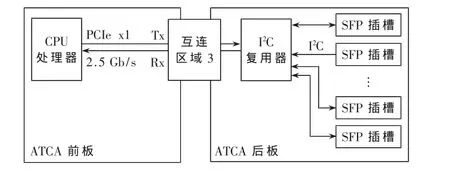

图2 优化的后板管理设计

如果把每个模块的I2C接口总线都连接到如图1所示的前板,则会造成浪费。因为一个I2C接口需要占用2个互连引脚,I2C占用的互连引脚越多,留给其他模块的互连引脚就越少,而实际上有相当多的互连引脚被用于传输以太网的收发信号,才能保证足够的数据通路带宽。

另外,所有同类型SFP模块的I2C接口的器件地址都是相同的,而I2C标准[3]规定每条I2C总线上不能存在两个相同的器件地址,所以当它们与CPU相连时,必须经过I2C复用器(因为处理器通常没有足够的I2C总线接口)。I2C复用器可以采用专用的芯片实现(如PHILIPS公司的PCA9548A,支持将一个I2C接口扩展为8个I2C接口),也可以用CPLD或者FPGA实现。

(2)软件方面:I2C是一种低速串行总线,频率一般为100 kHz或 400 kHz。以 100 kHz为例,如果不考虑器件的响应时间,读取一个字节大约耗费40个I2C时钟周期(约0.4 ms)。因为处理器和I2C复用器之间只有一个I2C接口相连,处理器不得不通过逐个轮询的方式去查询各个SFP模块的状态变化,占用了大量的CPU资源;如果用中断方式,SFP模块标准中又没有定义模块的中断引脚,硬件架构上不提供支持。所以,如何有效管理各个SFP模块而又尽可能低地耗费CPU指令是软硬件设计面对的一大难题。对以上问题,本文提出下面的优化解决方案。

2 优化的解决方案

为了解决硬件和软件面临的设计难题,本文从硬件架构入手,借助于CPLD或FPGA芯片,辅以高效的软件设计,开发出了一套行之有效的解决方案。

2.1 硬件设计

为了减少I2C接口所占用的前后板互连引脚数目,本文将执行I2C复用功能的芯片放到了后板上,这样只有一条I2C总线通过互连区域3(即只占用2根互连引脚),极大地节省了互连引脚的数目。另一方面,I2C复用器不采用商业专用芯片,而是采用CPLD或者FPGA,可为软件设计提供较佳的灵活性 (如提供中断机制)。在本设计中,采用了FPGA。

假设后板上安放了8个SFP插槽,与优化前的设计相比,优化后的设计节省了14个互连引脚。为了进一步提升处理器访问后板SFP模块的速率,本文用PCIe总线取代I2C总线,如图2所示。连接FPGA和处理器,PCIe总线占用4根互连引脚,虽然比I2C总线多占2个引脚,但是速率提升到了 2.5 Gb/s,远高于 I2C的速率,使处理器和I2C复用器之间的速率瓶颈问题得以解决。选择PCIe的另一个好处是:如果采用中断方式,则PCIe不需要专用的中断引脚,因为它是依赖带内消息中断的。此外,连接FPGA和8个SFP插槽的8组I2C总线互相独立,所以FPGA可以并行地访问8个SFP模块,比串行访问的效率提升了8倍。

2.2 软件设计

如何处理高速处理器与低速外围总线之间的关系,是软件设计的主要任务。处理器的速度一般在几百到上千兆赫兹,而I2C总线的速度一般最高为400 kHz(普通的只有100 kHz),两者完全不在一个数量级上。所以,FPGA不但要承担扩展I2C总线的任务,而且要承担管理低速总线设备的任务,使处理器有更多的时间处理计算量大、优先级高的任务。因此,软件设计的主要工作在FPGA上。

FPGA中集成了2个成熟的IP核:一个是PCIe内核,工作于从设备(End Point)模式,1路通道(x1 Lane);另一个是 I2C内核,工作于主设备(Master)模式,各条总线互相独立。FPGA软件的设计需要考虑两方面的因素:一是高效,尽可能降低CPU的负担;二是支持热插拔,因为SFP模块随时都可能被插入或拔出,导致I2C总线上正在运行的协议随时会被中断而产生异常。

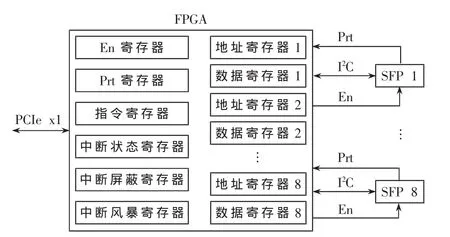

FPGA中的寄存器设计以及与SFP模块之间的控制连线如图3所示。根据SFP标准[2],每个模块会引出一个存在(Prt)信号和一个使能(En)信号,FPGA中的使能(En)寄存器通过使能信号控制每个模块是否工作。存在(Prt)寄存器通过读取存在信号反映每个 SFP插槽中是否插入了SFP模块。重启寄存器用于重启各条I2C总线,特别是当I2C协议正在总线上运行时,模块被突然拔出,I2C总线因为缺少客户端的响应而产生异常,此时会在中断状态寄存器反映异常情况,并且自动重启I2C总线,以便下次模块插入时可以正常工作。CPU也可以主动设置指令寄存器来重启某条I2C总线。

图3 FPGA管理SFP模块框图

地址寄存器和数据寄存器成对出现,每一对寄存器对应一条I2C总线。当处理器需要读取SFP模块内的一个寄存器时,可以将寄存器地址设置到地址寄存器,再设置指令寄存器为读操作。如果操作正常,则操作完成后,FPGA会把读取的数据存放在对应的数据寄存器中;如果操作出现异常,则FPGA会设置中断状态寄存器的相关比特位反映异常情况;当处理器需要写SFP模块内的一个寄存器时,先把待写数据写入数据寄存器,并将寄存器地址写入地址寄存器,再设置指令寄存器为写操作。如果写操作异常,FPGA也会设置中断状态寄存器的相关比特位反映异常情况。

中断状态寄存器反映了每条I2C总线的工作状态以及模块本身的状态,例如:I2C总线工作是否正常、读写操作是否成功完成、模块被拔出或者插入等。中断屏蔽寄存器定义了各个状态变化是否要触发中断上报机制。

指令寄存器在不同比特位针对每条I2C总线设置了读、写、轮询和重启4种指令(读写和重启指令在前文中已有描述)。轮询指令是指:如果SFP模块存在且使能,则FPGA会不停地读取SFP模块中的寄存器(寄存器地址由地址寄存器指定),并将读回的数据存放在数据寄存器中,供处理器随时调用;同时可以设置中断,如果本次读的数值不同于上次读的数值,则产生中断并通知处理器。轮询功能为系统软件监测后板对外的以太网接口的链路状态提供了强大的支持。因为在系统运行过程中,以太网链路可能被断开或连接,链接状态随时可能变化。例如,速率从百兆变为十兆,或从千兆变为百兆;模式从全双工变为半双工。

许多SFP模块的链路状态可以从其中的一个物理层状态寄存器获得。假设处理器通过直接轮询这个寄存器来获得链路信息。如果I2C工作频率为100 kHz,则读取一个寄存器耗时约0.4 ms(8个SFP模块共耗费约3.2 ms);在一个主频为1 GHz的处理器中,轮询一次占用的CPU资源高达3 200 000个CPU时钟周期,处理器为了及时获得模块和链路状态,不得不频繁地(如每隔0.1 s)去轮询一次,明显降低了处理器的工作效率。然而,模块和链路状态不是一直在变化的,可能数小时或者几周有一次变化,但是处理器如果不能及时捕获这一次变化,就可能给系统运行造成致命的后果。例如链路断开了没有及时发现,仍然误认为连接,将导致实际业务的中断。而为了偶然出现的一次状态变化,而频繁地去轮询查看低速设备的状态,耗费大量的CPU资源是不值得的。

因此,在新的软件设计中,由FPGA接管处理器的轮询任务,以中断方式上报给处理器,使处理器只要在系统初始化时去获得SFP模块和链路状态,运行过程中几乎不需要在I2C总线上浪费任何CPU资源。

另外,对某些中断类型,例如模块的插拔、链路状态等,FPGA设计了防止“中断风暴”的功能。“中断风暴”是指短时间内有大量的中断产生,直接影响处理器的效率甚至业务。例如有时SFP模块或网线没有插紧或者对端设备的网线虚插,可能引发状态的频率变化,触发大量中断产生。

因为在系统软件中,中断的优先级大于任何线程或任务,当中断过多时,处理器就忙于处理中断而无暇顾及正常的数据处理和业务。而FPGA会根据“中断风暴寄存器”规定的时间间隔,统计相同类型的中断数量,上报第一个发生的中断和最后一个发生的中断,隐瞒中间过程产生的中断,从而提高了处理器效率。时间间隔的设置需要根据应用仔细权衡,一般设置为50 ms左右。此外,运行在处理器上的软件发现某类中断频繁上报时,还可以通过设置中断屏蔽寄存器禁止这类中断,并输出消息提醒用户。

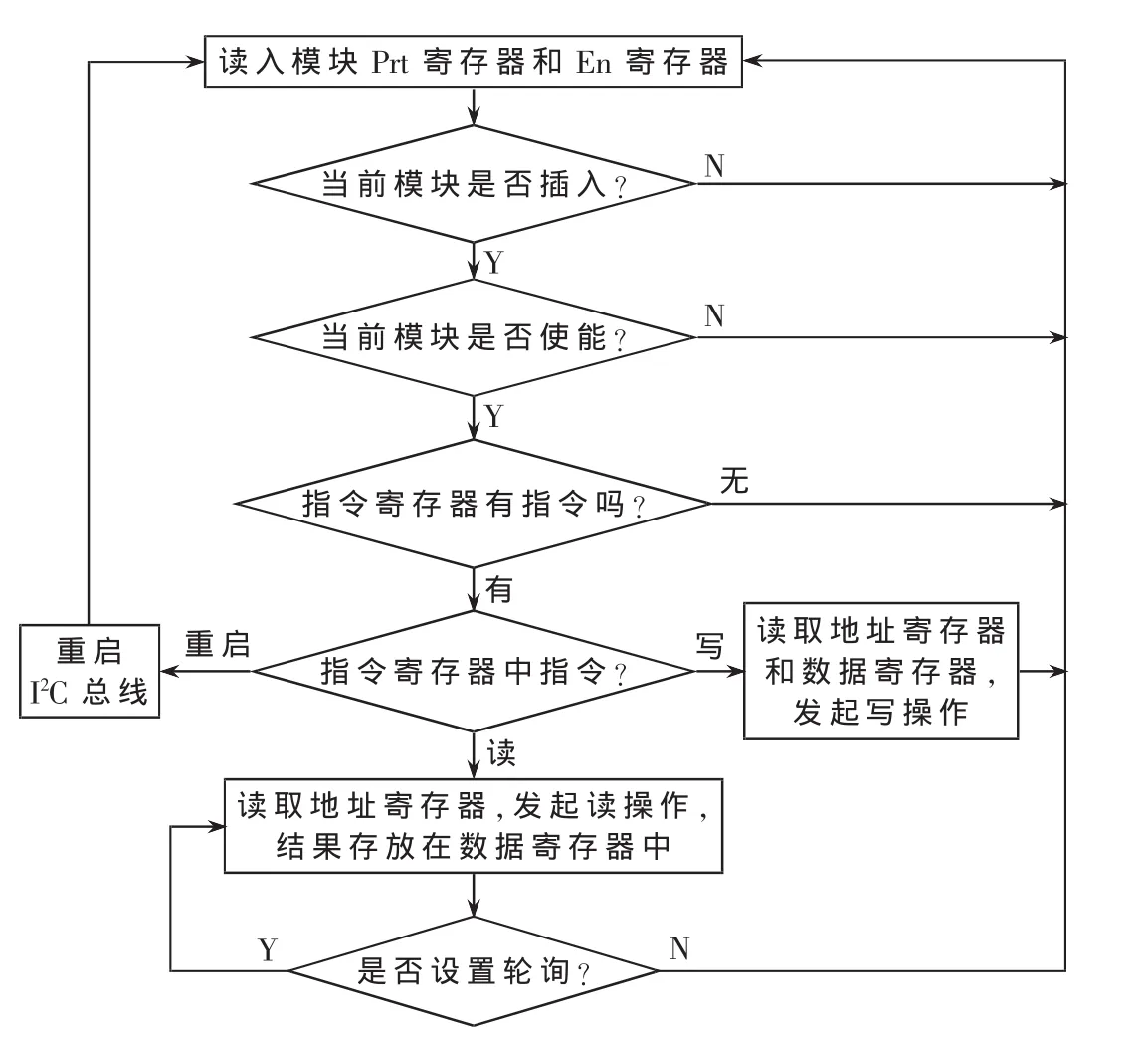

图4是针对一个SFP模块的FPGA的软件流程。首先,FPGA读入模块的存在寄存器和使能寄存器,然后判断模块是否存在和使能,如果模块不存在或者不使能则跳过;否则,根据指令寄存器中的指令进行相关操作。如果没有设置指令,则跳过;如果是写指令,则根据地址寄存器和数据寄存器的值进行写操作;如果是读指令,则根据地址寄存器中的数值进行读操作,并将读取的数值存放在数据寄存器中;如果设置了轮询,则不断地读取设定的寄存器,更新数据寄存器中的数值。每种操作完成后都会调用中断子程序,例如读取存在寄存器后,FPGA会把当前数值和前一次的值进行比较,如果不同,则根据中断屏蔽寄存器的设置触发中断;轮询操作时数据寄存器的数值发生更新也可触发中断。

图4 FPGA软件流程图

本设计采用软、硬件相结合(包括SFP模块频繁插拔、链路状态频繁变化等),经过长时间连续集成测试,同时观察CPU的利用率,后板模块管理任务所占的CPU利用率始终低于0.1%,而且处理器没有漏过任何一次模块和链路的状态变化。测试证明,优化后的设计不但可以长时间可靠工作,而且大幅度降低了处理器在管理多网口后板上的指令开销,提高了处理器的利用率。本文介绍的优化后的后板的软、硬件设计架构不但适合于ATCA标准的后板,也可以应用到CompactPCI标准和其他自定义后板的设计中。

[1]PICMG.PICMG R3.0 advancedTCA base specification[Z].2008.

[2]SFF Committee.SFF-8472 specification for diagnostic monitoring interface for optical transceivers[EB/OL]Rev 11,2010.9,ftp://ftp.seagate.com/sff/SFF-8472.PDF.

[3]PHILIPS.The I2C-bus specification version 2.1[Z].2000.