基于DSP+FPGA的Camera Link接口相机的图像处理平台设计

2013-08-13张向阳程勇策曲思潼

张向阳,程勇策,曲思潼

(中国电子科技集团公司第三研究所,北京 100015)

责任编辑:任健男

光电传感器发展至今,标准全电视信号的传感器技术成熟稳定,广泛应用在各个领域,随着光电传感器技术的发展,基于Camera Link接口的高帧频数字相机的出现,它提高了成像能力,提升了传输带宽,但是也存在一些工程应用上的问题,一是基于Camera Link接口的各种相机都不能直接显示,只能通过PC机配备专用的采集卡在屏幕上显示,这样的架构不能满足特定应用的要求;二是传输距离短,有效传输距离在10 m以内。

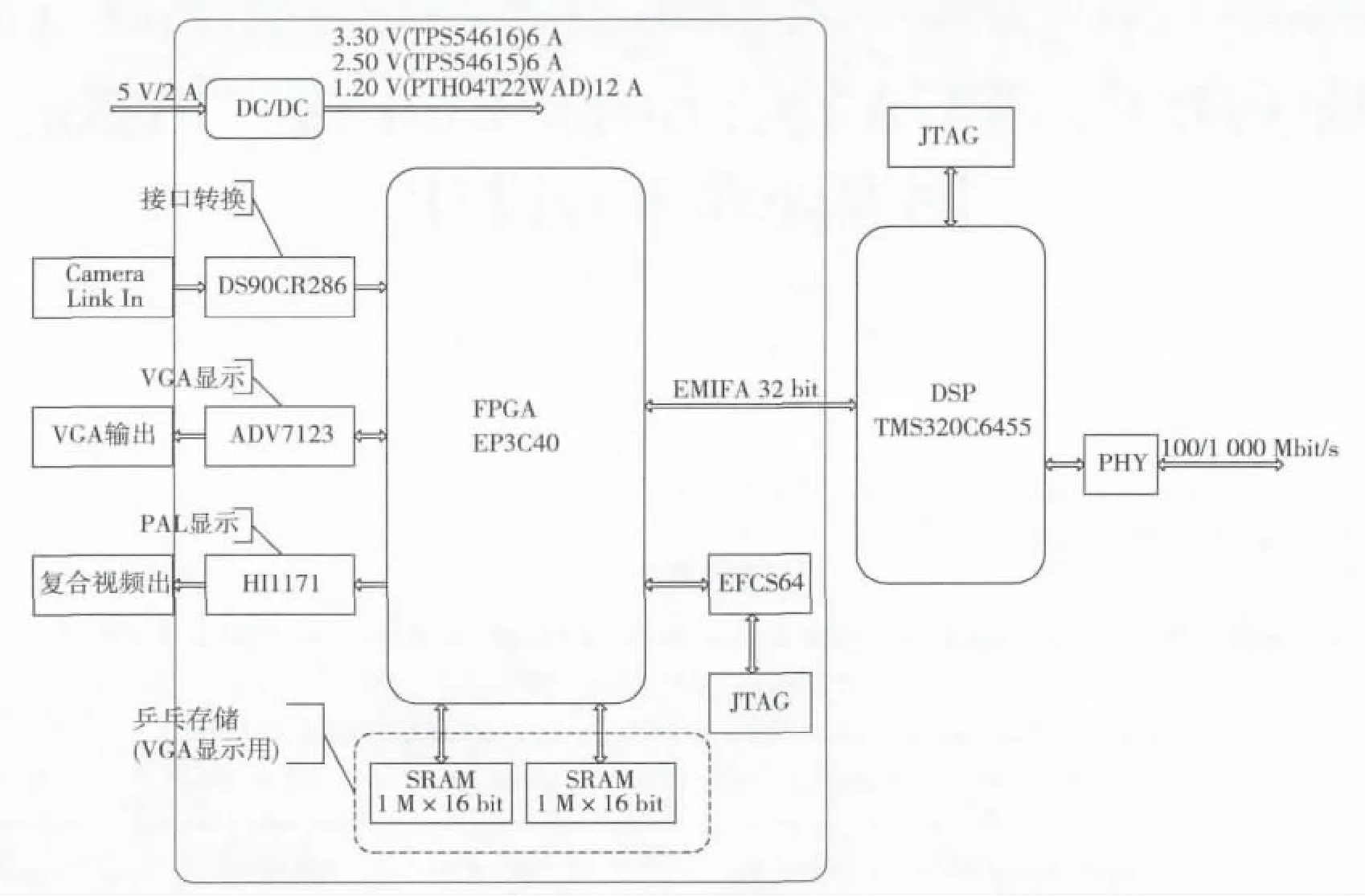

本系统设计采用基于DSP+FPGA的图像处理平台代替PC机,完成对基于Camera Link接口的高帧频数字相机的图像信号进行实时的采集、VGA和PAL制式的显示、信号处理等功能,并对 DSP[1-2]处理后图像数据利用千兆以太网向上位机传输,实现降低硬件成本,提高系统集成能力,满足对实时性和可靠性要求比较高的应用需求。

1 系统架构

系统以FPGA为中心,实现对相机的Camera Link接口的数据采集,并将数据实时通过VGA和PAL显示。同时像机数据又送入DSP进行图像处理后,通过千兆网络发送到计算机终端。系统架构如图1所示。

1.1 Camera Link 接口和相机

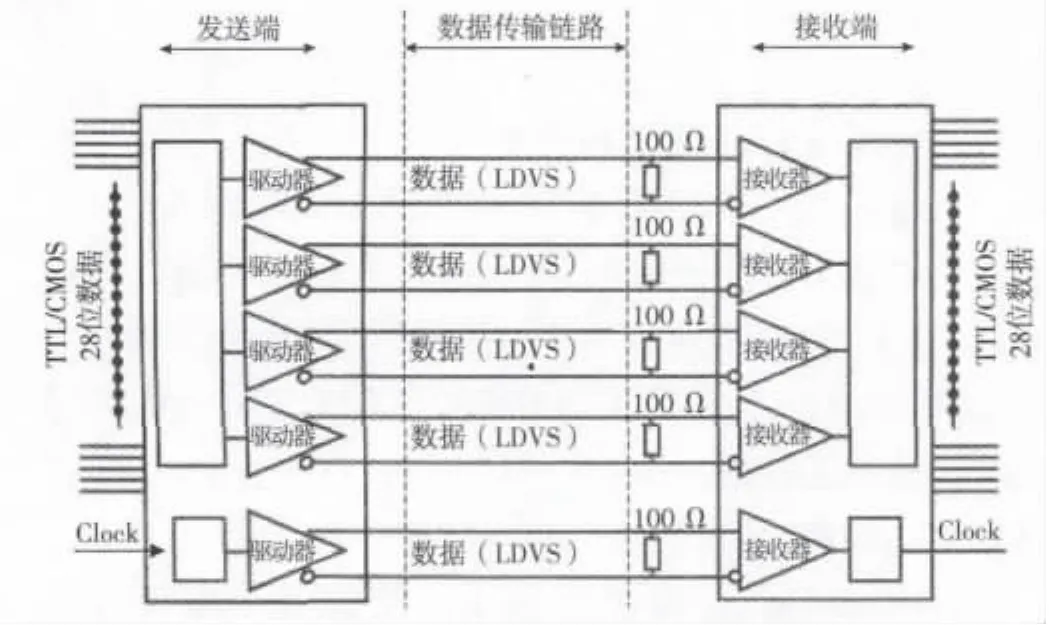

Camera Link标准是在NS提出的Channel Link技术标准的基础上发展而来的,该接口具有开放式的接口协议,使得不同厂家既能保持产品的差异性,又能互相兼容。它在传统LVDS传输数据的基础上又加载了并转串发送器和串转并接收器,利用SER/DES(串行化/解串行化)技术以更高的速度发送数据。

Camera Link标准使用每条链路需要2根导线的LVDS传输技术。驱动器接收28个单端TTL/COMS数据信号和1个时钟信号,28个数据信号以7∶1的比例被串行发送,也就是5对LVDS信号通道上分别传输4组LVDS数据流和1组LVDS时钟信号,即完成28位数据的同步传输只需要5对线,如图2所示。

本文以美国UNIQ公司生产的UP685相机为基础机型,针对定制的UP685CL相机进行Camera Link图像采集、处理、显示等功能设计。该相机的特性为:传感器1/2”逐行扫描的CCD,有效像素659(H)×494(V),像元大小9.9 μm,像素时钟固定为 40 MHz,帧频固定为 100 Hz,曝光时间1/62 000~1/100 s,支持外部电平触发或软件触发,镜头接口C,供电电压12 V,最大功耗6 W,数字视频输出格式采用CameraLink base格式[3]。

图1 硬件平台模块框图

图2 CameraLink接口发送、接收的原理框图

1.2 FPGA

根据本系统的运算性能和外设I/O的需求,选用CycloneIII系列的EP3C40F484C8芯片,它具有39 600个逻辑单元、2 340 kbit存储单元,126 个乘法器、4 个 PLL,331 个外部独立I/O,最高运行时钟高达300 MHz,串行配置芯片存储器选用EPCS64,2片IS61WV102416存储器芯片SRAM 1 M×16 bit。由于输入的数据量大、速率快,因此系统采用乒乓缓存机制,作为VGA显示用的视频数据缓存。

1.3 DSP

DSP采用TI公司的高速处理芯片TMS320C6455,主频达到了1 GHz,1 ns的指令周期。每周期执行8条32位指令,最大峰值速度达到8 000 MIntruction/s(兆指令/s)。TMS320CC6455[4]片内是基于C64xx内核的L1/L2存储结构,片上集成有大量的存储空间。L1P为32 kbyte,L1D为32 kbyte,L2为2 Mbyte,比此前C64x存储器的容量翻一番,其中L1P和L2都可直接映射到存储空间。

TMS320C6455带有的DDRII SDRAM存储器接口,可以实现与32位存储器件的无缝连接,板载DDR2 32 M×32 bit。TMS320C6455带有一个10/100/1 000 Mbit/s以太网媒体访问控制器(EMAC),一个无缝外部存储器接口(64 bit EMIFA)支持128 M×8 bit NOR Flash。DSP与FPGA采用EMIF和Mcbps连接,EMIF支持16 bit,32 bit,64 bit宽度,速度 100 MHz。

2 FPGA的实现

2.1 接口设计

2.1.1 转换电路

对于接收到的LVDS串行数据,需要转换成并行数据流,利用Camera Link接收器接收LVDS数据流并将其解串成CMOS/TTL数据。采用美国NS公司的Channel Link芯片DS90CR286A作为Camera Link接收器,Camera Link接口相机硬件连接如图3所示。

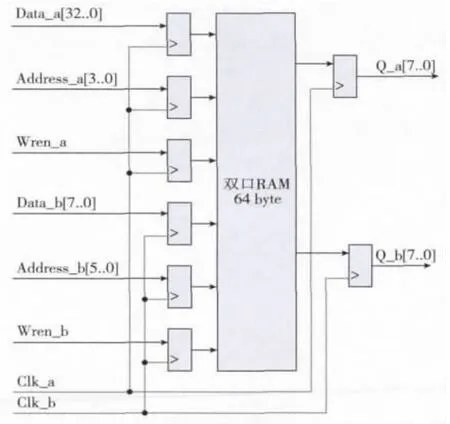

2.1.2 数据流控制

图3 Camera Link接口信号硬件连接图

在基模式下,传输时钟40 MHz,相机输出的5路LVDS差分数据,经DS90CR286A转换后,每个传输时钟传输28位并行数据,其中有视频数据24位(3个像素),帧同步信号FVAL,行同步信号LVAL,数据同步信号DVAL,SPARE备用信号。在FPGA中将24 bit的视频数据转换成3个串行的字节数据,采用1片双时钟、输入是32 bit数据、输出是8 bit数据、64 byte深度的双口RAM,作为视频数据的缓冲存储结构,双口RAM的逻辑框图如图4所示。

图4 双口RAM功能模块图

2.2 时序控制

2.2.1 VGA 时序控制

VGA的接口芯片采用AD公司的ADV7123KST140作为VGA视频D/A转换器,ADV7123KST140是3路高速、10 bit的视频D/A转换器,工业级芯片具有最大140 MHz的采样速率。

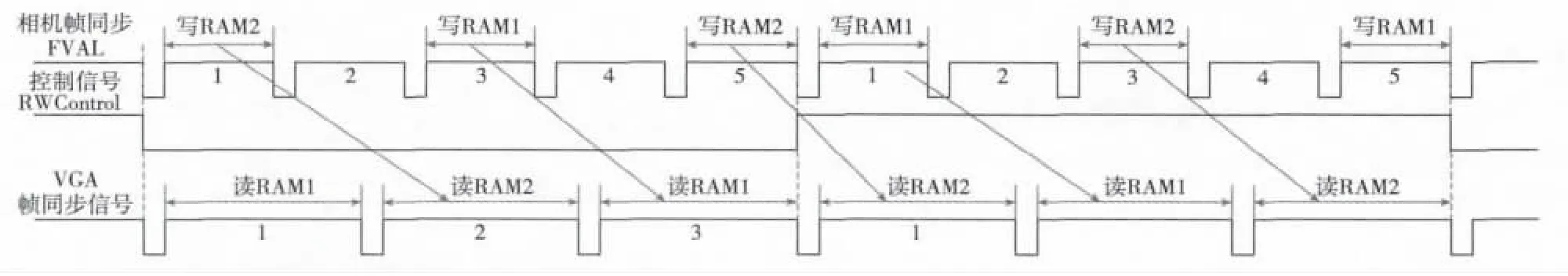

设计中采用VGA显示刷新频率为60 Hz,高速相机的帧频为100 Hz,为了达到帧率的匹配,FPGA在缓存存储过程中进行抽帧存储,每5帧抽取3帧,依次存放到外接的2个SDRAM中,存储扫描的时序如图5所示。

1)数据抽帧存储机制

(1)根据相机的帧同步信号FVAL进行5分频,得到控制信号RWControl,设立一个写存储器的状态计数器Wr,状态计数器Wr初始值为0,用控制信号RWControl的沿对状态计数器Wr进行清零工作。

(2)当控制信号RWControl为低电平时,当检测到相机的帧同步信号FVAL上升沿后,状态计数器Wr加1,抽取第1,3,5帧数据按照RAM2→RAM1→RAM2的顺序依次写入外挂的SDRAM中。

(3)当控制信号RWControl为高电平时,当检测到相机的帧同步信号FVAL上升沿后,状态计数器Wr加1,抽取第1,3,5帧数据按照RAM1→RAM2→RAM1的顺序依次写入外挂的SDRAM中。

2)数据读取扫描机制

(1)根据相机的帧同步信号FVAL进行5分频再3倍频,得到VGA帧同步信号。

(2)当控制信号RWControl为低电平时,当检测到VGA帧同步信号上升沿后,按照RAM1→RAM2→RAM1的顺序依次读取外挂的SDRAM中。

(3)当控制信号RWControl为高电平时,当检测到VGA帧同步信号上升沿后,按照RAM2→RAM1→RAM2的顺序依次读取外挂的SDRAM中。

图5 视频信号存储扫描时序

3)数据存储及扫描空间

(1)外挂的数据存储的SDRAM的空间大小是1 Mbyte,将SDRAM按照视频数据行、列进行存储,将SDRAM的地址线分为行、列地址空间,列地址空间0~1 023(A0~A9),行地址空间0~1 023(A10~A19),整个SDRAM可以存储1 024行数据,每行1 024个8 bit的像素。

(2)VGA显示器的分辨率是800×600,相机的分辨率是659×494,是视频信号显示在显示器中间,所以视频每一行视频数据的存储地址为70~728(A0~A9),视频行存储地址为50~543(A10~A19)。

2.2.2 PAL 时序控制

PAL输出接口采用INTERSIL公司的HI1171作为PAL制式视频D/A转换器,HI1171是8 bit的视频D/A转换器,工业级芯片具有最大40 MHz的采样速率。

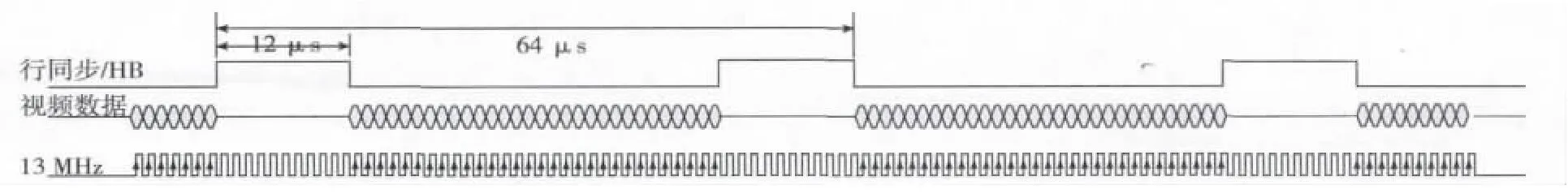

PAL模拟视频的场同步信号VB是根据高速相机的帧同步信号FVAL同步后,用13 MHz外部输入时钟进行计数产生,如图6所示。

图6 模拟视频场同步信号时序

模拟视频显示的行同步和消隐信号的实现思路是根据模拟视频场同步信号VB和13 MHz时钟计数产生,计到某一个数值时,使输出的信号翻转(由低电平到高电平或者由高电平到低电平),计数器的周期和翻转的周期根据不同的参数而有所不同。这些时序是在FPGA中编程实现,同时也容易调整和修改。模拟视频的奇偶行同步信号如图7所示。

图7 奇、偶行同步信号时序图

模拟视频显示的行同步信号、视频数据信号及时钟信号的时序关系如图8所示。时钟的上升沿选通并向HI1171写入数据。

图8 行同步与视频数据时序图

2.3 DSP 数据接口

FPGA与DSP之间实时通过EMIF接口完成视频数据的传输,数据线8位(D0~D7),传输时钟40 MHz,与相机的像素时钟一致,传输的视频区域为256×128,如图9所示。

3 DSP信号处理

图9 传输显示区域

DSP完成的主要工作包括数据传递、图像预处理、目标特征提取、目标位置计算。数据传递是利用DMA模式完成FPGA与DSP内部高速缓存之间的数据传递(见图10),图像预处理是对灰度图像进行图像分割,剔除图像中大部分的背景信息,使目标特征在图像中更加明显,目标特征提取是在预处理后的视频数据中,计算阈值门限,根据阈值门限进行数据二值化,将目标的特征信息提取出来,目标位置计算是通过行列坐标投影方式,计算出真实目标的行列坐标,并给出目标在整个图像中的位置信息。

图10 FPGA与DSP之间读写时序

3.1 图像分割

图像分割是通过对相邻两行的图像数据进行处理,用当前像素的灰度值与上一行像素灰度的均值进行比较,得到新的像素灰度值,计算公式为

式中:avg为上一行像素的灰度均值;p(x,y)为处理前的像素灰度值;f(x,y)为处理后的像素灰度值。

3.2 阈值计算

对图像分割处理后的图像数据使用直方图统计的方法,计算出图像的平均灰度,最大灰度值与最小灰度值,采用可变阈值法,计算出在不同目标极性条件下的阈值门限t。

3.3 数据二值化

根据得到的阈值门限进行数据二值化,计算公式为

3.4 位置计算

将二值化后的数据进行3×3数据滤波,滤波核根据实际需要进行设置,剔除低于最小识别目标的像素点,并采用行列投影的方式计算目标的行列中心位置,列出目标位置的矩阵,根据满足最小识别目标的大小及目标特征信息,剔除假目标,得到真实目标的坐标信息。

3.5 终端显示

将视频数据通过千兆网传送给终端计算机,由客户端软件进行图像显示。利用DSP6455片内的千兆以太网接口模块 EMAC/MDIO,结合片外的PHY芯片 Agere ETl01IC以及外围电路,扩展了以太网网络通信接口,采用100 Mbit/s的传输速率,传输协议采用无连接的UDP协议,提高系统数据的实时性,数据格式采用自定义的UDP图像数据结构,每个UDP包发送一行视频数据,数据结构中包括:包头(4 byte,自定义数据内容),图像帧号(2 byte),图像行号(2 byte),图像行数据(1行图像数据),实现网络化传输视频数据。

4 仿真结果及结论

经过仿真测试,FPGA内部SDRAM的数据时序如图11所示,仿真结果符合设计时序要求。

图11 SDRAM_FIFO数据仿真图

本设计的基于DSP+FPGA的Camera Link接口相机的图像处理平台能够稳定接收Camera Link接口的视频数据,VGA视频显示稳定,数据接口带宽及FPGA控制时序满足设计要求,在数据处理方面,DSP运算时间在帧周期的1/2左右,满足图像实时处理要求。

[1]江思敏,刘畅.TMS320C6000 DSP应用开发教程[M].北京:机械工业出版社,2005.

[2]江国强.EDA技术及应用[M].2版.北京:电子工业出版社,2007.

[3]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2003.

[4]TMS320C6455 Fixed -Point Digital Signal Processor[EB/OL].[2013-04-20].http://wenku.baidu.com/view/788c182e0722192e4536f6a0.html.