高速数据采集卡DDR控制器的设计与实现

2013-08-13王晓娇张治中

王晓娇,张治中

(重庆邮电大学通信网与测试技术重点实验室,重庆 400065)

随着网络流量的日益庞大,链路带宽的不断提升,在高速数据采集系统中,对双倍速率同步动态随机存储器(Double Data Rate Synchronously Dynamic RAM,DDR SDRAM)[1]所提供的大容量缓冲技术也提出了挑战。

现有技术中,DDR控制器对数据的封装处理和读写控制方法难以很好地兼顾数据访问的可靠性和有效性,且容错纠错能力较低、内存管理复杂。本文研究并设计了一种改进型高性能DDR控制器,保证了数据存储取的正确性、高效性和连续性,有效提高DDR存储器的管理效率和内存利用率。适用于多光口/电口的千兆线速数据采集系统,提供高速大容量的缓冲能力,在网络流量峰值时,能够实现动态均衡,平滑处理,可显著提高数据采集密度与速率。

1 DDR控制器工作原理

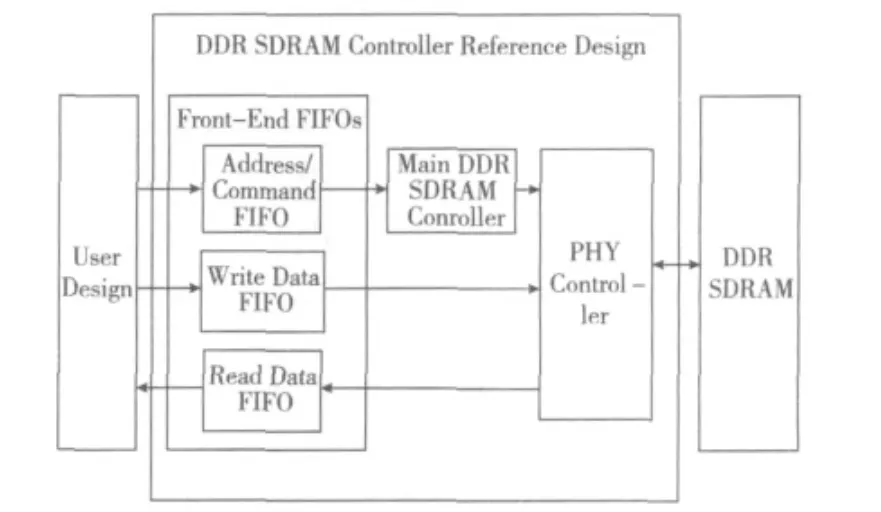

基于FPGA实现的DDR控制器通常主要包括前端主控模块和后端用户模块。以目前主流的Virtex-5 FPGA器件参考设计结构为例,如图1所示。

前端主控模块由PHY控制器、主控制器和前端FIFO组成。PHY控制器完成DDR存储器初始化状态和读数据采集时序校准逻辑功能,主控制器实现DDR控制器状态机和用于地址/命令/数据的FIFO逻辑,前端FIFO作为一种用户接口,提供地址/命令、写数据和读数据3个FIFO。前2个FIFO由不同的用户后端逻辑加载,而读数据FIFO则由PHY控制器访问,以将采集的数据存储在每个读周期上。通过用户接口,可以发出命令,向DDR存储器提供写数据或者读数据操作[1-3]。因此,在前端主控模块的设计结构相对固定的情况下,后端用户模块以及与前端模块对接方式的良好设计,对提升DDR控制器的整体性能具有重要作用。

图1 DDR SDRAM存储器控制器的参考设计结构

2 DDR控制器模块设计

2.1 基于FPGA的模块化设计

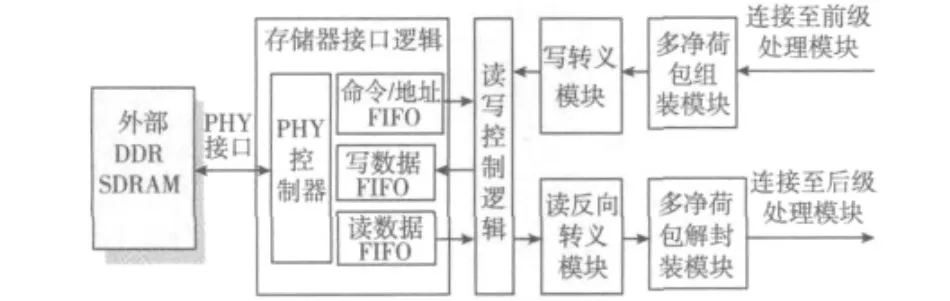

针对现有的DDR控制器对外部DDR 存储器数据读写访问所存在的不足,提出一种基于FPGA实现的模块化设计,采用多数据包重组和转义思想,以及读写控制方法,其模块设计框图如图2所示。DDR控制器主要包括:多净荷包组装模块、写转义模块、读反向转义模块、多净荷包解封装模块、读写控制逻辑以及存储器接口逻辑。

图2 DDR控制器模块设计框图

其中,多净荷包组装模块将把从前一级处理模块送入的多个净荷数据包拼接为一个较大的数据包;写转义模块完成对预写入DDR存储器数据的转义处理;读反向转义模块则实现对从DDR存储器读出的数据流进行反向转义,解析出正确的原始组装净荷包;多净荷包解封装模块将提取出原始单个净荷包;读写控制逻辑模块负责对DDR存储器的读写访问进行控制;存储器接口逻辑模块主要实现图1中的前端主控功能,完成对外部DDR存储器的读写访问,并为应用提供命令、读、写接口。

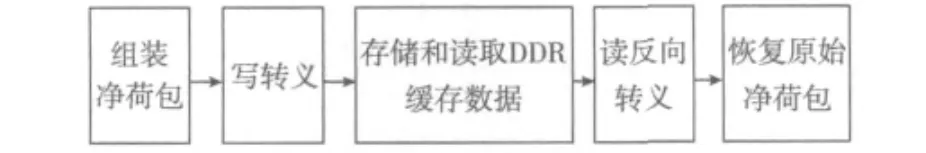

2.2 基本工作流程

DDR控制器存储和读取数据的基本流程如图3所示。首先,对多个净荷包进行组装并进行写转义处理;然后,在处于写操作时钟周期时,将写转义处理后的数据写入到DDR存储器中。当到达读操作时钟周期时,从DDR存储器中读取数据,并对读出的数据流进行读反向转义和解封装,恢复出原始单个净荷包。

图3 DDR控制器存储和读取数据基本流程示意图

3 数据预处理与解析

3.1 多净荷包的组装

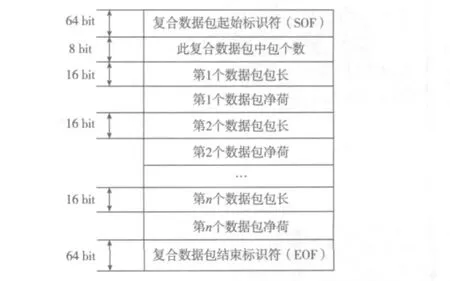

向DDR存储器写入数据前,对数据进行两级预处理。多净荷包组装是第一级数据预处理,该方法旨在有效减少短包对CPU的中断次数,降低资源开销,提高DDR控制器的处理效率。多净荷包组装模块封装的数据包格式如图4所示。

图4 多净荷包组装模块封装的数据包结构示意图

多净荷包组装过程:首先,将一个或一个以上原始数据净荷包分别增加一个标识有该包长度信息的数据包包头后级联在一起,并在第一个数据包包头前标识级联在一起的数据包的个数;然后,将级联在一起的数据包组装为一个复合数据包;在组装的同时,在复合数据包的头部加上64 bit特定的数据包起始标识符(Start of Frame,SOF),在数据包的尾部加上64 bit特定的数据包结束标识符(End of Frame,EOF)。其中,SOF和EOF可以在解析读出的数据流时,定位有效数据的起始位置与结束位置。

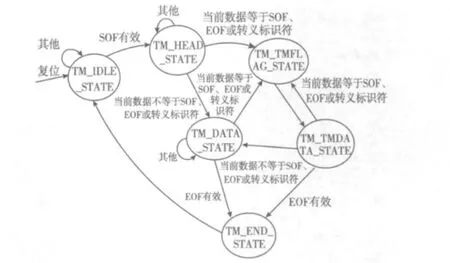

3.2 写转义的逻辑设计

写转义是第二级数据预处理,可避免在组装后的原始数据包中出现与SOF、EOF以及转义标识符相同的有效数据,从而影响数据的正确解析。写转义变换的规则是对相应的64 bit原始数据的最高位进行反码转换,并在其起始位置加上64 bit特定的转义标识符。写转义变换的实现流程如图5所示,其对应的写转义各状态含义见表1(TM是Transferred Meaning的英文缩写,表示转义)。

图5 写转义状态机

表1 写转义状态机各状态说明

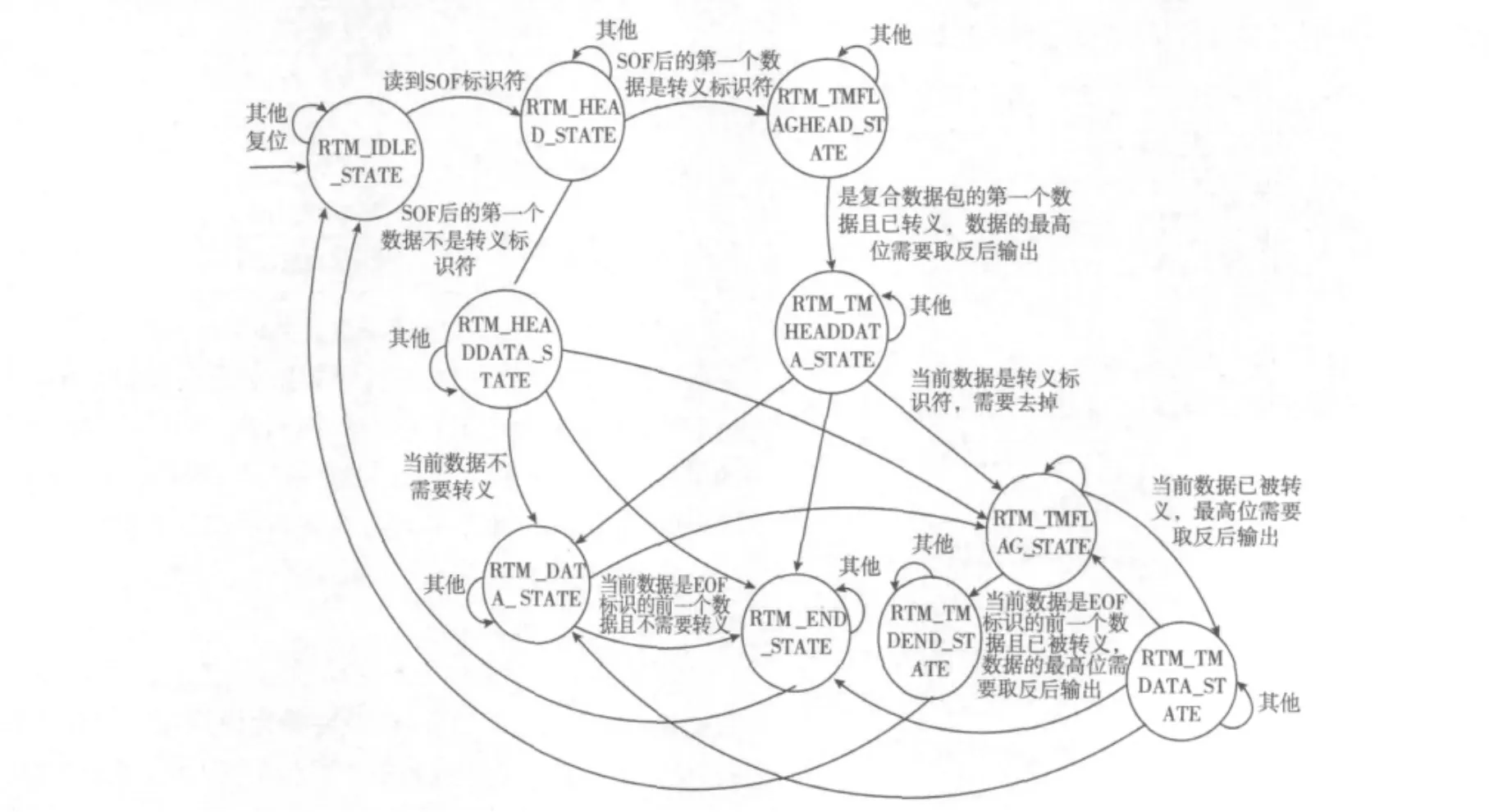

3.3 读反向转义的逻辑设计

读反向转义是写转义的逆过程,解析从DDR缓存所读取的数据流。读反向转义变换的规则是:从有SOF、EOF和转义标识符的数据流中读出并过滤掉SOF、EOF和转义标识符,同时将转义标识符后的64 bit数据的最高位进行反码转换,以恢复出原始数据。读反向转义的实现流程如图6所示,其对应的转义各状态含义见表2(RTM是Reverse Transferred Meaning的英文缩写)。

图6 读反向转义状态机

表2 读反向转义状态机各状态说明

4 读写控制逻辑设计

本方案中对DDR的读写控制主要有两个关键点,一个是64 bit和256 bit数据转换,另一个是读写均衡控制。前者的目的在于更有效地利用接口宽度和转义数据的读写粒度,存储、读取和解析数据。后者则以平均、轮流占用时间片的方式实现读、写操作所占用时间的均匀分配。

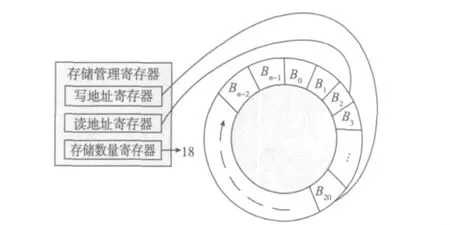

4.1 存储管理寄存器

在读写控制逻辑模块定义3个256 bit位宽的存储管理寄存器,分别用于写地址计数、读地址计数和存储数量计数。3个寄存器的协同工作运转过程如图7所示。

图7 存储管理寄存器协同工作运转过程示意图

写地址寄存器存放写入数据的地址。在写入1个256 bit的数据后,寄存器值加1,当达到1 Gbit容量的DDR存储器上限值时,寄存器值回到0。

读地址寄存器存放读取数据的地址。读地址寄存器在读出1个256 bit的数据后加1,当达到1 Gbit容量的DDR存储器上限值时,寄存器值回到0。

存储数量寄存器存放DDR存储器中当前存储的数据个数。在写入1个256 bit数据后加1,在读出1个256 bit数据后减1。当存储数量寄存器等于DDR存储器的容量大小时,表示存储器已满;当存储数量寄存器等于0时,表示DDR存储器为空。

4.2 64 bit和256 bit的转换

为了将写转义和读反向转义时,数据按64 bit粒度进行变换和解析,为达到存储器提供的256 bit读写接口的数据总线要求,在写转义后,对输出数据进行64 bit—256 bit的转换。而在读反向转义前,首先通过256 bit—64 bit FIFO将输入256 bit宽度的数据转换为64 bit位宽,为下一步反向转义做好数据准备。

4.3 读写均衡控制

为实现对DDR总线的分时复用[4-5],在读写控制模块中定义一个读写计数器,完成读写均衡控制中的计数功能。在连续写入固定量数据后,切换到读状态;在连续读出固定量数据后,又切换回写入状态,如此反复,可使读写吞吐量基本一致且足够大。

经仿真测试和计算单位时间内读写的数据个数,如果每次读写数据为4 kbyte,读、写操作的总速率可达到18 Gbit/s,每个单向具有9 Gbit/s的速率。写入数据时,如果连续写入数量未达到4 kbyte,却出现没有数据输入或DDR存储器已满时,将主动切换到读数据状态。在读数据时,在连续读出数量未达到4 kbyte,却出现DDR存储器已空时,将切换到写数据状态。

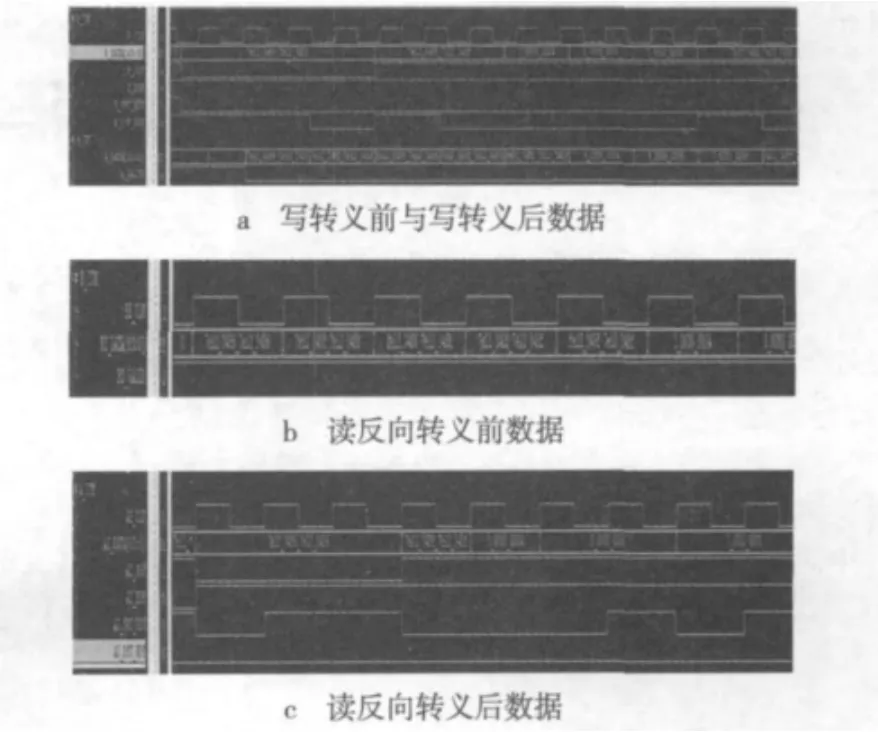

5 仿真测试

为了验证方案中转义处理的可靠性和有效性,图8给出了写转义和读反向转义的FPGA仿真图。图8a中B_TM是写转义前的数据,A_TM是写转义后的数据,设置SOF标识为64 bit特定数据0x7e1234567e123456,EOF标识为64 bit特定数据0x7e12345d7e12345d,转义标识符为64 bit特定数据0x7e12345f7e12345f。从图中,可以看出写转义前的数据为0x7e1234567e123456,0x7e12345f7e12345f,0x300000004,……,其中,SOF标识后的第1个64 bit有效数据与转义标识符相同,于是对其进行转义变换为0x7e12345f7e12345f,0xfe12345f7e12345f,如图 8b 所示,B_ITM是从DDR存储器读出数据后,读反向转义前的数据。图8c中的A_ITM是读反转义后的数据,与原始数据一致。采用转义的方法后,读数据时的时延问题(发送读命令后,期望的数据要在几十个时钟周期后出现在读数据总线上)可以得到有效解决。

图8 DDR控制器写转义与读反向转义仿真图(截图)

6 结束语

本文提出一种基于FPGA实现的DDR控制器设计方案,采用了多净荷包组装,转义与反向转义方法以及读写控制的流量均衡算法设计,改进了数据封装与解析方式以及读写控制方法。该DDR控制器统筹兼顾了数据读写的可靠性和有效性,有效提高了DDR存储器的管理效率和内存利用率。经实际应用测试,该DDR控制器在千兆线速数据采集卡中已得到有效运用,保证了高速大容量的数据缓冲功能,具有广泛适用性和较高的应用价值。

[1]DOUBLE DATA RATE(DDR)SDRAM Specification[EB/OL].[2012-06-10].http://download.csdn.net/detail/macrojiali/3069228.

[2]使用Virtex-5 FPGA器件实现DDR SDRAM控制器[EB/OL].[2012-06-10].http://www.docin.com/p -9751883.html.

[3]门亮,王立欣.基于FPGA的DDR SDRAM控制器在高速数据采集系统中的应用[J].电子产品世界,2007(C00):99-103.

[4]姚玮,赵海庆,陈金树.基于Stratix器件的高速DDR缓存系统优化设计[J].电视技术,2005,29(S1):69-72.

[5]ZHOU Zude,CHENG Songlin,LIU Quan.Application of DDR Controller for High-speed Data Acquisition Board[C]//Proc.Innovative Computing Information and Control,ICICIC '06.Beijing,China:[s.n.],2006:611-614.