GSM的下行同步算法设计与FPGA实现

2013-08-09许起明余翔

许起明,余翔

(重庆邮电大学无线定位与空间测试重点实验室,重庆 400065)

目前我国的移动通信系统正在由2G向3G过渡,二者将在很长一段时间内共存。尽管3G有很多优势但GSM及其增强标准EDGE和GPRS是目前世界上覆盖最广的移动通信网络[1-3],在未来很长一段时间内,移动终端中仍会兼容GSM标准。GSM系统的同步过程是非常关键的技术。移动终端MS能否充分享受到小区提供的服务,与其开机后能否尽快驻留在一个满足驻留条件的质量较好的小区息息相关,这对于以后要进行的各种交互过程都有重大的影响。而驻留小区的第一个关键过程就是同步过程。因此研究同步过程不论是对于2G还是3G都具有重大意义。

本文针对GSM系统提出了一种基于FPGA的下行同步算法设计方案,并且选用Altera公司的Cyclone III系列芯片,经Modelsim仿真,板级调试,最终该方案得到验证并应用到了实际项目中。选用的芯片是Altera公司的Cyclone III系列EP3C25Q240C8芯片,功耗小,系统综合能力强,价格较低,包含了24 624个逻辑单元、594 KB内存大小和4个锁相环,硬件资源完全满足测试要求。

1 GSM系统的同步原理

在移动通信系统应用中,移动终端MS开机后必须尽快搜索到一个合适的小区,然后与这个小区达到时隙和频率上的同步,才能获取该小区的详细信息。移动终端只有在登录到小区后才能使用网络服务。通常把从开机搜索到登录到合适小区的过程定义为小区初始搜索过程,简称小区初搜。同步是小区初搜中的一个关键步骤,指的是从开机到与小区达到时频同步的过程。

本文是基于GSM系统中的帧同步,在GSM系统中主要是利用专门的帧(FB和SB)来完成帧同步[4]。

GSM系统的基站通过广播信道(BCH)传输信令信息,它包括3种数据类型:频率矫正突发(FB),同步突发(SB)和广播控制信道(BCCH)。小区初搜的目的就是解读这些突发中的信息来驻留小区。

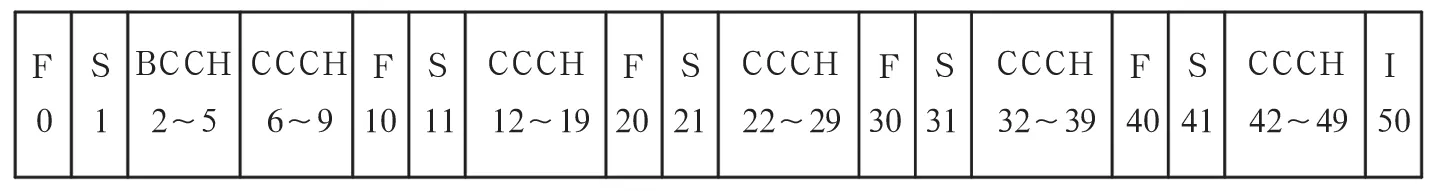

控制信道(CCH)包括BCH、公共控制信道(CCCH)和一个空闲(Idle)帧,它的帧结构为51复帧,由51个TDMA帧组成,每帧分为8个时隙(0~7),每个时隙的持续时间约为576.9 µs (15/26 ms),其中携带的物理内容叫做突发(Burst),在每帧的时隙0中发送广播信息,其结构如图1所示[5]。

图1 CCH的51复帧的帧结构

其中F代表FB,S代表SB,I代表Idle。FCCH对应着一个频率校正突发脉冲序列(FB),FB主要有两个用途:一是MS开机时发现本地可用的网络,以驻扎到本地小区,二是MS开机运行时内部频率的微调。FB不携带信息,由148个全“0”比特组成,它结构简单,便于检测。SCH对应一个突发脉冲序列(SB),它包含一个64 bit的训练序列并携带有基站识别码(BSIC)和帧信息。BCCH广播基站的一般信息,MS解读这些信息,在确认合法后选择相应小区,完成整个小区驻留过程。移动台通过对这两种逻辑信道(FCCH和SCH)的同步来实现与基站的同步。其中FCCH用来完成粗同步,SCH用来完成精同步。

2 GSM同步算法设计

2.1 FCCH粗同步算法设计

由于FCCH经GMSK调制后是一个频率高于载波频率的67.5 kHz正弦波,其频谱必然具有尖锐的单峰特性[4]。因此,我们可以在其幅度谱中检测单峰,进而捕获FCCH。在FPGA中实现时,可以直接对基带处理过的数据进行FFT处理,并寻找最大峰均比,从而确定FCCH的位置。

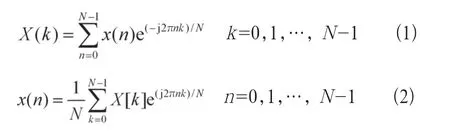

FFT算法是基于离散傅里叶变换(DFT)及其反变换的求和运算的嵌套分解以及复数乘法的对称性来实现的。如式(1)和式(2):

式(1)是傅里叶正变换,式(2)是傅里叶逆变换,其中x(n)是时域周期序列,X(k)是频域周期序列。

其中一类FFT算法为库利—图基(Cooley-Tukey)基r按频率抽选(DIF)法,将输入序列循环分解为N/r个长度为r的序列,并需要级运算。算法的核心是蝶形运算,蝶形运算的速度直接影响整个设计的速度。Altera的FFT IP核选用的是基4运算,若N是2的奇数幂,则FFT IP核在完成转换的最后自动使用基2运算。利用FFT IP核大大减小了算法的复杂性。Altera官方提供的FFT IP核具有稳定高效等特点,直接调用该IP核,能大大减少开发周期。

2.2 SCH精同步算法设计

用FPGA实现SCH同步的常见方法有两种:滑动窗口相关法和基于FFT进行快速相关法。

方法1:滑动窗口相关法。滑动窗口相关法即是对SCH的训练序列进行滑动延迟并与GSM中频数据序列进行相关处理,获得最大相关峰,此最大相关峰的位置即是SCH的位置。在FPGA中,在确定完FCCH位置之后,由于这个位置存在一定偏差,这里选取FCCH之后半帧的位置作为起始位置选取1帧数据作为GSM中频数据序列,该序列中必然包含SCH的起始位置。选取的这1帧数据不变。通过对训练序列不断向右滑动,同时将滑动后的序列数据与这1帧数据做相关。这样当滑动完这一帧数据必然会出现一个最大相关峰,这就是SCH的起始位置。

优缺点:这种方法耗费的FPGA的资源较少,实现简单,但这种方法的实时性不高。

方法2:基于FFT进行快速相关法。FFT快速相关法:在FPGA中可以使用快速傅里叶变换方法来实现相关[6]。

图2 SCH的算法流程图

式(3)中序列z(n)是序列x(n)和y(n)的相关结果,由推导可以看出序列z(n)同时也是序列x(-n)和y(n)的卷积。

本文用快速傅里叶变换来实现相关是基于图2来完成的。本文中所有数据都是经过4倍采样处理的,51复帧结构中1帧包含5 000个样点。具体实现过程如下。

(1) GSM的基带数据用x(n)表示,长度用M表示。SCH的训练序列的数据用y(n)表示,长度用N表示。

(2) 对序列x(n)和y(n)进行补零。在x(n)后面补L-M个零,形成长为L的序列。在y(n)的前面补(M-1)个零,在y(n)的后面补(L-M-N+1)个零,形成长为L的序列。

(3) 选取序列L≥M+N-1,且使L=2r,其中r为正整数。其中本设计中数据长度M为750,SCH训练序列的数据是已知的64bit由于本设计中采用4倍采样,所以这里训练序列的长度N为256,L的长度为1 024。

(4) 再对序列x(n)与y(n)分别进行FFT运算,结果分别为X(n)与Y(k)。

(5) 将X(k)的复共轭X*(k)与Y(k)相乘得到Z(k)。

(6) 对Z(k)进行逆傅里叶变换IFFT运算,结果为z(n)。

(7) 最后截取z(n)从第N个到第M个值,找出幅值最大的点的位置,再将所得结果倒序,即得SCH的起始位置。

优缺点:算法实现较复杂,耗费FPGA的资源也较多但实时性高,实现同步所需时间短。

实际的应用中要综合考虑实时性和FPGA芯片资源。基于对实时性的考虑本文选取基于快速傅里叶变换方法来实现SCH的精同步。实际中选择的Alter Cyclone III芯片的资源也是完全满足的。实际测得基于快速傅里叶变换方法来实现SCH的精同步所用时间是毫秒级的而使用滑动窗口相关法则需要几秒。显然前者实时性更高。

3 FPGA仿真结果分析

3.1 FCCH粗同步仿真结果分析

在完成整个程序的Verilog代码编写后,针对实际情况编写testbench代码,并用仿真工具Modelsim进行仿真,根据仿真结果,不断修改代码调试,以使仿真结果符合设计要求。

图3所示是粗同步在Modelsim中的仿真结果,其中datain_real和datain_imag分别是进入FFT的I/Q两路数据,dataout_real和dataout_imag分别是经过FFT处理后的I/Q两路数据。frames_in是进入FFT的帧数, frames_out是经过FFT处理后的帧数。num是存放FCCH位置的计数器。如图num由46帧变为154帧,这里的FFT的帧长为512,它们之间的距离转化为51复帧就是11帧,这就说明frames_in为154的帧就是要找的FCCH的位置。图4是FCCH在MATLAB中的频谱分析图,其中横坐标代表进行FFT处理的数据位置标号,纵坐标代表数据经过FFT处理过后的峰值大小,这里在Modelsim和MATLAB处理的是同一组数据,由图中可以看出的结果和Modelsim仿真结果一致,这里MATLAB是从第1帧开始计数的,而在FPGA中是从第0帧开始计数的。

3.2 SCH精同步仿真结果分析

图3 粗同步仿真时序图

图4 粗同步MATLAB仿真时序图

图5是精同步在MATLAB中的时序分析图。其中横坐标代表进行IFFT处理的数据位置标号,纵坐标代表数据经过IFFT处理过后的峰值大小,这里在Modelsim和MATLAB处理的是同一组数据,对比发现其结果和Modelsim仿真出来的结果一致。图6是精同步在仿真工具Modelsim中的仿真结果,其中source_real-rrr和source_imag_iii分别是经IFFT变换后数据的I/Q路,max为这I/Q两路数据的幅值比较找出最大幅值点,log为最大幅值点的位置。

图5 精同步MATLAB仿真时序图

通过仿真对比验证可以证明此算法是切实可行的。在FPGA中可以实现整个算法流程。

图6 精同步仿真时序图

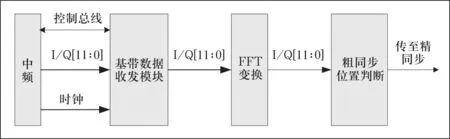

4 FPGA实现GSM同步的流程

4.1 FPGA中实现FCCH粗同步

图7 粗同步流程图

本文中调用FFT IP核来实现FFT变换,FFT核的参数选取如下:变换长度(Transform Length)为512,数据精度(Data Precision)为12 bit,数据流模式(I/O Data Flow)为流模式,其它选项选择为默认。从IP核配置界面中可知,占用的LEs为3 265,Memory Bits为90 112,可见实现粗同步对芯片资源耗费还是很高的。最后对经过FFT变换的数据的模值取峰均比,由于GSM FCCH的特性在一个51复帧会出现5个峰均比很大的点,这5个点之间相距10帧的长度,一个51复帧中最后一个峰均比很大的点与下一个51复帧的第一个峰均比很大的点之间由于有1个Idle帧,它们相隔11帧。所以只要计算这几个明显比较大的峰均比的点的距离即可找到FCCH的位置。

4.2 FPGA中实现SCH精同步

当确定FCCH的位置后,由GSM 51复帧结构可以看出FCCH帧与SCH帧相隔1帧,因本文的数据为4倍采样的数据,因此一帧的距离就有5 000个样点。实际项目中在确定FCCH位置后选它之后的4 700点开始存750个样点进入FIFO中,这750个样点必然包含SCH的起始位置。然后按快速傅里叶变换方法对它进行补零形成1 024序列。再对补零之后的序列进行FFT变换。这里采用的FFT的参数如下:变换长度为1 024,数据精度为12 bit, 数据流模式为突发模式(数据吞吐量小但占用资源少),其它选项选择为默认。从IP核的配置页面可看出,所占用的LEs是2 814,Memory Bits为 57 344。

GSM的SCH对应一个突发脉冲序列(SB),它包含一个64 bit的训练序列是已知的,这里也要对训练序列进行4倍采样,然后按快速傅里叶变换方法对它进行补零成1 024序列。实际项目中对补零的1 024序列在MATLAB中做FFT变换然后把变换之后的结果保存在Altera 的ROM IP核中。

根据快速傅里叶变换方法,对这两组数据补零形成1 024序列再进行共轭点乘。在FPGA中可以利用一个乘法器完成这一功能。实际项目中所选用的乘法器是Alter提供的ALTMULT_ADD这一IP核。这个IP核有4个输入1个输出,由于GSM数据分为I/Q两路,选用这一IP核可以一次性计算一组数据的点,而不需要使用多个普通的乘法器IP核,因此,该方式节约了芯片资源。

最后对乘法器输出的数据(24bit)进行IFFT变换。由于芯片上的资源有限,实际中没有用24bit的FFT IP核,这里采用的FFT是复用上一个FFT。实际中选择乘法器输出的数据的高12bit进入FFT中进行数据的相应处理,实验证明这种选取偏差很小,实际中可以采用。

对IFFT输出的最后结果,截取其中第N个到第M个值,找出幅值最大的点的位置,再将所得结果倒序,即得要找的SCH的起始位置。

同频流程见图7和图8。

图8 精同步流程图

5 FPGA程序正确性验证

为验证Verilog编写的程序的正确性,使用Quartus II中自带的逻辑分析仪(SignalTap II Logic Analyzer)对FPGA芯片内部的输入和输出信号进行实时的采样,把各个模块的实际结果与Modelsim仿真的结果进行对比验证。经过不断地调试使实际处理数据得到的结果和Modelsim仿真得出的结果一致。

通过粗同步逻辑分析仪时序图,可以看出该结果和Modelsim中的仿真结果一致。与精同步的逻辑分析时序图对比发现其结果也和Modelsim仿真结果一致。

经过逻辑分析仪的验证,说明此算法在FPGA中实现是可行的且实时性好、稳定度高。

6 小结

本文基于FPGA提出一种高实时性的GSM帧同步实现方案。通过Modelsim对各子模块进行仿真测试,并借助Altera Cyclone III芯片进行板级联调,最后利用Quartus II自带的逻辑分析仪进行调试和验证,该方案的可行性已在工程实现中得到了极好的验证,同时该方案也对其它通信系统帧同步的实现具有一定参考价值。

[1] Halonen T, Romero J, Melero J著,彭木根, 刘萍译. GSM/ GPRS和EDGE系统及其关键技术: 向3G/UMTS系统演化[M] .北京:中国铁道出版社, 2004.

[2] ETSI EN 300 908, Multiplexing and Multiple Access on the Radio Path(GSM 05.02 Version 8.5.1)[S]. 1999.

[3] ETSI EN 300 959, Modulation (GSM 05.04 version 8.1.2) [S].1999.

[4] 夏玲.GSM/GPRS系统物理层算法仿真及基于ZSP核的优化实现[J].浙江大学.2006.

[5] 王正生.GSM接收机同步技术研究与基于FPGA和DSP的接收机设计[J].北京交通大学.2009.

[6] 何方白,张德明,阳莉,李强,刘焕淋.数字信号处理[M].北京:高等教育出版社.2009.

[7] Altera Corporation.Integer arithmetic megafunctions user guide[EB/OL]. http:// www. altera.com/literature/ug/ug_lpm_alt_mfug.pdf.2010.

[8] Altera Corporation. FFT MegaCore functionuser guide[DB/OL]. http://www.altera. com/literature/ug/ug_fft.pdf. 2011.