基于FPGA的S模式应答机设计

2013-07-20李超史忠科

李超,史忠科

西北工业大学 自动化学院,西安 710129

基于FPGA的S模式应答机设计

李超,史忠科

西北工业大学 自动化学院,西安 710129

1 引言

S模式应答机是一种所有飞机必须装备的机载通信设备,用于报告本机信息,保障飞行安全[1]。在通用航空中,飞机主要以目视规则运行,且飞行机动性大,存在较大隐患。广播式自动相关监视(ADS-B)是以广播的形式将本机的GPS方位、速度,以及气压高度等信息以约每0.5 s一次的频率发送给附近的飞机以及地面站,使附近飞机进行避让的一种防撞方法[2-3],可以有效保障通用航空的飞行安全,其1090ES数据链通过对S模式应答机升级就可实现[4],在数据链能力以及成本方面均占有优势。

然而,现有的S模式应答机的控制器与收发电路仍然采用传统数字电路来完成对数字信号的处理[5-6],这就直接导致其设备庞大,成本过高,不利于在内部空间有限的小型通用航空飞机尤其是无人机上使用,在低空空域开放的局势下,阻碍了通用航空的发展。现场可编程逻辑门阵列(FPGA)具有并行处理能力强,集成度高,实时性好的特点,非常适合于高速数字信号处理的应用。针对以上分析,本文设计了一种基于FPGA的通用S模式应答机,仅采用一片小型FPGA,就实现了S模式应答机所需全部功能。

2 系统功能分析

2.1 总线接口设计

为了获取本机信息,系统需要与ARINC429总线通信来获取本机高度以及代号,通过RS232总线获取GPS数据[5]。本文采用两片电平转换芯片将总线电平转换为FPGA使用的LVTTL电平,在FPGA中进行本机信息的接收;由于这种技术目前已十分成熟,因此本文概不冗述。

2.2 通信编解码的实现

应答机的功能就是对询问信号解码,自动识别,并以相应格式编码应答。S模式应答机的通信格式有A、C与S模式,其中A模式为飞机代号询问,C模式为飞机高度询问,S模式以S模式数据链通信,包括飞机代号、高度、速度、在空中/在地面等一系列信息,其通信格式如图1所示[7]。

图1 S模式应答机的信号格式

2.3 抗干扰设计

当信号由通信板传来时,由于空间场干扰、电源干扰及信号通道干扰,造成信号的毛刺,脉冲宽度的变化等,无法直接对其进行解码,因此必须对信号进行滤波整形。本文在FPGA内设计了一种数字滤波器,用于S模式应答机接收信号的滤波。

3 通信编解码部分设计

系统需要解码的信号有A/C模式询问信号以及S模式询问信号,如图1所示,其中P1、P2、P3脉冲均为0.8 μs,而P4脉冲宽度仅在A模式为0.8 μs,A-C/S模式为1.6 μs。系统中编解码模块均采用状态机的方法实现。滤波后的信号送入解码模块后,如果是A/C模式询问信号,则对A/C编码模块发送信号让其以PCM编码应答;如果是A/S、C/S、或S模式询问信号,则对S模式编码模块发送信号并传输数据,让其按相应格式以PPM编码发送数据应答。

如果正在对一个询问进行应答时接到另一个询问信号,解码模块会将其延后至应答结束,并等待50 μs后给相应的模块发送信号及数据,使其应答。基于ADS-B的相关规定,为避免信号混叠,本文在解码模块中设置了一个随机数发生器,使其可每隔500 ms±100 ms产生一个信号,如果空闲,则使S模式调制模块广播本机ADS-B数据,如果忙碌,则延后发送[8]。

编、解码部分的流程如图2所示。采用状态机的方法来自动识别A模式、C模式和S模式的信号,其中PA3至PA5状态、PC3至PC5状态、PS3至PS6状态分别代表检测到A模式、C模式和S模式询问。P0为等待状态;当检测到脉冲上升沿时,进入P1状态;如果在0.8 μs后检测到下降沿,即接收到了完整的P1脉冲,进入P2状态,否则若在0.7 μs以内检测到下降沿或超过0.9 μs未发现下降沿,说明这个高电平信号不是要接收的P1脉冲,返回等待状态P0;在P2状态时,根据不同模式P1状态与P2脉冲的间距不同,若在1.2 μs后检测到上升沿,进入PS3状态,若在7.2 μs后检测到上升沿,进入PA3状态,若在20.2 μs后检测到上升沿,则进入PC3状态。后面信号流程与之前类似,其输出结果如图中所示,其中输出A/C模式将发送信号至A/C模式编码模块令其以相应模式应答,而输出S模式将发送信号至S模式编码模块并开始接收数据。

图2 编、解码部分流程图

实验效果如图3所示,以A模式和S模式为例。可以看出,系统对询问信号能以相应格式进行应答,满足系统要求。

图3 滤波后询问信号与应答信号对比图

4 数字滤波部分设计

当信号由通信板传来时,由于空间场干扰、电源干扰及信号通道干扰,造成信号的毛刺、脉冲宽度的变化等,将使编解码模块无法正常进行解码,造成信号的丢失,当干扰较强时这种现象尤为严重。图4为无数字滤波器时系统对信号的响应。这里对系统发出一组测试信号,以观察系统的响应。由于在实验室中进行实验,干扰较小,因此译码率较高,用滤波器难以提取解码错误片段,因此,这里使用Signal Tap II采集数据。可以看出,图4(a)中4 096~4 608采样点之间的C/S模式全呼叫询问因脉冲宽度发生变化,因此无法成功解码,导致没有应答;而图4(b)中4 608~6 144采样点之间的A模式全呼叫及C模式全呼叫也因为脉冲宽度变化没有应答。因此,必须在系统中加入数字滤波器,否则可能因为对询问信号无响应而发生危险。

图4 无滤波器时解码错误

当FPGA收到由通信板经光耦传来的信号时,所有毛刺干扰经过FPGA的I/O管脚之后均会变成脉冲干扰。由于所有送往FPGA的信号均为脉冲信号,如果将其转为数字信号并设计FIR滤波器进行滤波,延迟明显偏大。而使用脉冲宽度滤波方法简单,占用资源小,延迟小,效果较好。经实际测试,干扰脉宽大多较窄,不超过0.1 μs,只有极少数干扰较宽,最宽也不超过0.3 μs。而由前文可知,所有头脉冲部分脉冲信号最窄为0.8 μs,询问信号中只有S模式询问数据为0.25 μs一个码元;根据DO-181D以及GB12183[9]的规定,头脉冲允许±0.1 μs的误差。当解码模块在检测到S模式头脉冲后,开始接收数据时,将返还给滤波模块的en信号置1。当en=0时,将宽度小于0.65 μs的任何信号视为干扰滤掉;en=1时,只将宽度小于0.2 μs的信号视为干扰滤掉。这样,即使偶尔某些较宽的干扰脉冲出现在数据段,导致接收错误,也可通过数据中包含的奇偶校验位来发现。

系统采用了20M的时钟信号,滤波器以每个时钟周期0.05 μs对信号进行采样,将采样的数据依次循环存储在15个二进制寄存器中,并使用加法器将其相加。如果其和大于等于12,则输出高电平,并在结果小于12后使用计数器保持高电平11个时钟周期,以复现输入的波形。当检波模块返还的en信号为1时,将采样的数据存储在另外4个寄存器中,并相加,如果大于等于3,则输出高电平,并用计数器保持。为了使两部分滤波器相配合,则将0.25 μs滤波器数据放入一个9位的寄存器的末位,每个时钟周期将寄存器后一位的值赋予前一位,并将第一位的数据作为滤波结果输出,以达到延后的效果。en=0滤波器的流程图如图5所示,其中add1为15位加法器的输出,cnt1是一个计数器,每当时钟上升沿自增1,Z为滤波器输出。en=1时与其类似,仅加法器与计数器的位数不同。

图5 en=0时滤波器流程图

滤波效果如图6所示,其中,图6(a)为A模式全呼叫询问信号,图6(b)为S模式全呼叫询问信号,图6(c)和图6(d)分别为在强干扰下的仅C模式全呼叫询问信号和S模式全呼叫询问信号的滤波效果,所有图均为5 μs/div。由图可以看出,滤波延迟仅有1 μs左右;经过大量实验数据表明,在弱干扰下译码率接近100%,强干扰下译码率较低,仅有76%左右,预期滤波效果已经达到。

图6 滤波效果图

5 系统总体测试及对比

5.1 系统资源占用情况

采用了一片Altera的EP2C8T133C8芯片作为系统的主芯片。系统各功能模块在FPGA上实现后,占用资源情况如表1所示。

表1 主要资源模块占用情况

从表1中可以看出,整个系统模块占用内部LE 3 071个,约为37%,寄存器(registers)1 078个,约为13%,内部存储单元(memory bits)61 440个,约为37%,满足选型时出于系统余度考虑的3倍的要求。

5.2 系统实验结果

使用自制的通信板进行了实验,使用Tektronix公司的DPO7354示波器对实验数据进行了采集,限于篇幅,仅列出具有代表性的实验结果,如图7所示。图中依次为对A模式、C模式、A/S模式、C/S模式、仅C模式以及S模式询问的应答,频道1为接收到的询问信号,频道2为所产生的应答,询问信号后的脉冲为应答信号对示波器探头所产生的干扰。

图7 询问信号与应答信号对比图

从图7可以看出,系统设计的滤波器成功地滤掉了干扰,并进行了检波,做出了相应的应答。对A模式、C模式分别以相应模式的PCM编码应答;对A/S、C/S模式以S模式全呼叫回答进行应答;对仅C模式成功抑制,不进行应答;对于S模式则以相应数据格式进行应答。

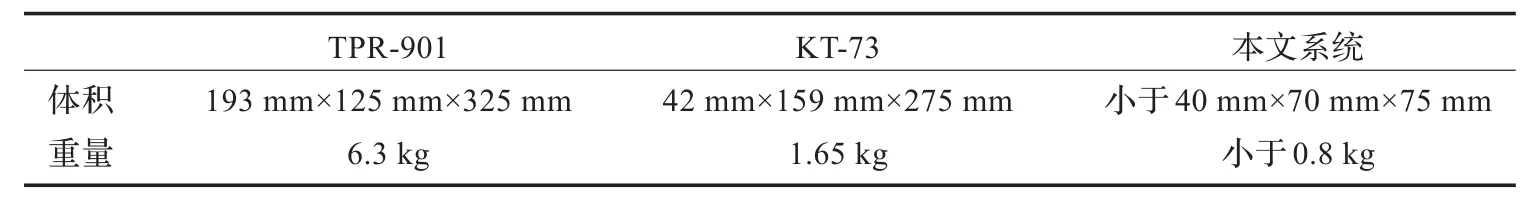

表2 系统与传统应答机的对比

5.3 与传统应答机的对比

与Rockwell Collins公司2009年的产品TPR-901应答机以及Honeywell公司2005年的产品KT-73应答机在体积、重量两方面进行对比,如表2所示,可见本文系统比目前最小的应答机小一半以上。由于通信板尚未小型化,系统尚未工程化,给出的数据仅为估计值。

6 结束语

本文针对现有S模式应答机体积、重量过大的缺陷,设计了一种基于FPGA的新型S模式应答机。系统由总线接口、通信编解码及抗干扰设计三部分组成,经过测试,三部分均工作稳定,能在有干扰的环境下对询问信号进行应答。实验结果表明,该系统的体积和质量比传统S模式应答机小,并且成本更低,有着较好的应用前景。

[1]Spalding D J.Mode S-the future[J].Aviation Surveillance Systems, 2002(1):1-4.

[2]Boisvert R E,Orlando V A.ADS-MODE S system overview[C]// Proceedings of the Digital Avionics Systems Conference,1993:104-109.

[3]Speealman L,Lee K.Cargo airline association ADS-B data link evaluation and production[C]//Proceedings of the AIAA/IEEE Digital Avionics Systems Conference,1999.

[4]Chung W W,Staab R.A 1090 extended squitter automatic dependent surveillance-broadcast(ADS-B)reception model for air-traffic-management simulations[C]//Proceedings of the AIAA Modeling and Simulation Technologies Conference and Exhibit,2006,8:1-11.

[5]Honeywell.Bendix/King KT 73 data link transponder.System Installation Manual,2005.

[6]Rockwell Collins.Rockwell Collins TPR-901-003/021 transponders.System Installation Manual,2009.

[7]RTCA.DO-181D Minimum operational performance standards for Air Traffic Control Radar Beacon System/Mode Select(ATCRBS/MODE S)airborne equipment[S].Washington,D C,2007.

[8]RTCA.DO-260B Minimum operational performance standards for 1 090 MHz Automatic Dependent Surveillance-Broadcast(ADS-B)[S].Washington,D C,2006.

[9]国家技术监督局.GB12183空中交通管制机载应答机通用技术条件[S].北京,1990.

LI Chao,SHI Zhongke

Institute of Automation,Northwestern Polytechnical University,Xi’an 710129,China

Aimed at large volume,heavy weight of the existing mode S transponder,thus it is not applicable to small general aviation aircraft especially small UAVs(Unmanned Aerial Vehicles),a new mode S transponder of general aviation is designed.The system adopts all-FPGA(Field Programmable Gate Array)design,the state machine is used to approach the realization of encoding and decoding function,a digital filter for the signal is designed by pulse width filtering method.The test results show that the system works stably,response of the interrogation signal is realized,and meets the RTCA DO-181D and DO-260B standards.For the system’s advantages of small volume,light weight,low cost,it is suitable for the general aviation aircraft whose interior space is limited.

mode S transponder;Field Programmable Gate Array(FPGA);general aviation;state machine;digital filter

针对现有S模式应答机体积、重量过大,不适用于小型通用航空飞机尤其是无人机的现状,设计了一种用于通用航空的新型S模式应答机。系统采用全FPGA设计,用状态机的方法实现编码、解码功能,使用脉冲宽度滤波的方法对通讯信号进行了数字滤波。实验结果表明:该系统工作稳定,实现了对询问信号的应答,符合RTCA的DO-181D及DO-260B标准;并且具有体积小,重量轻,成本低等特点,适用于内部空间有限的各种小型通用航空飞行器。

S模式应答机;现场可编程门阵列(FPGA);通用航空;状态机;数字滤波

A

TN911.72

10.3778/j.issn.1002-8331.1204-0775

LI Chao,SHI Zhongke.Design of mode S transponder based on FPGA.Computer Engineering and Applications,2013, 49(13):31-35.

国家自然科学重点基金(No.61143004)。

李超(1986—),男,硕士研究生,主要研究方向为硬件电路设计以及FPGA数字信号处理。E-mail:limiaosen@sina.com

2012-05-10

2012-08-27

1002-8331(2013)13-0031-05

CNKI出版日期:2012-11-28http://www.cnki.net/kcms/detail/11.2127.TP.20121128.1456.023.html