一种基于40nm 高速SRAM的自定时电路设计

2013-07-20魏芳伟

魏芳伟,张 鹰

(电子科技大学,成都 610054)

1 引言

在数字集成电路中存储器占据了整个芯片大部分的面积和功耗,存储器功耗的降低会使整个芯片的功耗大幅降低。近年来,静态存储器(SRAM)被广泛应用于便携设备中,高速低功耗成为SRAM 发展的 必 然 趋 势[1-2]。CMOS 尺 寸 深 亚 微 米 化为SRAM 工作电压的不断降低提供了条件,随之功耗也在不断下降。为配合芯片设计,通常SRAM 可在几种电压条件下工作。由于传统自定时电路的限制,要保证SRAM 在这些允许电压的范围内均可工作,就需使最低电压下的Vdb达到灵敏放大器(SA)可放大电压的最小值(即灵敏度)以上。最大位线电位差与最小点位差相差较大,就会影响SRAM 在其余电压下的速度。

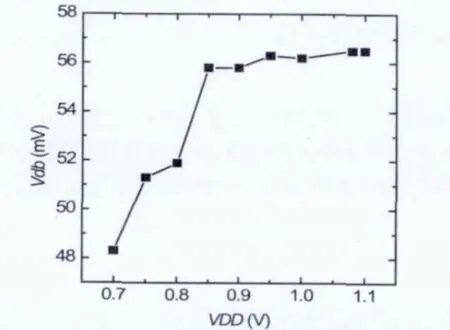

图1 更为准确的描述了这个问题。这是40nmSRAM的后仿结果。在0.7V的工作电压下,位线电位差为48mv 左右;在1.1V的工作电压下,位线电位差为57mV。为使其在正常工作电压1.08V下速度尽可能快,将SRAM的Vdb设计成最小值57mV,由图1 可以看出,在正常工作电压下Vdb满足了SRAM的工作条件,但在低压下随VDD 降低Vdb急剧下降。实际测试结果表明在最坏条件下,VDD=1V时80%的SRAM 不能工作;而VDD=0.9V时,SRAM 全部不能工作。若要增大SRAM的工作范围,就需在正常工作电压下留出足够多的Vdb余量,以保证其在预定低压下也可以工作,但这样又一定会影响SRAM 在常压下的存取速度。SRAM的最低工作电压与常压下的存取速度成为一对矛盾。

2 自定时电路

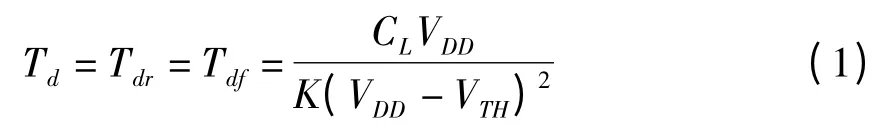

这种矛盾的产生与控制SA 使能信号的tracking path 电路密切相关。tracking path 产生图3 中的Delay Time 并控制内部时钟intclk的时钟沿翻转。而intclk翻转致使WL 关闭,灵敏放大器使能信号(SAE)有效,读出存储单元内数据。SRAM 读取时间(Access Time)主要消耗在位线放电过程中[3],即由tracking path 控制的Delay Time。过早开启SA,可能导致Vdb不够大,SA 不能准确读出数据;过晚开启SA,读周期增长,SRAM 速度受到影响。此外,SA开启时间过长也会增加功耗。因此,tracking path的设计对于实现SRAM 高速低功耗就显得尤为重要。理想tracking path 产生的延时应是电压、工艺和温度等因素的弱函数。使Vdb恒定。tracking path 电路原理示意图如图2 所示,它可以抽象为一段反相器链,其中bitcell为基本存储单元。Tracking path 中的反相器为电路提供延时。对于单个反相器,用最大导通电流的一半作为平均电流且为对称设计时,延时Td由(1)式给出:

图1 后仿SRAM的Vdb 与VDD 关系

图2 电路原理示意图

其中Tdr为上升沿延时,Tdf为下降沿延时,VDD为电源电压,VTH为晶体管阈值电压。上式两端对VDD求导得到(2)式

对于Vdb,可近似为位线放电过程,将放电时间Td和读电流(Iread)代入得(4)式

图3 SRAM 读操作时序图

其中n为反相器链中反相器的个数,Iread为读电流,VTC为存储单元传输管的阈值电压。M=nCLKN/(CBLK)为常数,对于已设计好的存储单元,VTC为恒定值。由(4)式可知,当VTH=VTC时,Vdb为以M1为斜率的VDD的一次函数。当VTH≠VTC时,平方项成为影响Vdb主因,可利用调整VTH减弱VDD对Vdb的影响。VTH大于VTC时,Vdb增大;反之,减小。另一方面,当VTH增大时,由(2)式可知,M 绝对值增大,即随VDD降低,HVT tracking path的延时增速会大于LVT的。因为恒定电压下Iread为恒定值,所以采用HVT tracking path 会使Vdb在低压下有所增加。

3 仿真结果

综合上面的讨论,对原有SRAM 做了改进,将原有tracking path 换为HVT 延时链(将LVT 晶体管改为HVT 晶体管)。单口同步SRAM 大小为36KB(X256Y4D36),采用40nm 工艺水平,其结构如图2所示,存储单元为标准六管单元。仿真采用SMIC40nm 技术文件,仿真工具为Ultrasim,仿真条件为SSCorner(nmos slow pmos slow)125℃,仿真结果如图4-5 所示。

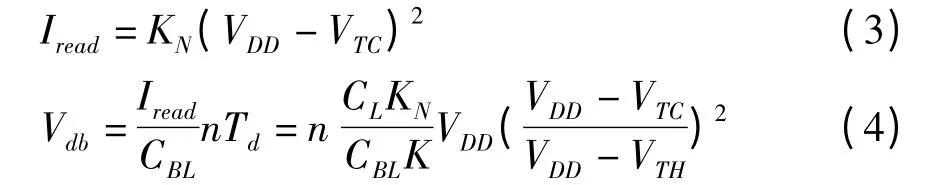

图4 中给出了高阈值(HVT)延时链与低阈值(LVT)延时链的延时跟随电压的变化图,两种延时单元在1.2V时的延时均为0.3ns。当在低压段(0.7V~1V)时,HVT 延时链的延时增速明显大于LVT 晶体管组成的延时链;当在高压段(1.1V~1.4V)时,两种延时链延时基本相同。与(2)式给出的结果基本相符。

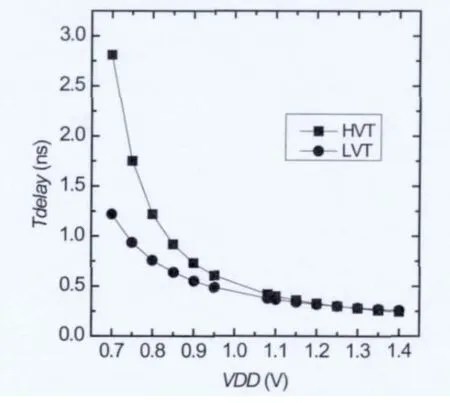

由图5 可以看出,两种SRAM 读取时间(Ta)基本相同,均随电压降低呈增大趋势。HVT SRAM 在0.7V~1.1V 下Vdb 几乎不变,波动幅度只有20%,而LVT SRAM的Vdb 波动幅度达到了147%。若保证SRAM 在0.7V时也可正常工作,需将低压下Vdb保持在50mV 以上,这种情况下HVT tracing path SRAM 常压下的性能将优于LVT的。

图4 HVT 延时链与LVT 延时链对比

图5 LVT SRAM 与HVT SRAM 对比图

4 分析总结

针对40nm 工艺下的SRAM,提出了一种tracking path 设计,将tracking 路径上的逻辑部分采用HVT 晶体管,有效增加了位线电压差而基本不影响Ta。为SRAM 在低压下能够正常工作,同时提高常压下存取速度提供了可能。

[1]Takahashi O,White M,Asano T,et al.A 4.8GHz Fully Pipelined Embedded SRAM in the Streaming Processor of a CELL Processor[J].ISSCC Session 2005(1):486-612.

[2]易兴勇,李海军,陈杰.90nm 工艺SOC 芯片多阈值低静态功耗设计[J].半导体技术,2007,32(9):812-815.

[3]Andrei Pavlov.Manoj Sachdev CMOS SRAM Circuit Design and Parametric Test in Nano-Scaled Technologies[M].Springer,2008.