IP软核测试策略及验证方法研究

2013-07-13闫淑梅邹明亮

闫淑梅,邹明亮

(长沙环保职业技术学院 湖南 长沙 410004)

IP软核测试策略及验证方法研究

闫淑梅,邹明亮

(长沙环保职业技术学院 湖南 长沙 410004)

近年来随着科技的不断进步和发展,集成电路的也在不断发展,呈现出来愈加复杂的趋势,所以芯片的设计也不断的出现了功能的增强、集成程度的提高的发展的趋势。系统芯片SoC成为当下主流的趋势下,IP核也在飞速发展。IP核也就是知识产权IP,分为软核IP、固核IP、硬核IP,其中软核IP以其灵活性高的优点,在复杂的设计中有较强的优势。但是在IP软核的实际应用中,也存在很大的困难和挑战,因此为了能更好的对IP软核进行应用,对IP核进行测试和验证具有重大的意义。文中通过对IP软核的特点进行概述,进而对IP软核的测试和验证方法进行研究,提出方案,以促进IP软核的应用及发展。

IP软核;测试;验证方法;应用特点

在SoC已成为发展主流的态势下,也面临了一系列的挑战,性能的愈加增强、规模愈加扩大、开发周期变长、设计质量难以控制等难题成为了考验。而IP核的发展则是一种有效的解决办法,而且IP软核因其灵活性较强,开发成本较低被广泛运用,但是IP软核也存在像预见性不强,来源众多,所以获得的一些IP软核质量不能保证,从而出现了对IP软核的研究,对于IP软核进行测试和验证研究以保证IP软核的质量变得尤为的有意义,文中就是对IP软核进行概述,并对IP软核进行测试、验证的研究和分析,以促进IP软核的正常、有效使用。

1 关于IP软核的概述

1.1 IP软核的含义

人们所说的IP核,也就是知识产权IP,是一种有着特定的电路功能的语言程序,IP核与集成电路的工艺没有关系,可以进行移植到不同的半导体的工艺中去,以生产集成电路芯片。而IP内核则分为3种,分别为IP软核、IP固核以及IP硬核,从而在不同的硬件实现。IP软核是用某高级语言来描述的程序,但是不需要电路元件去实现功能[1]。

1.2 IP软核的特征

首要的是IP软核要有以下基本特征:在通用性、正确性以及可移植性这3个上要有保证。通用性要求IP在特定的领域可以进行较为广泛的通用,在子功能上可以进行配置、可以进行编程。例如IP嵌入式CPU模块的通用性就展现的很好[2]。正确性要求IP可以实现严格的规范,可以遵守可重用开发的规范,IP在验证上可以达到完备,功能与测试的两项覆盖率都可以实现达到100%;同时可以覆盖IP的临界条件,提供与其相关的大流量、随机性的测试,甚至提供更详细的完备的测试环境等等。在可移植性上说的是IP可以实现网表,行为描述等等可以实现可移植的性能,在设计输入上可以在不同的平台进行展示。其次软核IP是由除了IP设计者以及IC加工商的第三方用的,而且不止有一个使用,因而IP软核还需要有以下的特征:

1)可读性。因为使用者需要对IP软核进行更近一步的应用,因而对于IP软核需要进行功能上的以及算法上的比较细致的了解,才可以达到对IP软核的正确应用,才能充分发挥IP软核的优点,因此需要提供者给出恰当的方法对设计进行描述,以供用户正确和方便的使用,同时还要采取一定的相应措施,以保证知识产权不会受到侵犯。

2)在工艺上要有一定的延展性以及工艺上的适应性。IP软核是经过多种设计、实验及优化的。在IP软核定型时要有一定的使用范围,在对于其他的设计上也要有一定的适应性,以便以后IP软核在别的领域进行应用时,不需要进行太大的调整;在工艺不断先进时,IP软核可以轻易进行小量调整甚至不用修改便可以正常的运用。

3)可测性。在IP软核被应用进不同的地方时,会进行相应的修改和调整,因而IP软核要可以在功能及性能上可以让被使用者进行相应的测试,这样就要求IP软核具有可以进行测试的性能,不但可以对IP软核进行独立的测试,同时也要满足IP软核在系统的环境中可以进行测试。

4)标准性。因为IP软核是由第三方提供的,所以为了方便的进行应用,就要要求IP软核设计的提供者对其端口有一个严格的标准的定义,以做到统一。

5)对版权要进行保护。因为要对IP软核的设计及技术进行保密,所以在设计的时候可以进行适当的、有效地加密技术,同时在工艺上实行保密的技术。

2 IP软核的测试策略

建立的测试平台和子模块的设计是一起的,首先开发测试的用例,并根据IP软核的模型对测试的环境进行调整和测试,从而对IP软核测试的测试用例和环境有所准备[3]。

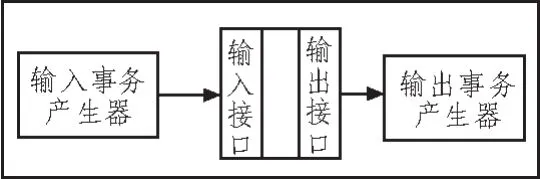

IP软核测试可以被简易的表现为如图1所示。这种测试的方式为通过输入接口进行输入,然后通过输出接口进行了检测的。在一般的数字系统中,接口产生有限的事务处理,其操作是对存储单元进行的读写操作。

图1 IP软核测试示意图Fig.1 The IP soft nuclear test schematic diagram

在设计IP软核时要对输入接口的允许类型进行设置,例如寄存器的特定时序,除了一些特定的时序外,其余的是不可以进行时序关系的改变的。在设置了输入接口类型后,要有对相应对应的次序的测试模块。要对测试模块的性能进行分析,来检测设计能否符合标准,同时也要对进行随机测验的未知情况进行分析。在对于输出的测试方面,要先有测试激励,进而根据对于IP软核的测试来断定其工作是否正常。如果想要对输出判断其是否有效,就要对数值进行检验,看其是否正确[4]。

IP软核测试包括其中一项回归测试,IP软核的回归测试是可以检测到在对错误进行修改时引发的另一个错误。回顾测试可以帮助我们在修复一个错误或者在添加新的功能的时候,已经通过测试的仍然能够做到基本的正确。

IP软核中的自动化测试在近年也越来越得到发展,首先对于测试的环境要根据情况进行建立,然后对操作流程进行配置,对测试的流程组件进行评测,从而得出质量及度量的结果,最后以对测试的结果进行评测,实现自动化,使IP软核的测试更加的有效率[5]。

3 IP软核的验证方法

对IP软核进行验证其目的就是为了通过形式多样的办法对所设计的进行检验以确保所设计的IP软核的实用性及准确性。在目前较为普遍的验证方法是模拟验证,通过对所设计的IP软核在不同层次的模拟测试,然后对输出的模拟测试的结果进行分析,进而实现对于所设计的IP软核的验证。通过对设计流程的了解和认知,IP软核的设计是有限的,其能完成的只有顶层到功能仿真层的设计,剩下的部分要通过IP软核的使用者才能够完成。好的IP软核不仅要具备良好地功能还要拥有高质量的综合的代码,这样可反映在不同工艺库中。所以说对于IP软核的验证是很复杂的,不仅要对其功能进行验证还要对设置的时序进行模拟性质的验证,以便更好地在多重验证下得到优化[6]。

功能仿真和时序仿真是组成验证的两个部分。功能级仿真可以对IP软核进行系统的优化,并且可以对系统规范得到完善。为了IP软核可以更好地进行综合,最好对此有计划,例如构制简易的逻辑图。在功能仿真时,需要通过对仿真的结果进行分析从而对IP软核进行修改,然后再次进行功能仿真,反复进行,达到对设计的愈加完善。而时序仿真则是通过采取各异的进行综合,然后验证,其同样是多次的反复验证,不断修改来优化设计。功能仿真和时序仿真的反复验证过程是一个庞大而又复杂的过程,其工作量较大,而且有些进行了重复,所以自动化的发展为其提高了效率,减少了不必要的麻烦[7]。

在对IP软核的验证还有一种是针对系统的形式验证,这种验证方式不需要数值,而是对不同的进行分析判断,看它们是否相同。所以形式验证需要有参照物进行对比,所以通常形式验证是为了对更改前后的设计进行比较以直观的了解功能是否改变。

在完成芯片时需要复杂的验证,相对于复杂的芯片验证,IP软核的验证显得较为的轻松,IP软核的错误和不足也更容易被检测出来,所以在集成之前验证IP软核是一个降低芯片验证成本的有效办法[8]。所以说在软核集成之前对其验证这项工作成为必然。因为IP软核所应用的多为重要的关键性地方,所以验证IP软核要更改错误及不足,以保证IP软核配置合理、科学,可以做到正常工作。在进行IP软核的验证时科学的、正确的验证方法可以提高验证的内容,为了做到IP软核功能上的准确,在验证上需要大量的投入对此进行完善,同时需要验证的技术和先进的工具[9]。一些IP软核的验证可以进行多次,在用户使用中也可以进行验证。

4 结束语

近些年来由于芯片技术及应用的飞速发展,使得芯片的功能不断地强大,成本也逐渐变低,而且使用的越来越灵活,在这之中IP软核也得到了快速的发展,种类也在不断地丰富,这样也促进了IP软核的更新换代,但是在IP软核推陈出新的过程中,对于IP软核测试及验证却不能有丝毫的松懈,可以说IP软核的好坏与否一半在与前期的设计和研究,另一半就决定于后期的测试和验证的确认和完善阶段的运行,所以IP软核的测试和验证成为了IP软核是否可以成功的关键因素。而IP软核的发展及其测试和验证也将成为我国在此领域一个新的发展机遇与考验。

[1]赵尔宁.基于SoC的可复用IP软核设计方法的研究[D].河南:解放军信息工程大学,2005.

[2]李丽.集成电路设计方法及IP设计技术的研究[D].安徽:合肥工业大学,2002.

[3]Louis S,Luciang L,Grint M.集成电路系统设计、验证与测试[M].陈力颖,王猛,译.北京:科学出版社,2008.

[4]William L K.硬件设计验证,基于模拟与形式的方法[M].王维维译.北京:机械工业出版社,2007.

[5]简贵胄,葛宁,冯重熙.静态时序分析方法的基本原理和应用[J].计算机工程与应用,2002,15(7):18-22.

JIAN Gui-zhou,GE Ning,FENG Chong-xi.Static timing analysis method of the basic principle and application[J].Computer engineering and application,2002,15(7):18-22.

[6]杜慧敏,曾泽仓,韩俊刚,等.构造特定领域应用芯片验证环境的方法讨论[J].微电子学与计算机,2004,21(6):185-189.

DU Hui-min,ZENG Ze-cang,HAN Jun-gang,et al.Structure specific application of chip verification environment discussed methods[J].Microelectronics and Computer,2004,21(6):185-189.

[7]安建峰,樊晓娅.龙腾CI微处理器的功能验证[J].计算机工程与应用,2005,12(2):33-35.

AN Jian-feng,FAN Xiao-ya.Longteng CI microprocessor functiontest[J].ComputerEngineeringandApplication,2005,12(2):33-35.

[8]李宥谋,韩俊刚.SDH芯片功能验证平台的设计与实现[J].光通信研究,2005,130(4):61-63.

LI You-mou,HAN Jun-gang.SDH chip function design and realization of the verification platform[J].Study on Coptical Communications,2005,130(4):61-63.

[9]刘路路.基于非完全确定有限状态机模型的控制器综合的形式验证[D].安徽:安徽大学,2006.

IP soft-core test strategy and verification methods

YAN Shu-mei,ZOU Ming-liang

(Changsha Environmental Protection Vocational College, Changsha 410004, China)

As technology continues to progress and development in recent years,integrated circuits are constantly development of present increasingly complex trends,chip design enhancements constantly improve the degree of integration of the development trend.System-on-chip SoC and become the mainstream trend,IP core is also developing rapidly.IP core intellectual property IP,divided into soft-core IP,solid-core IP,hard IP,soft core IP advantage of its high flexibility in the complexity of the design has a strong advantage.But in the practical application of IP soft core,there are also a lot of difficulties and challenges, IP soft core application, testing and validation of the IP core of great significance.This paper an overview of the characteristics of the IP soft-core,and then on the IP soft-core testing and verification methods to study a proposal to promote the application and development of IP soft core.

IP soft core; test; authentication method; application features

TP393.08

A

1674-6236(2013)04-0098-03

2012-10-15稿件编号201210104

闫淑梅(1974—),女,湖南衡阳人,硕士,讲师。研究方向:核测试与核测控。