基于DSP的高速动车组车内噪声测试系统设计

2013-07-12辛光伍川辉

辛光,伍川辉

(西南交通大学机械工程学院,四川成都 610031)

基于DSP的高速动车组车内噪声测试系统设计

辛光,伍川辉

(西南交通大学机械工程学院,四川成都 610031)

为满足高速动车组车内噪声试验的需求,设计一种基于DSP的噪声测试系统,对测试系统的设计方案以及软硬件实现进行介绍。系统由控制部分和运算部分组成:控制部分以高性能、低功耗的基于ARM Cortex-M3内核的微控制器STM32F103ZET6为核心,扩展了A/D采集模块、NAND Flash存储模块以及蓝牙通信模块;运算部分以TI公司的低功耗DSP芯片TMS320VC5509A作为核心,负责对采集的噪声数据进行实时处理,并把结果交给ARM发送给上位机,以实现对试验效果的实时观察;ARM与DSP通过双端口RAM相连接,使得两种处理器间的频率差异得到解决并能有效地实现数据交换。实验证明:基于DSP的噪声测试系统能很好地满足高速动车组车内噪声试验对噪声数据采集和实时处理的需求。

测试系统;DSP;ARM Cortex-M3内核;高速动车组;车内噪声;双口RAM

0 引言

近年来我国的高速铁路事业迅速发展,在提高列车运行速度的同时,带来的噪声污染也在加剧,噪声已经成为了评价高速铁路对环境影响的主要指标之一[1-2]。随着人们生活水平的提高,对环境重视程度也不断加大,车内噪声会直接影响到乘客乘坐列车的舒适度[3]。列车噪声的测试和研究对噪声来源、分布以及声振关系的明确有着重要意义[4],也为优化动车组的设计提供了依据。针对传统的基于工控机的噪声测试系统存在可扩展性差、体积大安装不方便以及信号线长抗干扰性差等缺点,本系统介绍基于DSP的噪声测试系统,ARM单元负责数据的采集、存储、与上位机通信,能实现多通道采样和大容量数据存储,和上位机间的通信采用蓝牙方式;DSP单元负责数据处理,两个单元使用双口RAM的中断方式进行连接,保证了数据交换的实时性。在处理器选取方面,均选用低功耗、高性能芯片,电路板做好抗干扰设计,使得系统能适应动车组运行过程中的特殊试验环境。

1 测试系统总体方案

为满足对噪声数据的采样和实时处理的要求,噪声测试系统采用DSP与ARM的双CPU构架。控制部分由STM32F103ZET6作为主控芯片,通过SPI接口与A/D采集模块相连,微控制器片内自带的定时器设定定时中断,控制A/D芯片的采样频率,A/D模块对经调理过后的传声器信号采样转换。运算部分由TMS320VC5509A作为主处理器,STM32将采集上来的数据写入双口RAM中并写相应的地址用以触发DSP端的中断,双口RAM以中断方式通知DSP取数据。DSP在完成噪声算法过后,将结果写入双口RAM中,也同样的写相应的地址触发ARM端的中断,ARM在接到中断后读取处理好的结果并由蓝牙发送给上位机,从而完成对试验的实时监测。噪声的原始数据储存于本地NAND Flash中,用以后续的分析处理。系统总体框图如图1所示。

图1 系统总体框图

2 硬件设计

2.1 芯片选型

STM32F103ZET6为意法半导体(ST)公司推出的基于ARM Cortex-M3内核的一款高性能芯片,它的封装为LQFP144脚,最高的工作频率能达到72MHz,片上集成的存储器有512K的Flash存储器和64K的SRAM存储器[5]。芯片有丰富的外设:多达11个定时器,以及CAN、SDIO、SPI、USART、USB等多达13个通信接口。拥有可变静态存储控制器FSMC,能够方便的与SRAM、NAND Flash和NOR Flash等连接,用以外扩存储器。片内配置独立看门狗和窗口看门狗,使得系统运行得以保障。相比ARM7,Cortex-M3使用单一的Thumb-2指令集[6],使得代码密度与处理性能都兼顾并且易于使用。在高度集成外设的同时也兼顾低功耗,STM32F103ZET6支持3种低功耗模式,可以对所需要使用的时钟进行单独的使能控制,以优化功耗。在具有高性能的同时还有低成本的和易开发的优点,使其具有极高的性价比和很高的应用价值。

TMS320VC5509A是TI公司推出的继C54x后的新型产品[7],C55x与C54x源代码兼容。相比C54x,C55x拥有更为卓越的性能,核心频率从C54x的120MHz提高到了300MHz,性能提高了5倍,C55x的功耗降低到0.05MW/MIPS。片内配置6通道直接存储器存取控制器DMA,拥有外部存储器接口EMIF,能够与EPROM、SRAM等异步存储器以及同步DRAM进行无缝连接。

2.2 数据采集模块

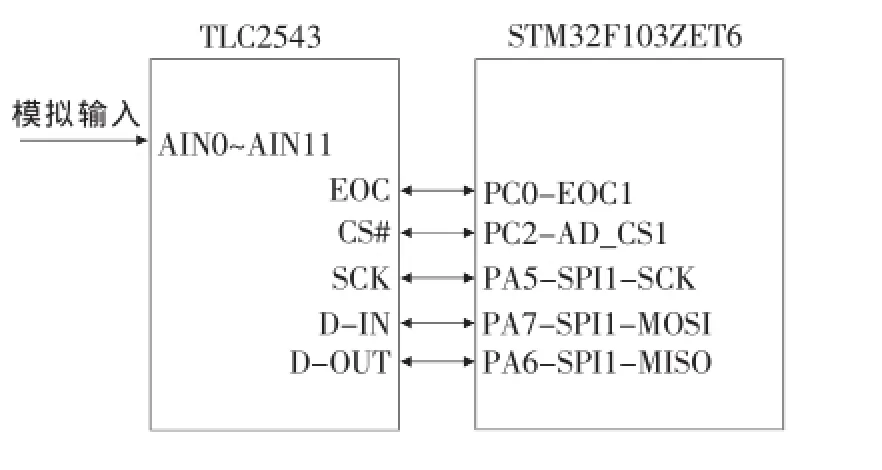

系统选用12位逐次比较型A/D转换芯片TLC2543。TLC2543最高的采样频率能达到66kS/s,能提供11个采样通道的输入,本设计中使用2个通道采集噪声数据,能够满足系统需求。TLC2543采用4线制串行接口,能与微控制器的SPI总线接口无缝连接,STM32通过两个SPI控制器可连接两片TLC2543以获得22个采样通道。微控制器与A/D芯片连接如图2所示。

图2 微控制器与A/D芯片的连接图

2.3 蓝牙通信模块

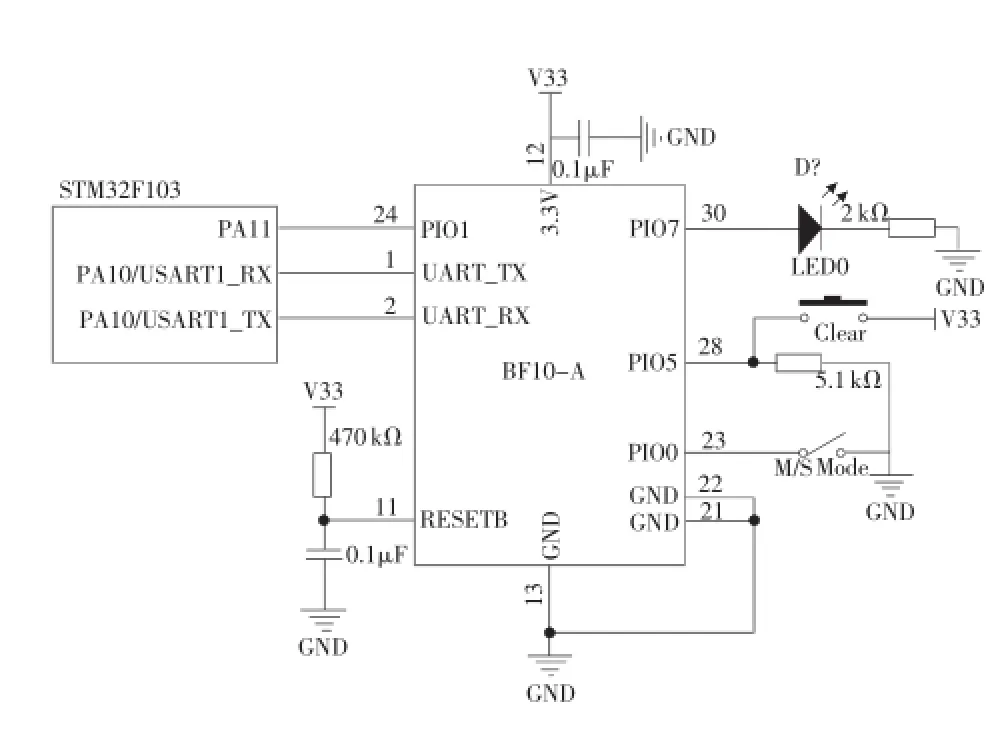

下位机与上位机之间的通信运用蓝牙方式,系统选用蓝牙模块BF10-A,该模块基于BlueCore4-Ext芯片,完全兼容蓝牙2.0规范。支持Uart接口,用来和微控制器连接。可以选择的配置为主/从模块,使用AT指令方式,可方便地修改模块的蓝牙名称、配对码、及波特率等。蓝牙模块与STM32的连接如图3所示,其中BF10-A的PIO1口为蓝牙连接状态脚,当连接成功时为高电平,接STM32的通用I/O以便设备监控连接状态。

2.4 ARM与DSP连接电路

图3 蓝牙模块连接图

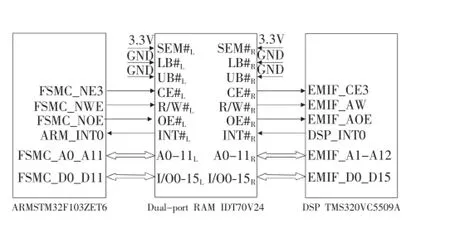

图4 ARM与DSP双口RAM通信方式连接图

测试系统需要实时地进行噪声算法,ARM把采集上来的数据交由DSP处理,DSP再将处理结果送回ARM。ARM与DSP使用较多的通信方式主要有主机接口(HPI)方式、总线方式以及双口RAM方式。HPI主机接口,是TI高性能DSP上配置的与主机进行通信的片内外设。主机是HPI的主控者,HPI作为一个外设与主机相连[8]。这种方式连线简单、体积小,但逻辑比较复杂,增加了应用的难度。总线方式一般采用I2C、SPI等串行接口,其硬件连接简单,若片上有I2C、SPI外设,则编程就会比较简单,作为串行传输,适合少量数据交换,稳定性和传输速率不高。系统采用双口RAM方式实现处理器间的数据交换,逻辑简单并且能很好解决ARM与DSP间频率匹配问题[9]。

双口RAM选用IDT公司的IDT70V24双口RAM,大小为4KB,位宽为16b,工作电压3.3V,最快存取时间25ns,满足数据的高速存储。它可以左、右两个端口同时读写数据,每个端口有属于自己的独立数据线、地址线和控制信号线。为避免左右端口控制器因占用RAM存储区而产生竞争,双口RAM提供了硬件仲裁、中断仲裁和信号灯仲裁3种仲裁方式,与BUSY、SEM和INT 3个左右逻辑交互接口。本系统选择中断仲裁方式,具体实现过程为:双口RAM的两个特定的地址单元被用作“邮箱”,通过对特定地址单元的写入和读取,实现对RAM占用信息传递。当右侧端口在右侧信息位FFE写入数据时,左侧中断INTL被触发,要清这个中断,左侧端口需读这个信息位;同样当左侧端口在左侧信息位FFF写入数据时,右侧中断INTR被触发,右侧端口通过读这个信息位清中断。ARM与DSP双口RAM通信方式连接如图4所示。

3 软件设计

3.1 数据采集程序设计

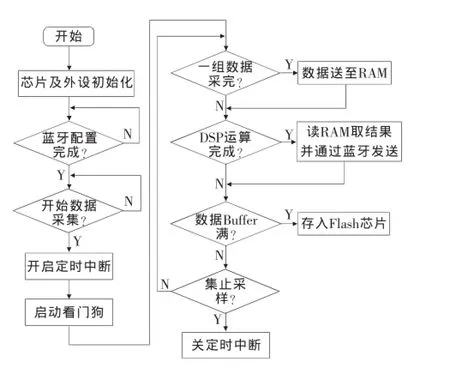

ARM系统的软件编程使用的编译环境为Keil MDK,有强大的仿真能力,能观察外设的运行状况并且提供虚拟逻辑分析仪等功能,这些特性使调试很方便。系统的数据采集部分由ARM芯片控制,STM32自带通用定时器(TIMx),通过对定时器的配置,使其产生定时中断,以中断来触发采样,就能通过设置定时中断的频率来确定采样频率。STM32通过SPI口连接LTC2543,并且把控制字通过DATA INPUT引脚传入TLC2543来控制采样,在每个定时中断向写TLC2543命令字以采样。为了减少CPU开销,配置STM32片内的DMA来搬运采样数据,采样数据送双口RAM通知DSP完数据处理算法运算,原始数据存入一个Buffer中,待Buffer满后写入NAND Flash保存,以备后续的详细数据处理。数据采集程序放在TIM2定时器的中断服务子程序中,完成对通道的扫描采样和数据保存。ARM部分主程序流程如图5所示。

图5 数据采集主程序流程图

3.2 DSP运算程序设计

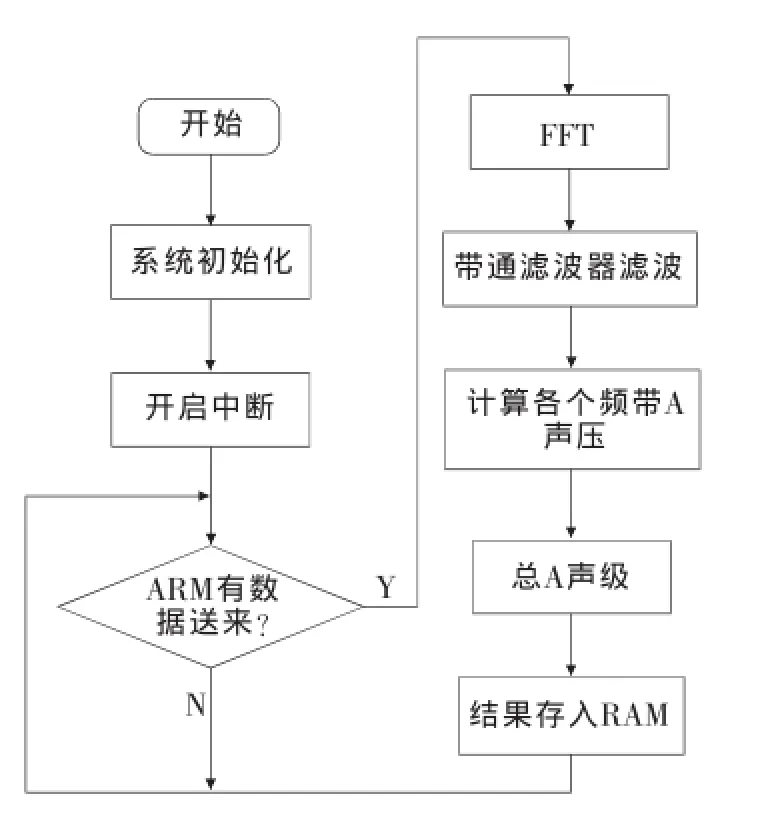

DSP的程序流程如图6所示。

图6 DSP程序流程图

DSP主要是进行数据处理,完成特定的噪声算法,当ARM有数据采集好了送来时,会写双口RAM相应的“邮箱”,此时会触发双口RAM另一侧的中断信号,DSP在接到中断时,就从RAM中读取数据,并开始数据的实时处理,把结果送回双口RAM中通知另一侧的ARM取结果,ARM取到结果后就通过蓝牙方式发送给上位机,这样试验过程就能随时观察试验的效果。其程序流程就是一个主循环,判断中断标志来确认是否进行噪声算法。

4 试验结果

系统上位机实时监控程序,通过蓝牙接收下位机运算结果,达到在试验过程中观察结果的目的。监控程序完成试验数据采集和储存,主要获得的参数包括1/3倍频程、A计权声级等。图7所示为监控程序显示的列车某测点的1/3倍频程谱图,图8所示为后续分析得出的列车某测点在不同速度下的噪声谱图。

图7 列车某测点的1/3倍频程谱图

图8 列车某测点在不同速度下的噪声谱图

5 结束语

基于DSP的高速动车组车内噪声测试系统,能够实现噪声数据的实时采集与分析,其高性能、低功耗特性满足动车运行环境下的测试需求,对噪声的检测提供了可行的方案,对噪声研究和评价起到重要作用。系统结构灵活,运行稳定,有很好的应用价值。

[1]孙大新,高亮.高速铁路轮轨噪声及其控制措施[J].中国安全科学学报,2005(11):88-90.

[2]周君.高速铁路建设过程中如何治理噪声污染的研究[J].铁道工程学报,2001(1):28-30.

[3]范蓉平,孟光,孙旭,等.基于心理声学响度分析的高速列车车内噪声评价[J].振动与冲击,2005(5):46-48.

[4]邢淑梅,刘岩,张晓排.高速铁路动车组噪声测试与分析[J].噪声与振动控制,2009(3):79-81.

[5]王永虹,徐炜,郝立平.STM32系列ARM Cortex-M3微控制器原理与实践[M].北京:北京航天航空大学出版社,2008(7):47-56.

[6]Yiu J.ARM Cortex-M 3权威指南[M].北京:北京航空航天大学出版社,2009:28-29.

[7]汪春梅,孙洪波.TMS320VC55X DSP原理及应用[M].3版.北京:电子工业出版社,2011:10-59.

[8]胡庆钟,李小刚,吴钰淳.TMS320C55x DSP原理、应用和设计[M].北京:机械工业出版社,2006(1):200-203.

[9]翁奇财,王维.嵌入式系统中CPU之间通信方式的比较[J].声学与电子工程,2008(4):38-39.

High-speed EMUs interior noise test system based on DSP

XIN Guang,WU Chuan-hui

(School of Mechanical Engineering,Southwest Jiaotong University,Chengdu 610031,China)

In order to meet the demand of interior noise tests for high-speed EMUs,a DSP-based noise test system was designed.The system consists of the control part and the computation section.High-performance and low power consumption control part takes ARM Cortex-M3 corebased microcontrollers STM32F103ZET6 as the core and extends A/D acquisition module,NAND Flash memory module,and Bluetooth communication module.Computing part takes TI’s lowpower DSP chips TMS320VC5509A as the core and it is responsible for collecting the noise data in real-time processing,and sending the results to the host computer through the ARM in order to achieve real-time observation of the test results.ARM and DSP were connected with the dualport RAM,which made the frequency differences between two processors resolved with effective data exchange.Experimental results show that the noise test system based on DSP can meet the demands of noise data acquisition and real-time processing for high-speed EMUs interior noise test.

test system;DSP;ARM Cortex-M3 corebased;high-speed EMUs;vehicle interior noise;dual-port RAM

TP216+.2;U292.91+4;TB535;TP274+.2

A

1674-5124(2013)03-0084-04

2012-05-11;

:2012-07-20

“十一五”国家科技支撑计划项目(2009BAG12A01)作者简介:辛光(1986-),男,四川成都市人,硕士研究生,专业方向为自动化测试技术与PC仪器。