滑动相关法扩频同步系统设计及FPGA实现

2013-07-06杨自恒

郑 东,孙 阳,杨自恒

(黑龙江大学 电子工程学院,哈尔滨 150080)

0 引 言

通信系统是将信息从一个地点传送到另外一个地点,它在我们的生活中发挥着至关重要的作用。软件无线电(Software Radio)技术是20世纪末提出的一种设计思想,被美国军方所使用,21世纪才逐渐开始民营化,它突破了传统电台以硬件为核心的设计模式,其核心是系统可在线升级软件来提高系统性能[1]或者适应不同的通信体制。这种全新的思想使通信中的无线电台可以最大限度满足互联互通的需求。简单说,软件无线电就是使AD和DA尽可能靠近射频前端(RF),将模拟信号转换成数字信号,然后在软件上编程实现其功能,这样就将原来用硬件来实现的部分,现在主要靠软件来实现,并且能在通用的硬件平台上通过加载不同的软件模块来实现不同的功能。

本系统采用的扩频方式为当今应用较广泛的直接序列扩频(DSSS),它也是软件无线电中的核心技术。它是将发送的数据用伪随机码(PN码)扩展到一个很宽的频谱上,在接收端,采用和发送端同频同相的伪随机码对接收到的数据进行解扩,从而恢复出原始的数据。其中如何找到与发送端同频同相的伪随机码是最关键的步骤,它用到一个关键的技术:码同步。同步是通信系统中必不可少的的部分,特别是在接收端,同步的好坏决定了接收端的性能。

1 码同步算法及仿真

码同步包括两部分:码捕获和码跟踪。

1.1 码捕获

码捕获又称为粗同步,就是大致使本地产生的伪随机码与接收端接收到的扩频码的相位和频率基本相同,使发射机与接收机的伪码的相位在半个最小码片宽度内。跟踪也可以称为精同步,它是在捕获达到指定目标的基础上,使收发信机两端的伪随机码的相位进一步减少,却使接收机端的伪码与接收到的发射机端的伪码在相位上保证在预期的误差范围内,可在允许的范围内变动[2]。

扩频序列同步的第一步便是为本地扩频序列寻找一个相位,使本地扩频序列与发送扩频序列相位差<1/2个码元,这一步称为捕获(又称粗同步)结构框图见图1。捕获部分采用的是分段相关捕获法,包括乘法器、积分累加器、门限判决和码发生器4部分。相关运算实质上是求两个函数的相似性,在离散函数求相关的过程中,相位相同的PN码序列具有极好的相似性,公式如下:

由式(1)可见,一次相关运算是2个序列对应点相乘后把结果再求和记到N次的时候(N是伪码的周期),进行一次门限判决。如果积分器的值小于门限值,则通过改变码发生器的频率来调整电路,控制本地伪码发生器延时一个码元,达到本地伪随机码滑动的目的。重复以上操作,直到积分累加器输出值大于判决门限为止,则相位捕获完成[3]。

图1 捕获结构图Fig.1 Structure of capture

1.2 码跟踪

同步的第二步是跟踪(又称精同步),它是通过更加精准的运算来进一步缩小本地伪随机序列与发送端的扩频码之间的相位误差,一般来说,通过跟踪电路以后,能够使两码元之间的误差<1/10码元的时间。结构框图见图2。

在本系统中码跟踪采用的是延迟锁定环(DLL)的跟踪方法[4]。在码跟踪环路中,先将通过解调以后的I路和Q路的扩频序列分别与本地伪随机码的超前、滞后码进行相关,再进行数据累加和包络检测,分别求出超前支路和滞后支路的值,然后将其送入到延迟锁相环的误差检测器中,根据伪随机码的基本特性可以求出两路超前滞后码的误差,该误差经过码环路滤波器后控制本地伪随机码的码产生时钟,伪随机码的超前和滞后2个支路都需要计算累加值,可以采用与捕获支路相同的分段积分相关法[5]。

图2 跟踪结构图Fig.2 Structure of tracking

误差检测器采用的算法公式如下:

归一化的超前包络减去滞后包络,是为了消除幅度的敏感性。对于1/2基码的相关器间距来说,当输入误差<1.5个基码的范围是会产生良好的跟踪误差[6]。

环路滤波器采用二阶环路,它的时域模型为:

从而可得到它的时域的差分方程为:

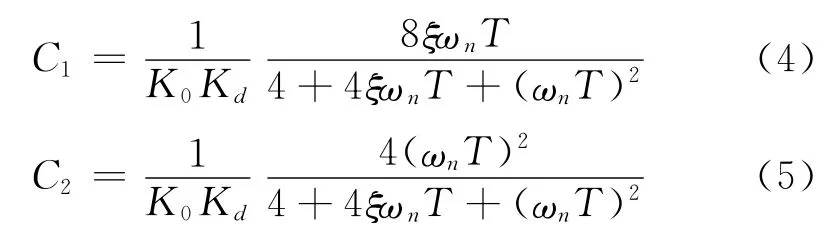

式中Xk是环路滤波器的输入值,即鉴相器输出的相位误差值;Yk是环路滤波器的输出值;C1和C2是环路滤波器的系数,它们的确定是整个环路滤波的重点和难点,决定了整个环路的性能。其中C1和C2的计算式[7]如下:

由式(4)、式(5)可见,要想求出环路滤波器的系数C1和C2,就需要确定环路的阻尼系数ξ,环路的自然角频率ωn,以及环路的增益K0Kd。计算出的C1和C2在实际的工程中是不能直接使用的,需要在实际的调试过程中对其作适当调整或优化。总之,系数C1和C2值的大小决定了整个环路的跟踪性能,需要依据环路的特性来取值。其中,C2决定了环路的捕捉带的大小,而C2主要决定了环路的捕获速度和长期跟踪速度,如果C2较大时,经过很长的时间环路才能成功的收敛。所以在实际工程中,仍需要根据工程的需要来选取合适的C1和C2的值。

1.3 码同步的Matlab仿真

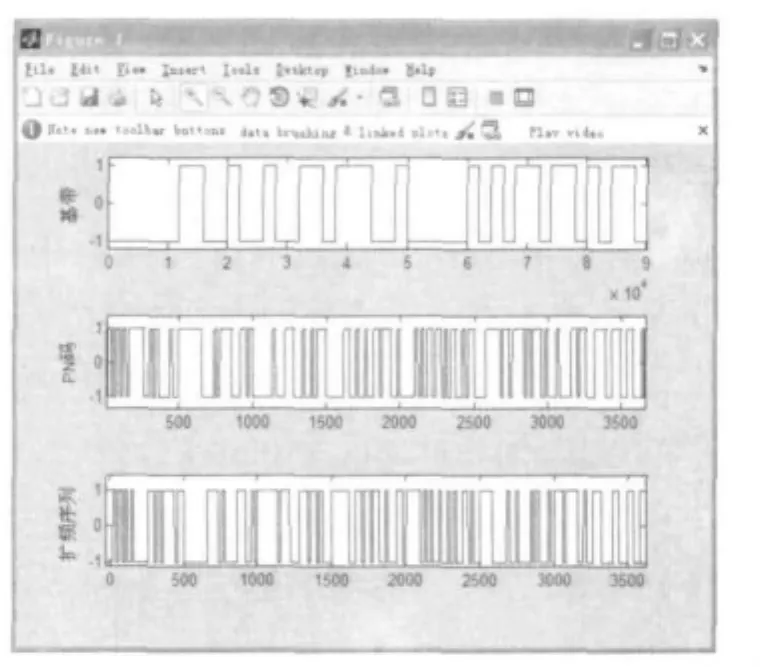

用Matlab对捕获和跟踪进行仿真,设Pn码频率为3MHz,周期为1024个bit,基带信号的频率为30kHz,则其直接扩频序列见图3。

图3 直接扩频序列图Fig.3 Simulation of Matlab for direct sequence spread spectrum

捕获部分的Maltab仿真见图4。判定当相关捕获的结果>2000时即为捕获成功,进入跟踪阶段。

跟踪部分的Matlab仿真见图5,当误差检测器输出的相位差接近0时,环路滤波器输出也为0,则跟踪成功,从而得到了发送的原始基带信号,验证了码同步环路的可行性。这里的码环路滤波器的主要系数C1=1;C2=10。

2 系统的FPGA实现

本次设计采用ALTERA公司cyclone系列的EP3C25Q240C8N芯片,在Quartus中进行编译后下载到板子上,在逻辑分析仪下进行调试及仿真。

2.1 伪码捕获在FPGA上的实现

码捕获部分的FPGA实现包括3位移位寄存器、NCO控制选择器、捕获环路3部分。其中3位移位寄存器产生本地PN码的当前码、滞后码、超前码3路信号。3位的移位寄存器的RTL电路见图6,其中E输出为超前码,P输出为当前码,L输出为滞后码,通过超前码与滞后码和接收到的信号的相关值的差来判断接收到的信号中PN码与本地PN码的相位情况。其中3位移位寄存器产生的信号通过quartus II的信号仿真器见图7。由图7可见超前码比当前码超前1/2个码片,当前码比滞后码超前1/2个码片。

捕获环路的FPGA实现模块见图8,其中的G为捕获标志位当其为1时表示环路已捕获到接收到的信号,也就是说接收机中的伪码与发射机发射过来的信号中的伪码在相位上相差1/2个码片。其输出管脚G为0时表示捕获环路正在捕获中。其FPGA实现可在其自身自带的信号仿真器上观测,其结果见图9。

2.2 码跟踪的FPGA实现

码跟踪部分的FPGA实现包括3位移位寄存器模块、跟踪环路模块、码NCO控制器模块。

3位移位寄存器模块如2.1中的捕获部分的3位移位寄存器模块一样也是产生超前码、当前码、滞后码3路信号。码NCO控制器模块也如2.1中的捕获部分的码NCO控制模块一样,同样是通过控制字来改变PN码产生器的控制时钟,来调整本地PN码与接收到的信号中的PN码的相位。

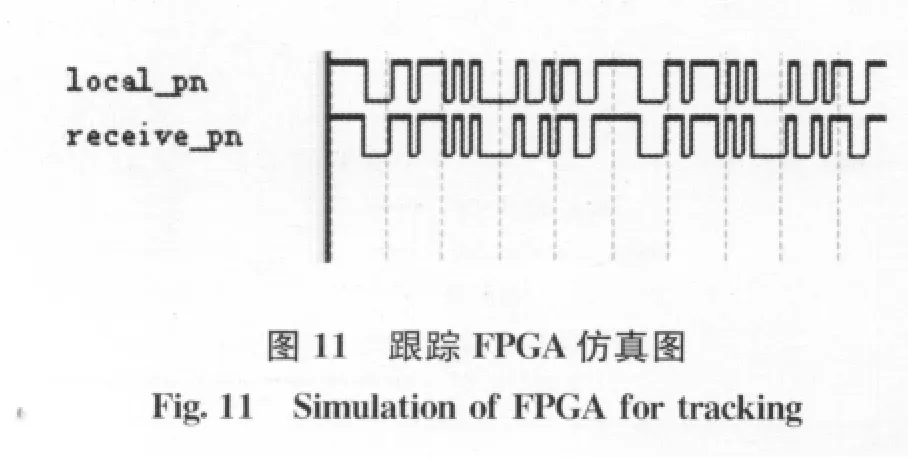

码跟踪环路的FPGA模块见图10,其中包括相关器、包络检测器、误差检测器、码环滤波器。其输出为码环滤波器的输出值,它反馈到PN码产生器来短时间改变PN码速率,使本地PN码的相位与接收到的信号中的PN码的相位相同。跟踪上的FPGA仿真见图11。

3 结 论

捕获是利用相关计算差的方法,使发射端伪码和本地的伪码相位的初始同步。本文采用的捕获方法是多积分滑动相关法,此方法是逐步改变接收机PN码的相位。对相关积分和的峰值的判决是研究捕获中的难点,良好的判决检测方法可获得较高的检测概率和较低的误判率,由于单积分时间检测的平均捕获时间要高于多积分时间检测,并且误判率较高,所以结合系统的参数和性能要求采用多积分滑动相关法,提出了一种改进的分段多积分滑动相关法,并给出了具体的实现方案。

码跟踪环的重点在于锁相技术,在此基础上介绍了延迟锁定环技术,研究并在实际应用中使用的全时间非相干延迟锁定环,给出了其环路的具体实现方法,完成了二阶环路的硬件设计并实现。在跟踪环路的基本实现过程上,提出了一种简化的环路设计方法,其优势在于跟踪的时间短,随之带来的负面因素是抗噪声能力低,这方面需要进一步研究。利用直接数字频率合成技术来实现码NCO模块,分析了其频率漂移的基本原因并给出了解决方法,最后将整个码同步系统在FPGA上实现并做了实际的分析。

本码同步系统采用软件无线电技术并在FPGA上实现其可移植性、再升级性较强。与此同时,本文的实现主要是自主设计,所以系统的安全性和保密性较强,具有广阔地应用前景。

[1]Wu DingXue,Fan WenPing.A new method of modeling and simulation for DSSS communication systems based on software radio[C]//IEEE International Symposium on Knowledge Acquisition and Modeling Working,2008:765-768.

[2]阮朝阳,基于EPF10K200SRC240芯片的全数字DSSS处理器ASIC设计——数据捕获、同步及解扩部分[D].成都:电子科技大学.

[3]李 涛,孙志国,郭黎利.扩频通信系统中扩频码并_串快速捕获的数字化实现 [J].应用科技,2004,31(1):2-3.

[4]Hui Du,Qun Ding,Ziheng Yang.The research of DLL used in DS spread spectrun communication system[A].International Conference on Instrumentation,Measurement,Computer,Communication and Control[C].2011:696-699.

[5]许 刚,黄国荣,彭兴钊,等.GPS软件接收机相关技术研究 [J].导弹与航天运载技术,2012,(4):47-49.

[6]金富钊,GPS中的环路跟踪算法的研究 [D].西安:西安电子科技大学,2006.

[7]周 帆.一种GPS软件接收机的同步算法研究与仿真[J].弹箭与制导学报,2012,32(3):180-181.