多通道数据记录装置设计及实现

2013-07-05单彦虎卫一然甄国涌

单彦虎,卫一然, 甄国涌

(中北大学仪器科学与动态测试教育部重点实验室电子测试技术重点实验室,山西 太原 030051)

多通道数据记录装置设计及实现

单彦虎,卫一然, 甄国涌

(中北大学仪器科学与动态测试教育部重点实验室电子测试技术重点实验室,山西 太原 030051)

介绍了一种基于FPG A的多路采集存储电路设计。该装置以FPG A为主控芯片,控制模拟开关对导弹引信在高速动态交会试验中发射飞行过程中引信的多普勒信号、点火信号以及引信保障执行机构等的工作状况进行弹载实时采集,并通过THS1040模数转换器,将模拟信号转换成数字信号存入F LASH存储器。发射完成后,上位机通过USB接口将数据上传至计算机进行分解、绘图。经多次验证,证明该装置可以准确地对信号进行采集、存储,达到了设计目标。

FPG A;多通道;信号采集;模数转换

当代数字信号处理技术飞速发展,数据采集存储作为信号处理过程的一项关键技术,已经广泛应用于雷达、声纳、瞬态信号测试、无线探伤等领域。数据采集速率和精度依据环境条件的不同而有所差异。一般情况下,如果采集速率较低则数据采集和上传至计算机进行处理可以同时进行[1]。但在采集源移动的情况下,就需要设备同时具有采集和存储功能,以便事后对数据进行处理分析。根据实际需要,研发了一种蓄电池供电工作、体积小、功耗低、存储量大的记录装置。

该记录装置采用FPGA构建多路数据采集存储系统核心控制电路,用来记录导弹引信在高速动态交会试验中发射飞行过程中引信的多普勒信号、点火信号以及引信保障执行机构等的工作状况。发射完成后可以回收再现飞行数据,为及时查找可能发生故障的原因,提供有效的测试手段,为产品设计与问题故障分析提供依据。记录装置共采集18路信号,其中6路采样率为300 kS/s,12路采样率为25 kS/s。

1 装置结构及工作原理

该采集存储装置主要包括信号输入接口电路、采集电路、中心逻辑控制电路、存储接口电路及USB读数接口电路。

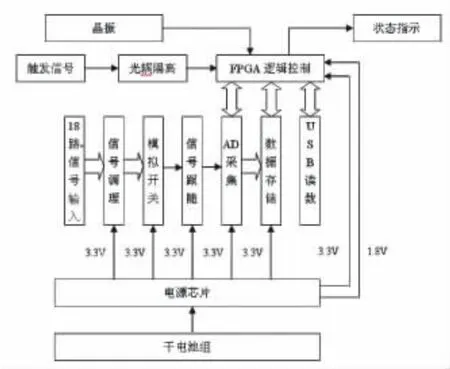

6路高速待采信号和12路低速待采信号经过信号输入接口进入记录装置后先经过运放的分压处理,由大幅值信号统一调理为0~2 V的信号,然后经过一个模拟开关,这时高速模拟开关将自动切换到需要采样的通道,经过运放跟随后送往AD转换器进行转换,将转换后的数据送往中心逻辑单元进行数据中转,包括对数据进行编帧等,数据整理完成后送往FLASH进行数据存储,试验完成后通过USB将数据导出。其整体设计框图如图1所示。

图1 整体设计框图

2 采集模块设计

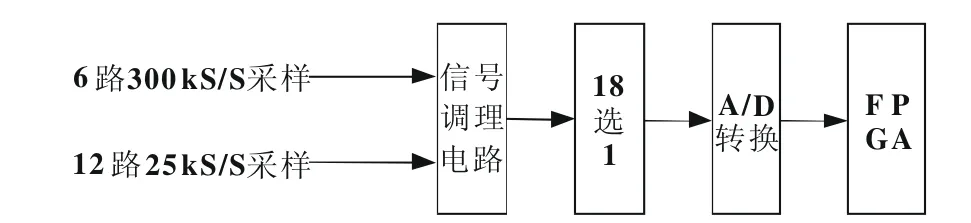

18路模拟信号经过运算放大器调理后,进入模拟开关ADG732,FPGA控制ADG732按照一定的顺序进行地址线切换,将18路信号有序的输入模数转换器THS1040进行采样,采样长度为10位,前两位为有效数据标志位[2]。之后数据就进入FPGA进行编帧、打包。采集过程框图如图2所示。

图2 采集过程框图

2.1 接口电路设计

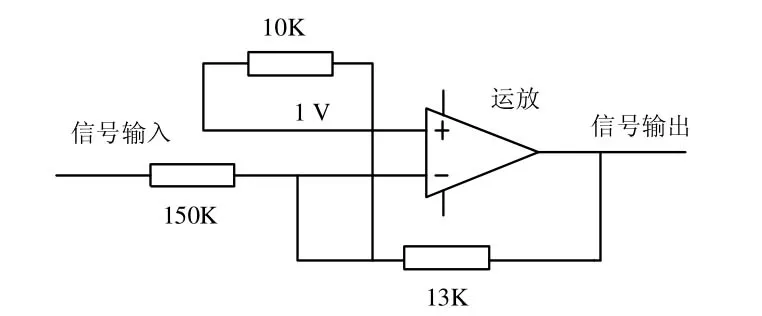

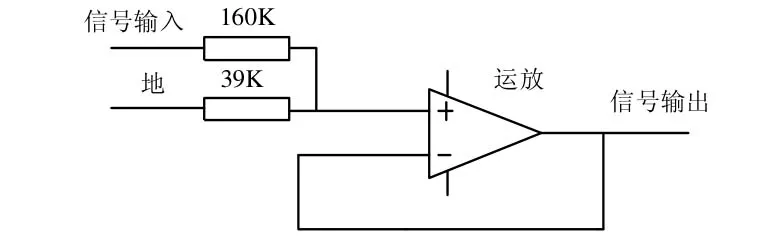

为了保障进入模拟开关前信号的完整性和准确性,设计中采用具有rail to rail特性的运算放大器OPA4340进行信号调理,在提高了信号输入阻抗的同时也减小了调理后信号的输出阻抗。信号经接口电路的调整由大幅值信号统一的变为0~2 V的低压信号,方便后续电路的采集。图3为-10~+10 V、-30~+30 V信号接口电路,图4为0~+40 V、0~+10 V信号的接口电路。

图3 -10~+10 V和-30~+30 V接口电路

图4 0~+40 V和0~+10 V接口电路

2.2 多路模拟开关设计

装置设计选用模拟开关ADG732对18路信号进行一定的顺序切换。该开关工作电压范围宽(1.8~5.5 V),导通电阻小,具有轨对轨特性,开关切换时间短(30 ns),封装小[2]。

由于18路待采信号的频率有所不同,其中6路高速通道,每路采样率300 kS/s;12路低速通道,每路采样率25 kS/s。为了满足不同信号采样率的要求,同时尽可能减少总的数据量,设计采用如下的帧格式。

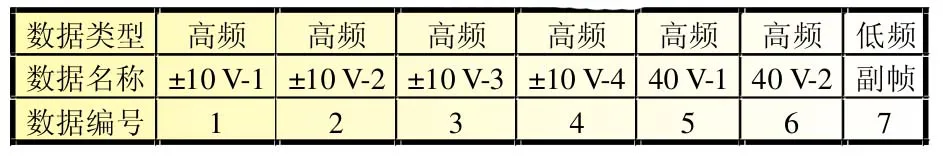

数据的编帧采取主副帧结构,既主帧中最后一个字节为副帧中的数据,当主帧每运行完一次,主帧中的副帧数据进行更新,继续重复运行主帧数据,当副帧中的数据全部被更新完后,结束全部一整帧数据,加入帧计数和帧标记。如表1和2分别为数据主帧结构和副帧结构。

表1 数据主帧结构

表2 数据匐帧结构

主帧中信号的采样率为2.068 965 5MS/s,按数据编号1到7顺序采集,每一路采样率为:2.068 965 5÷7≈0.295 566 5 MS/s=295.566 5 kS/s,即高频信号的采样率为295.566 5 kS/s。由于每次采集完所有高频信号后采集一次低频信号,所以12路低频信号中的每一路采样率为:295.566 5 kS/s÷12≈24.63 kS/s,即低频信号的采样率为24.63 kS/s。

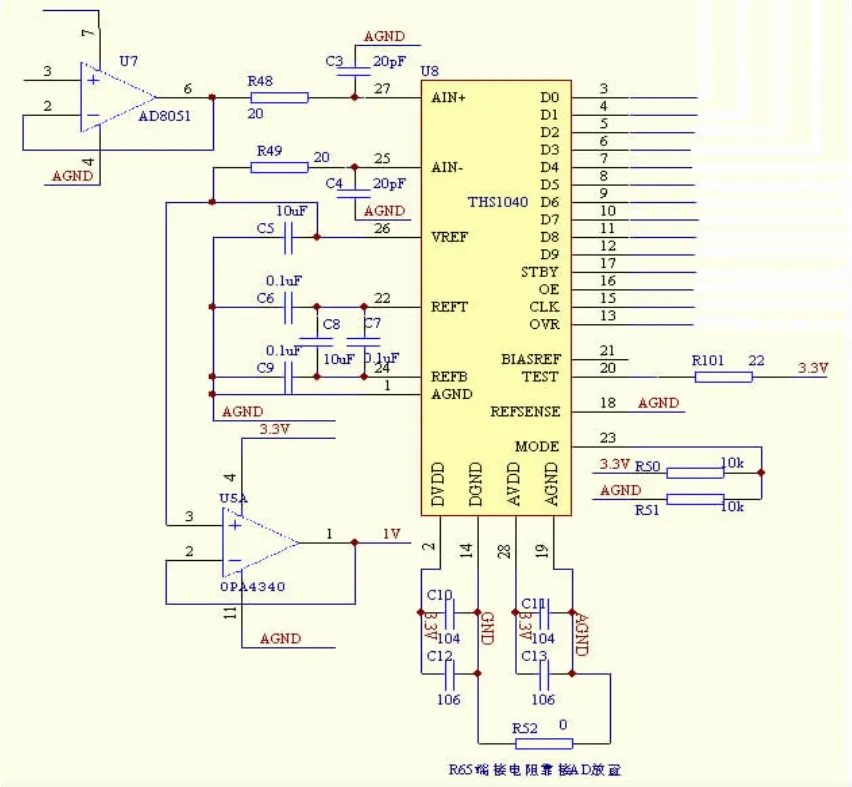

2.3 A/D转换电路设计

设计使用THS1040对信号进行采集。THS1040是一个低功耗(单一3 V电源供电)、10位、40MSPS模数转换器,同时支持单端和差分模拟输入。THS1041提供了多种选择的参考电压,以匹配用户的设计要求。为了使设计更加灵活,内部参考使用外部基准,以满足直流精度和温度漂移要求的应用程序。整体电路如图5所示。

图5 A D转换电路

通过模拟开关切换的当前待采信号经过运放AD8051跟随后,通过AIN引脚进入THS1040转换为10位数字信号,然后传入FPGA进行缓存和编帧。VREF引脚参考电压为1 V,经运放OPA4340跟随,可以增加其输入阻抗、减小输出阻抗、提高带负载能力。REFT和REFB电压通过内部参考发生器控制在2 Vp-p的ADC输入范围。

3 存储模块设计

设计采用FLASH进行数据存储,它具有体积小、功耗低、存储量大等特点。FLASH是按页进行存储的,写完一页后要进行下一页控制字和地址的重新写入。在相邻页交替的时间内要保证数据完整不丢失,所以采集到的数据不能直接存入FLASH,而是利用FPGA内部的双口RAM作为缓存[3]。采集到的数据先写入双口RAM,然后再写入FLASH。操作过程中保证双口RAM的数据输入速度小于输出速度。

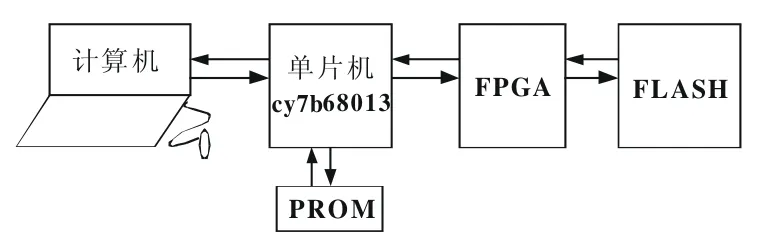

4 USB读数接口设计

USB模块是连接计算机与记录装置的主要设备,它主要负责将记录装置存储的数据上传到计算机和将计算机的命令下发给记录装置实现擦除等功能命令[4]。USB模块设计时选用USB2.0协议芯片Cy7c68013,此芯片经过了大量的应用实践,设计较为可靠。图6为USB接口模块工作原理图。

图6 USB接口模块工作原理图

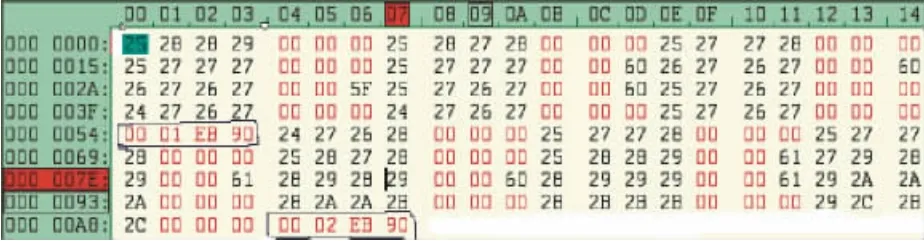

5 调试及结果

为了验证装置的采集功能,利用信号源输出正弦波来提供18路模拟信号作为待采信号。上位机软件通过USB接口下发控制命令,将数据上传至计算机进行后期的处理分析。

测试过程为:上电后首先对设备进行擦除操作,出现擦除完成指示后启动线上加+27 V的阶跃信号,启动记录装置进行记录。此时,记录指示灯绿灯亮。记录60 s后,记录指示灯灭表示记录结束。上位机软件通过USB接口将数据读入计算机进行绘图分析。从图7可以看出采集上来的数据准确无误。

6 结论

图7 回读数据

该装置以FPGA为核心控制器件,控制模拟开关和模数转换器对导弹引信在高速动态交会试验中发射飞行过程中引信的多普勒信号、点火信号以及引信保障执行机构等的工作状况共18路模拟信号进行采集。之后上位机通过USB接口将数据上传至计算机进行后期处理。经测试该装置可以满足要求正常工作。

[1] 周治良,刘俊,张斌珍.基于FPGA及FLASH的数据采集存储系统设计[J].微计算机信息,2007,23(7):91.

[2] 李鹏,马游春,李锦明.基于FPGA的多路数据采集模块硬件设计[J].仪表技术与传感器,2010,3(3):80.

[3] 林长青,孙胜利.基于FPGA的多路高速数据采集系统[J].电测与仪表,2005,42(5):52.

[4] 安荣,任勇峰,李圣昆.基于FPGA和USB2.0的数据采集系统[J].仪表技术与传感器,2009,3(3):50-52.

Design and implementation of multi-channeldata recording apparatus

SHAN Yan-hu,WEIYi-ran,ZHEN Guo-yong (M inistry of Education Key Laboratory for InstrumentScience and Dynam ic Test,National Key Laboratory forElectronic Measurement Technology,North University of China,Taiyuan Shanxi030051,China)

The design of an FPGA-based multi-channel acquisition circuit was introduced.The device master chip FPGA control analog switches in high-speed dynamic intersection test launch missile fuze flight fuse Doppler signal, ignition signals and fuse protection executing agency of the state of real-time acquisition of missile-borne and THS1040 ADC converts the analog signal into a digital signal stored in the FLASH memory.The launch is complete, the host computer via the USB interface to upload data to the computer to decompose,drawing.It has been proved that the device can collect and store signal accurately and achieve the design by the repeated experiments.

FPGA;multi-channel;signal acquisition;analog-to-digital conversion

TM 93

A

1002-087 X(2013)11-2032-03

2013-04-26

国家自然科学基金(50905169)

单彦虎(1985—),男,江苏省人,博士生,主要研究方向为动态测试、微系统及集成技术、信号处理。