基于RS485的数据通信协议的设计与实现

2013-06-23杜小丹刘永红

鄢 涛,杜小丹,刘永红,胡 庆

(1.模式识别与智能信息处理四川省高校重点实验室 四川 成都 610106;

2.成都大学 信息科学与技术学院,四川 成都 610106;3.成都大学 电子信息工程学院,四川 成都 610106)

RS485作为一种串行通信标准,采用差分收发方式,实现通信系统的物理层连接,具有通信距离远,传输速度快,抗噪声干扰性好等优点[1-4],已被广泛应用于各种领域。文中所介绍的通信系统能够接收高低速串行数据,针对高低速数据的不同速率和接收模式的要求,本文以RS485标准为物理层基础,在现场可编程门阵列(FPGA)平台上设计并实现了高低速串行数据的可靠接收。

1 协议描述

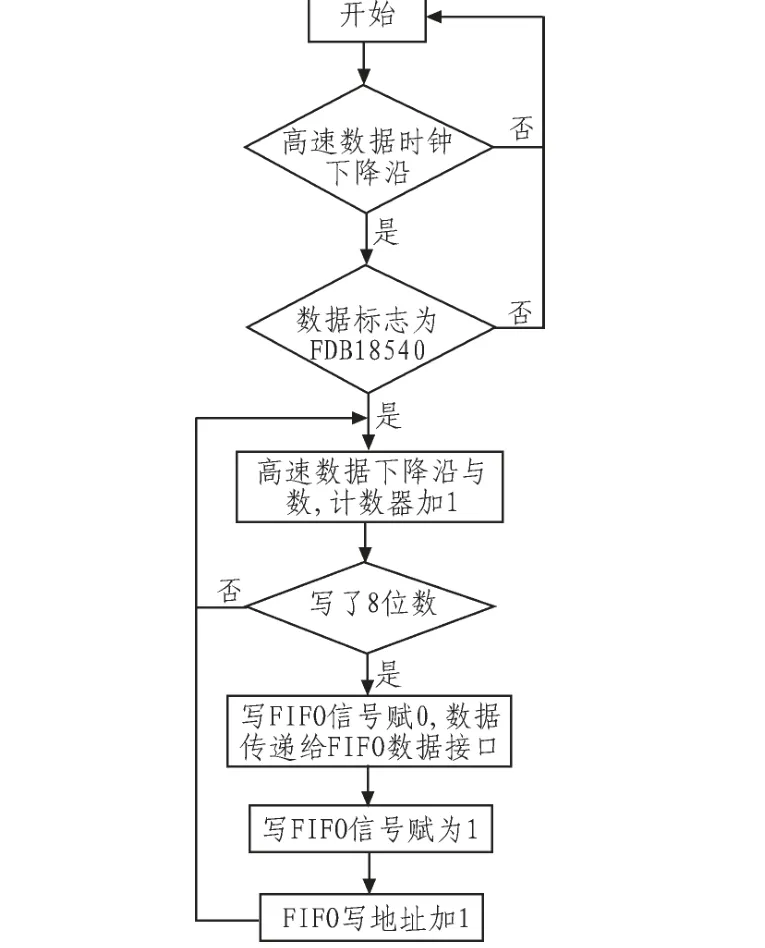

用特殊的标志字来表示数据帧的起始位置,以便接收有效的数据信息,从而实现同步。标志字选用16进制数“FDB18540”,这种标志字经过大量测试表明它的独立性很好,不会和数据内容重复,可以有效避免假同步现象。高速数据接收时,在同步高速时钟的上升沿时,检测高速数据的标志字,当检测到标志字时,就意味着有效数据的到来,系统开始接收高速数据。

1.1 高速数据通信协议

1.2 低速数据通信协议

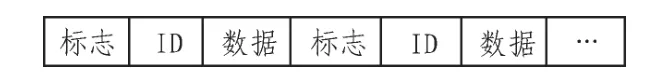

本通信系统的高速接口包括时钟和数据两个接口,高速数据接收采用同步RS485通信协议,高速时钟速率为3.6864 MHz,与数据发送时钟同源,可以利用同步时钟实现数据接收同步。高速数据具有特定的帧格式,每帧容量为2 kB,帧格式[5-6]如图1所示。

图1 高速数据帧格式Fig.1 Frame format of high-speed data

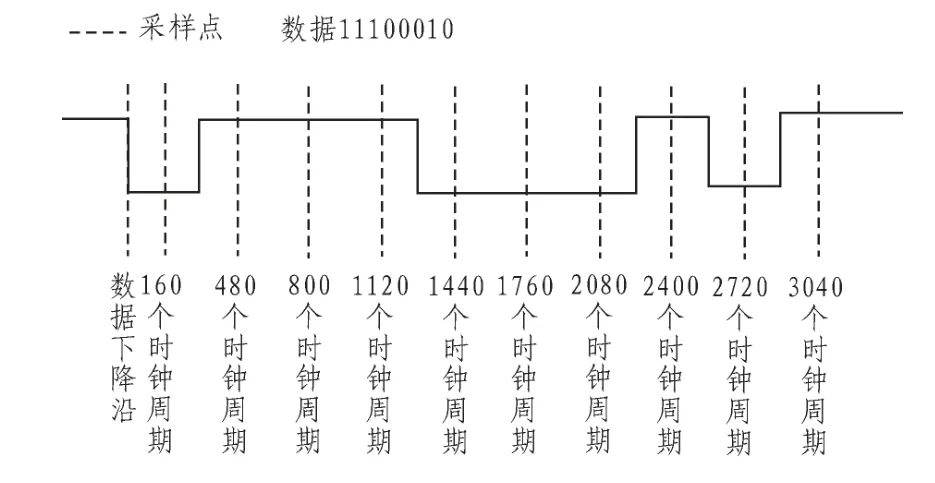

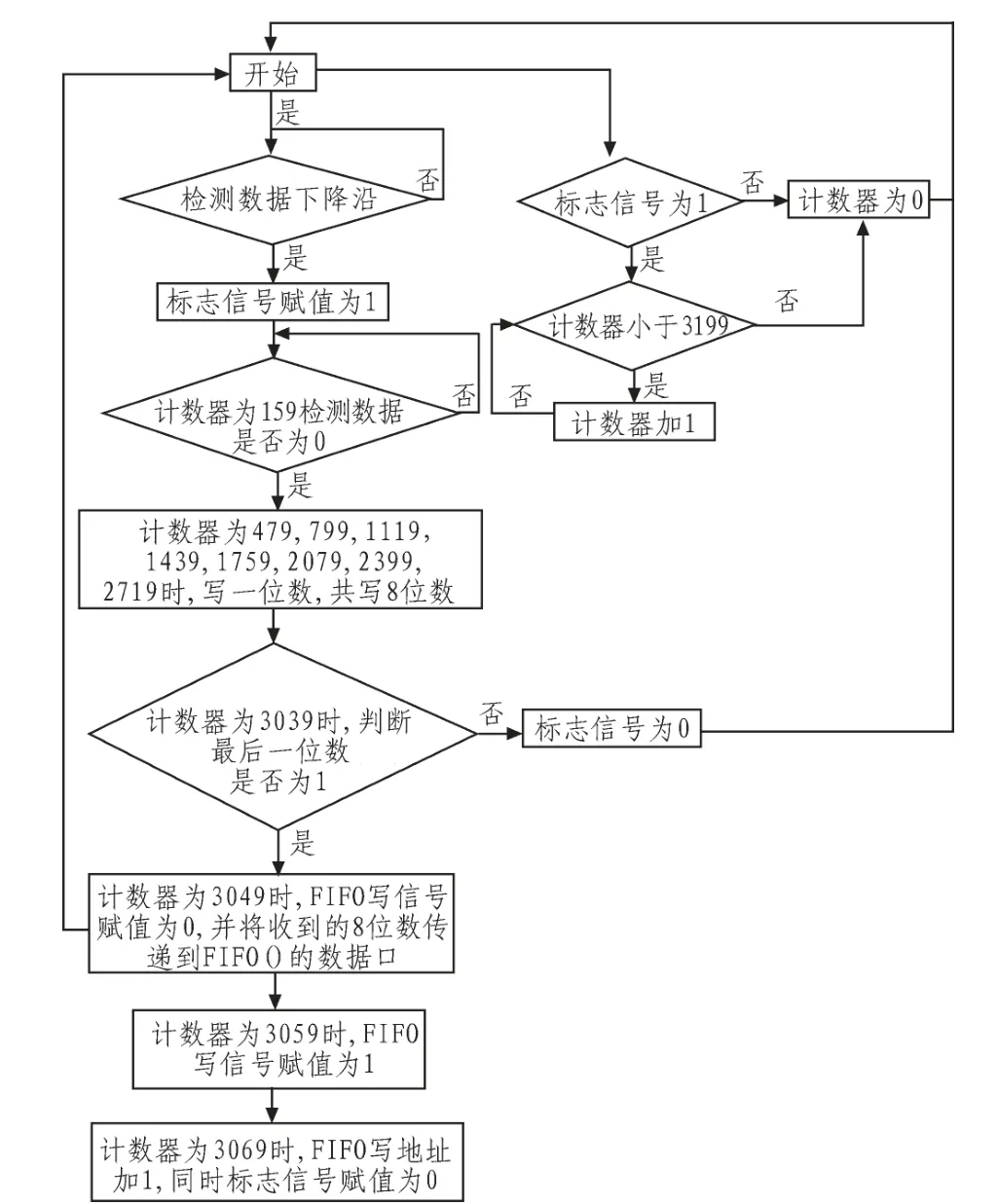

低速数据没有同步时钟控制,采用异步RS485通信协议,以字节作为通信协议的基本单元,每字节1个起始位,8个数据位,1个截止位,波特率115.2 kbps。低速数据接收时,利用FPGA的外部时钟源作为检测时钟,时钟频率为36.864 MHz,每传输1bit数据占用320个时钟周期。当检测到数据的下降沿时,就开始对检测时钟计数,实现低速数据的位同步,当记到160个时钟时,对输入数据进行检测,当检测到输入的信号为低电平时,以后每隔320个时钟周期,进行一位数据的接收,共接收8位,再隔320个时钟周期后,检测截止位是否为高电平,如果为高电平,则接收的8位数据为有效数据,再进行下一字节数据接收。否则,丢弃数据,时钟计数归零,重新检测数据。可以看出,对低速数据接收的采样点是每位数据的中间位置。信号在连续长“1”之间的短“0”很容易受到码间干扰影响变短,但本文在中间位置进行检测,只要短“0”的长度在原始信号长度的一半以上就可以得到正确数据。数据接收同步示意图如图2所示,可以看出这一字节的起始位为0,截止位为1,通过检测时钟对数据采样,数据被正确接收。这种通过检测数据跳变沿作为数据起始的同步方法可以减少RS485通过双绞线长距离传输时的码间干扰。

图2 数据接收同步示意图Fig.2 Schematic diagram of data receiving synchronously

在数据进入FPGA后,再对低速数据进行打包,每包容量为512B,在包头和包尾分别加入标志字,再通过USB接口传送到计算机,通过对低速数据打包,可以有效地区分同时接收的高低速数据,防止数据出现不连续情况。

2 硬件设计

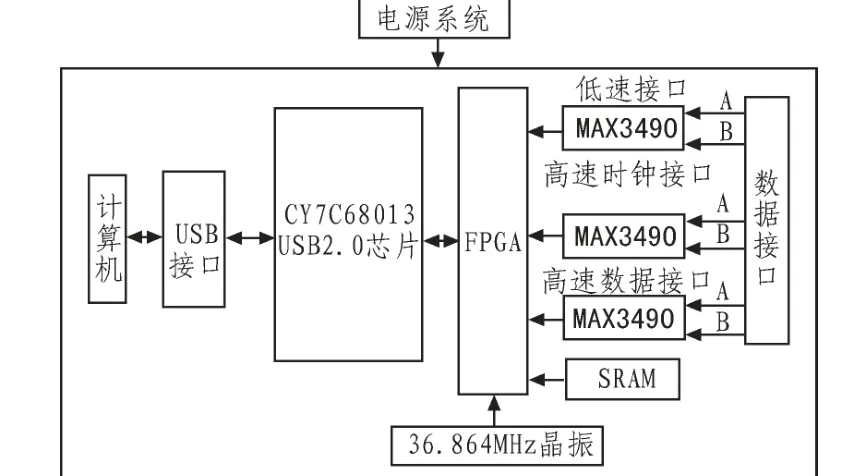

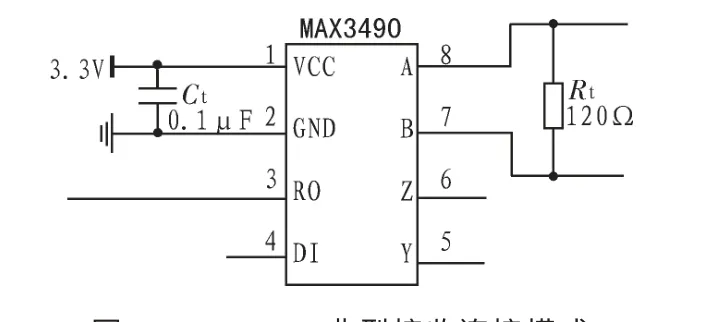

硬件原理框图如图3所示。模式,输入电压范围为-7~+12 V,输出电压高电平为最小为供电电压减去0.4 V,低电平最大为0.4 V。它的典型接收连接模式如图4所示。

图3 硬件原理框图Fig.3 Functional block diagram of the hardware

图4 MAX3490典型接收连接模式Fig.4 Typical receiving connection mode of MAX3490

FPGA选用XILINX公司的Spartan3系列的XC3S200芯片,它采用多电压供电,其中内核电压为1.2 V,I/O口驱动电压为3.3 V,其他的辅助电压为2.5 V。该芯片含有4320的逻辑资源、141个可用的I/O口。外部晶振源频率为36.864 MHz,作为低速数据的检测时钟,利用FPGA内部的倍频模块对它进行倍频后作为高速数据接收的外部时钟。

FPGA外部外加了一个容量为1 MB的SRAM作为外部缓存,它的作用主要是作为高速数据的实时缓存,弥补利用硬件逻辑无法提供大容量空间进行高速数据的缓冲存储的缺点,可以保证高速数据在传输过程中不会在FPGA接收环节丢数。SRAM芯片选用CY7C1059DV33,它的深度为1M,宽度为8 Bit,容量为1 M×8 Bit,3个控制端控制SRAM的读写操作,支持异步通信。

FPGA利用CY7C68013芯片通过USB接口与计算机进行通信。CY7C68013属于Cypress公司的FX2系列产品,是Cypress公司生产的第一款USB2.0芯片。 CY7C68013是一个带增强型MCS51内核和USB接口的单片机,完全遵从USB2.O协议,可提供高达480Mbps的传输率;内部集成PLL(锁相环),最高可使5l内核工作在48 MHz;对外提供两个串口,可以方便地与外部通信;片内拥有8KB的RAM,可完全满足系统每次传输数据的需要,无需再外接RAM。

3 逻辑设计

RS485标准是基于差分传输的[7],它使用一对双绞线作为传输介质,通过两根线之间的差分电压来表示相应的逻辑状态。数据信号进入FPGA之前,必须经过接口芯片进行电压转换[8]。根据设计要求,高低速接口最高的输出码率为3.686 4 MHz,由于本通信系统只是接收数据,所以工作在单工模式。因此,RS485接口芯片选用MAX3490,它采用3.3 V单电源供电,波特率最高可达10Mbps,可以支持全双工工作

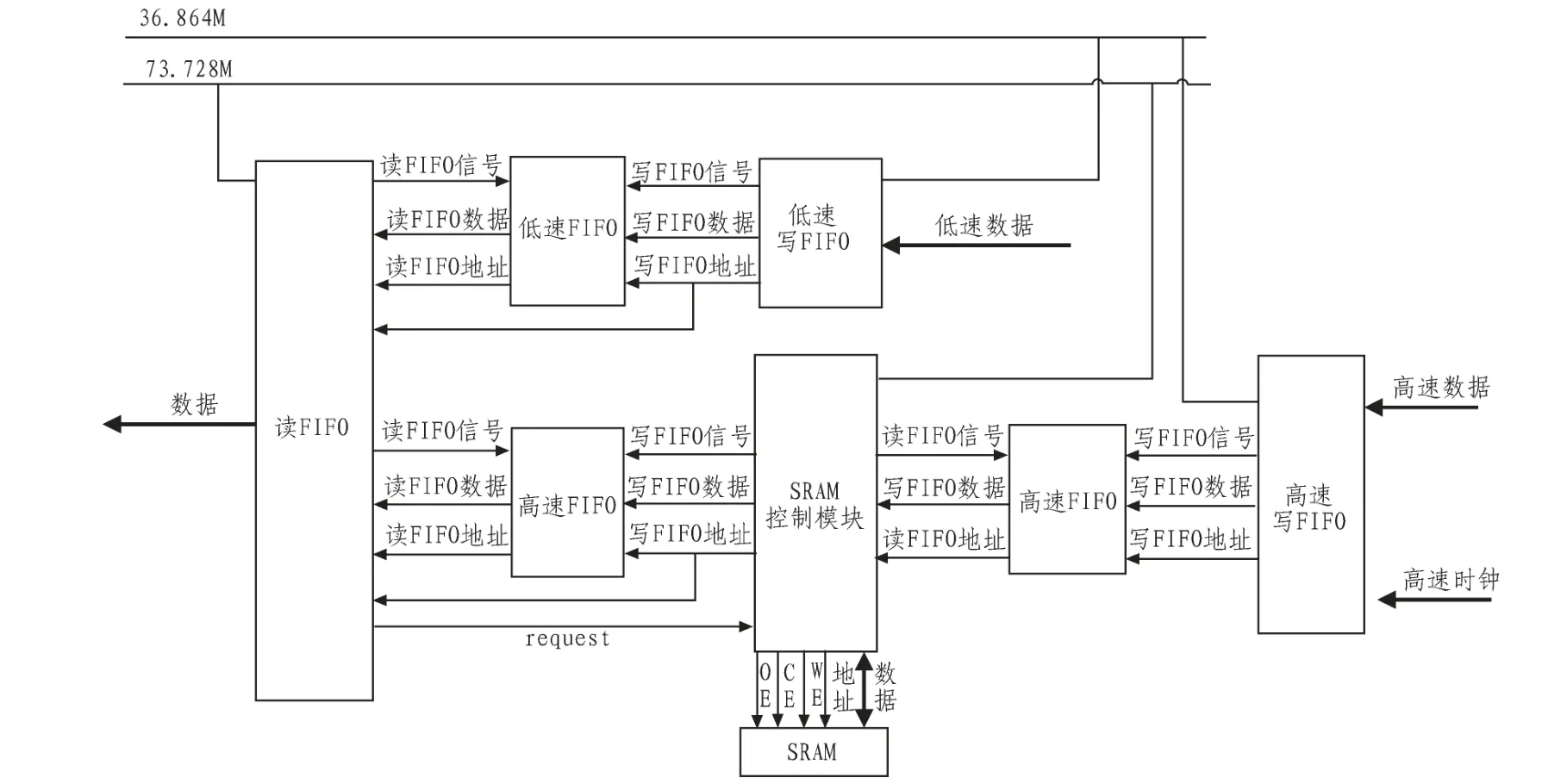

RS485接收芯片将收到的差分信号解为串行信号,FPGA内的程序对串行信号进行检测处理,接收数据。FPGA内部分别为高低速数据开辟了2k的FIFO作为缓存,为解决高速数据传输过程中可能由于FPGA内部缓存不够而导致丢数的问题,在FPGA外部加入1MB容量的SRAM作为外部缓存。低速数据接收采用一级缓存结构,高速数据接收采用采集三极缓存结构。图5为系统逻辑框图。

图5 接收高低速数据逻辑结构Fig.5 Data logical construction in receiving with high or low speed

FPGA内部模块主要包括高速写FIFO模块[9]、低速写FIFO模块、SRAM控制模块,读FIFO模块。高速写FIFO模块和低速写FIFO模块负责将接收到的数据暂时存入内部FIFO中;SRAM控制模块的功能主要是控制SRAM的读出、写入,将一级缓存FIFO中的数据写入SRAM,将SRAM中的数据读出写入三级缓存FIFO中。读FIFO模块主要是根据计算机下发的命令,选择读取高速FIFO和低速FIFO中的数据,并将数据送至数据总线。在设计FIFO过程中,读FIFO的时钟信号必须大于写FIFO的时钟信号,否则,将会导致FIFO溢出,接收数据丢失。本设计中读FIFO时钟频率是写FIFO时钟频率的二倍,读FIFO的速度远大于写FIFO速度。

传输协议是基于XILINX公司的XILINX7.1开发环境利用超高速集成电路硬件描述语言(VHDL)设计。图6为高速写FIFO模块,图7为低速写FIFO模块流程图。

图6 低速写FIFO模块流程图Fig.6 Flow chart of writing module FIFO with low speed

图7 高速写FIFO模块流程图Fig.7 Flow chart of writing module FIFO with high speed

读FIFO模块共有3种读取模式:单独读低速FIFO,单独读高速FIFO,同时读高速FIFO和低速FIFO。读FIFO模块是通过FPGA内部集成FIFO半满信号触发单片机进行读数的,单片机检测到FIFO半满信号后,单片机才开始从FIFO中读取数据,执行每次读操作,连续从FIFO中读取512bit数据,FIFO半满信号是读FIFO模块通过比较FIFO读写地址的差值而对其赋值的,它的有效值为0。当写地址与读地址之差大于515时,FIFO半满信号赋值为0,否则为1。利用FIFO半满信号控制读数过程,可以有效防止空读和误读现象。

SRAM控制模块包括写SRAM和读SRAM两部分,写SRAM是由一级缓存FIFO的半满信号触发的,当半满信号有效时,开始写SRAM。读SRAM是通过读FIFO模块传递过来的request信号来控制的,当request信号有效时,读取SRAM中的数据,然后将它写入到三级FIFO,读FIFO模块从三级FIFO模块中读取数据。

4 结 论

基于现场可编程门器件(FPGA)FPGA设计的RS485数据通信协议,可以实现高速数据和低速数据接收,以及二者的同时接收。 采用专门的RS485接收芯片,在信号进入了FPGA前,进行电压转换。利用FPGA内部资源构建FIFO为数据接收提供缓存,并为了保证高速数据可靠接收,外部加入SRAM加大高速数据接收缓存。经过实际测试,本设计稳定可靠,能够实现采用RS485标准的数据通信。

[1]JIA Hui-juan.Research on the Technology of RS485 over Ethernet,The International Conference on E-Product,EService and E-Entertainment (ICEEE2010)[C].Henan,China,2010:1-3.

[2]耿立中,王鹏,马骋,等.RS485高速数据传输协议的设计与实现[J].清华大学学报,2008,48(8):1311-1314.GENG Li-zhong,WANG Peng,MA Pin,et al.The design and implementation of transport protocol of high-speed data[J].Journal of Tsinghua University,2008,48(8):1311-1314.

[3]NI Hai-yan,HU Chao,MA Chang-wang.Research on a 485-serial network architecture in intelligent uptown management[C]//Proc 2006 IEEE Conf on Mechatronics and Automation.Luoyang:IEEE Press,2006:400-405.

[4]B&B Electronics Mfg.Co.Inc.THE RS-485 APPLICATION“CHEAT SHEET”[EB/OL].(2012-01-01)[2012-9-03].http://www.bb-elec.com/getattachment/7045d510-a095-4064-a739-518eea017363/RS-485-Quick-Guide-Just-the-Essentials-on-a-Single.aspx

[5]李成钢,申萍,聂晓波.基于FPGA的HDLC与RS485通信网关的设计[J].机车电传动,2011,1(1):20-23.LI Cheng-gang,SHEN Ping,NIE Xiao-bo.The design of communication gateway between HDLC and RS485 based on FPGA[J].Electric Transmission in the Locomotive,2011,1(1):20-23.

[6]陈金华.基于HDLC协议的RS485通信设备的研制[J].测控技术,2010,29(6):98-101.CHEN Jin-hua.Research on RS485 communications equipment based on HDLC protocol[J].Measure and Control Technology,2010,29(6):98-101.

[7]QIN Shi-hong.Design of the Multi-computer communication system based on RS485[C]//2011 International Conference on Electric Information and Control Engineering(ICEICE),2011:1318-1320.

[8]GU Yong-hong,WEI Huang,YANG Qiao-li.Design and Implementation of a Multi-Channel HDLC Protocol Controller Based on FPGA[C]//2010 International Conference on Electrical Engineering and Automatic Control(ICEEAC2010),2010:266-269.

[9]BIN Huang.Design of a multi-channel high speed FIFO applied to HDLC processor based on PCI bus[C]//IEEE 2002 International Conference on Communications,Circuits and Systems and West Sino Expositions,2002:1476-1480.