基于ADF4360-8的锁相环频率合成器的设计与实现

2013-06-15谢亮芦旭吴成英杨建青樊战友

谢亮,芦旭,吴成英,杨建青,樊战友

基于ADF4360-8的锁相环频率合成器的设计与实现

谢亮1,2,芦旭1,2,吴成英3,杨建青1,2,樊战友1

(1. 中国科学院国家授时中心,西安 710600;2. 中国科学院研究生院,北京 100039;3. 湖北民族大学,恩施 445000)

为满足工程需要,设计并实现了一种基于锁相环芯片ADF4360-8的低噪声高稳定度频率合成器。给出了该频率合成器的设计原理、硬件组成、软件设计及其实现方法与流程。重点介绍了一些主要芯片和关键电路。该锁相环频率合成器输出的100MHz较高频周期信号的峰-峰值达到2.16V,能直接驱动TTL电路。测试结果表明该频率合成器输出的频率信号稳定,噪声低,幅度大。

频率合成器;锁相环;相位噪声;压控振荡器

0 引言

随着计算机、高速通信、导航定位以及航空航天等高科技领域的迅猛发展,系统对频率源所提供的频率稳定度、输出频率范围、信号幅度等要求越来越高[1]。为了提高频率的稳定度以及满足在规定的频率范围内输出任意频率的要求,目前大量采用频率合成技术,通过对参考频率进行加、减、乘、除运算,就可以由一个具有高稳定度和高准确度的标准频率源产生一系列具有同一稳定度和准确度的频率信号。频率合成器在许多现代电子系统中是必不可少的,可用于目前高尖端的信息产业。目前,频率合成技术的发展趋势是:1)锁相环频率合成器芯片的性能不断提高;2)鉴相器部分使用最新的电荷泵技术,这样的锁相环具有功耗低、速度快、抖动低的特点;3)锁相环芯片外围电路结构芯片的技术也得到了发展,在一定的程度上提升了锁相环的性能[2]。

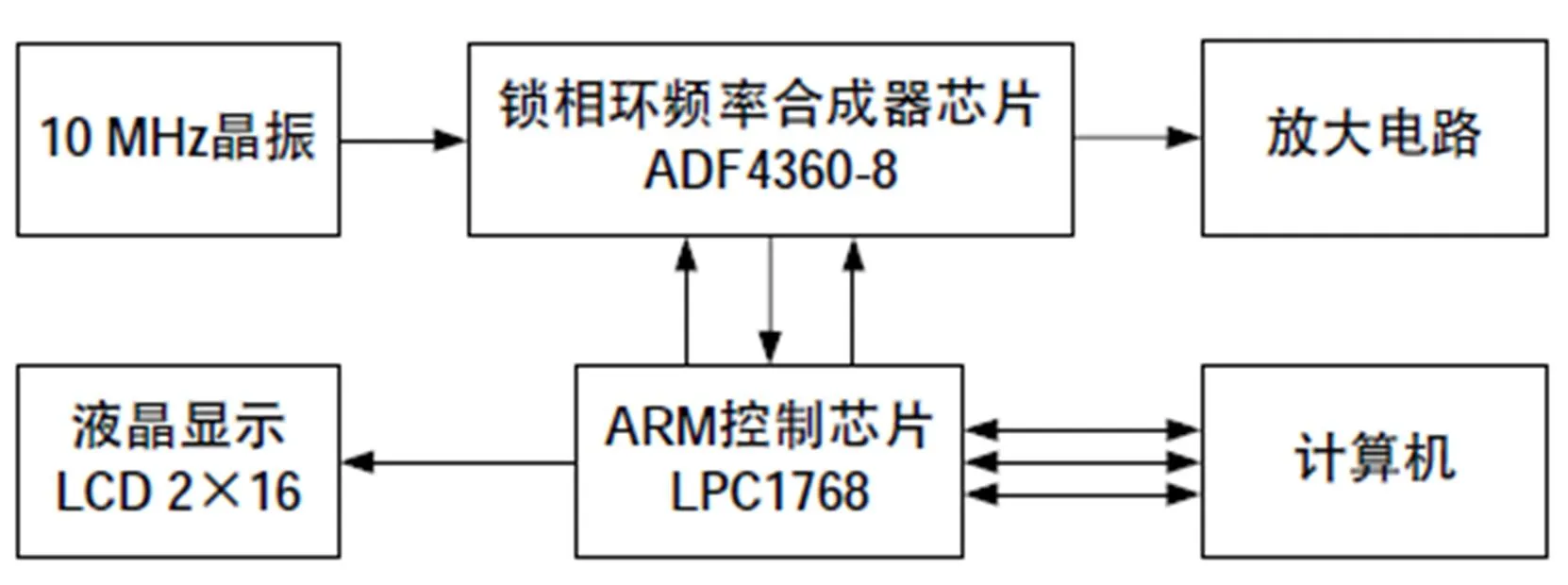

现在普遍采用的锁相环频率合成器的组成原理框图如图1所示,在压控振荡器与鉴相器之间的反馈回路上增加一个整数分频器就可以构成一个整数频率合成器,通过改变分频系数,压控振荡器就可以产生不同的输出频率[3]。

图1 锁相环频率合成器的组成原理框图

本文设计的锁相环频率合成器旨在为高精度时间间隔计数器提供可靠稳定的输入参考频率,因此,选用了ADI公司的具有高稳定度和低噪声性能的整数分频锁相环芯片来实现100 MHz的频率输出。

1 基于ADF4360-8芯片的锁相环电路设计

本设计的整体设计框图如图2所示,系统控制部分由ARM芯片LPC1768来完成。ARM控制液晶显示屏、锁相环频率合成器芯片ADF4360-8以及连接计算机。

图2 锁相环频率合成器设计的整体框图

如图2所示,系统采用外部10 MHz的晶振作为参考频率提供给锁相环频率合成器芯片ADF4360-8,同时采用LPC1768作为控制芯片来配置锁相环芯片ADF4360-8内部的R分频器、C控制器以及N分频器,从而完成锁相环芯片的外部输入以及配置。另外,ADF4360-8的MUXOUT端口将芯片内部的工作情况反馈给LPC1768,LPC1768通过相应的处理使得锁相环芯片的内部工作信息显示在LCD上,使用户能够清楚地看到芯片的工作状态。此外,通过计算机来控制锁相环芯片输出不同的频率:由计算机串口将数据传递给ARM芯片LPC1768,ARM再对锁相环芯片相应的寄存器重新配置,进而得到不同的输出频率。这样得到的锁相环频率合成器虽然满足设计的要求,但是由于波形幅度较小,无法满足实际工程中的需要。因此,本设计中增加了放大电路对输出频率进行放大以满足实际工程中的应用[4]。

2 芯片介绍以及硬件设计

2.1 ADF4360-8芯片介绍

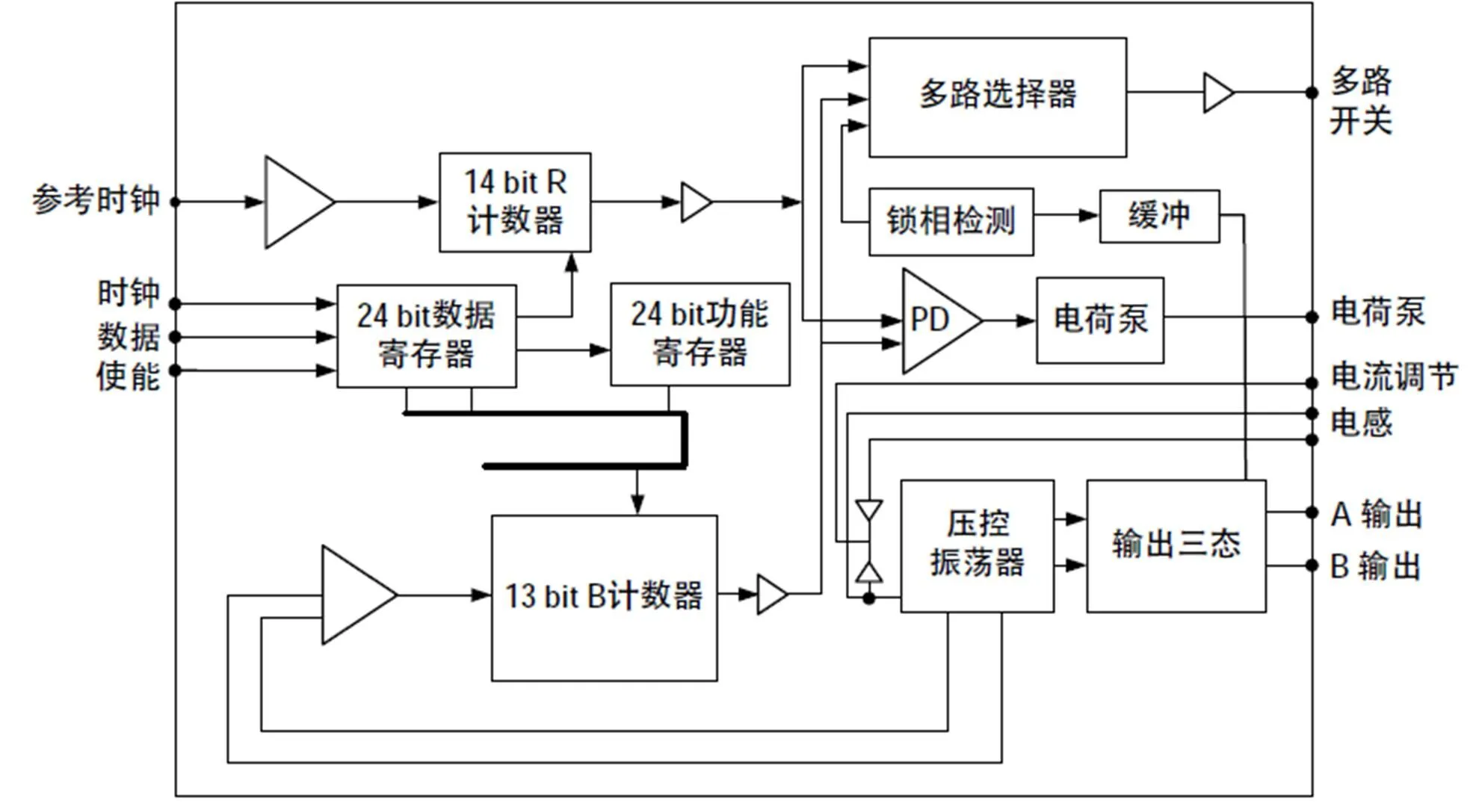

本文所用的锁相环芯片ADF4360-8是整数分频频率合成器芯片,其内部结构如图3所示[5]。该芯片集成了除低通环路滤波器之外的所有其他模块,因此只需要在鉴相器与压控振荡器之间设计一个低通环路滤波器就可以实现一个完整的锁相环电路,使设计趋于小型化。

图3 ADF4360-8的内部结构

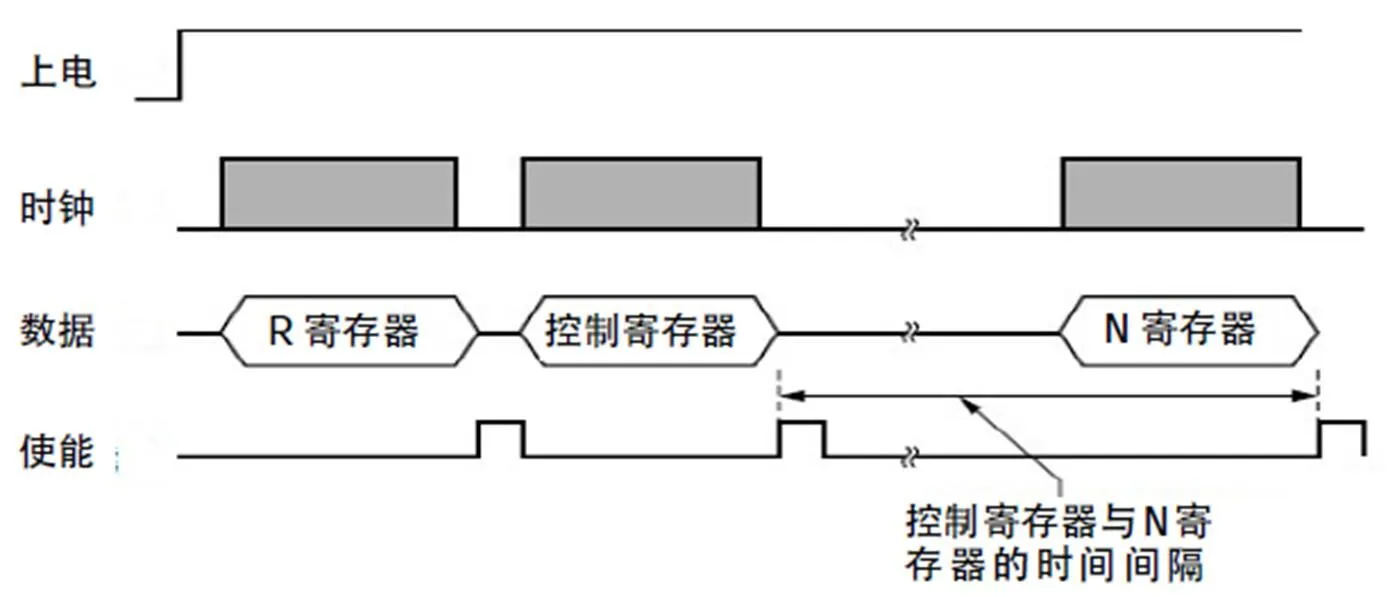

ADF4360-8内部的反馈分频器N寄存器和参考分频器R 寄存器以及功能寄存器F都需要配置24 位数据。配置的顺序是加参考时钟→R寄存器→F寄存器→N寄存器。由于要等待ADF4360-8内部VCO的电流稳定后,再加载N寄存器数据,故F寄存器和N寄存器赋值间隔要大于15ms。具体的时序原理图如图4所示。

另外,锁相环芯片ADF4360-8还有一个多路输出端口MUXOUT,通过对此端口的配置可以检测锁相环芯片的内部工作状态。对芯片配置完成之后,重新加电可使频率合成器正常工作。

图4 ADF4360-8的配置时序图

2.2 LPC1768芯片介绍

LPC1768是NXP公司推出的基于ARM Cortex-M3内核的微控制器LPC17XX系列中的一个型号。LPC17XX系列Cortex-M3微处理器主要应用于高集成度和低功耗的嵌入式产品中。LPC1700系列微控制器的操作频率可达100 MHz。ARM Cortex-M3 CPU具有3级流水线和哈佛结构。LPC17XX系列微控制器的外设组件包含高达512 KB的flash存储器、64 KB的数据存储器、以太网MAC(media access control)、8通道DMA(direct memory access)控制器、4个UART(universal asynchronous receiver/transmitter)、2条CAN(controller area network)通道、2个SSP(synchronous serial port)控制器、SPI(serial peripheral interface)接口、3个IIC(inter-integrated circuit)接口、2输入和2输出的IIS(inter-IC sound bus)接口、8通道的12位ADC(analog to digital converter)、10位DAC(digital to analog converter)、电机控制PWM(pulse width modulation)、正交编码器接口、4个通用定时器、带有独立电池供电的超低功耗RTC(real-time clock)和多达70个的通用IO管脚。

对ADF4360-8的配置可通过LPC1768的SPI接口对分频器R,N以及控制器F进行相应的配置。通用的GPIO接口可实现向LCD显示器的寄存器写入数据。

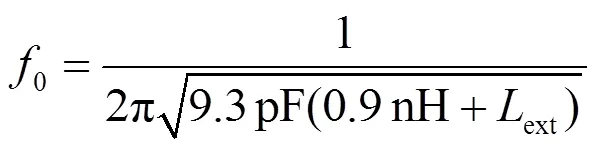

2.3 ADF4360-8芯片关键参数的确定

式(1)中pF为电容量的单位,nH为电感量的单位。

本设计所要求的输出频率是100 MHz,因此可以计算出外部电感的大小为271 nH。该参数在频率合成器中是很重要的参数,它影响压控灵敏度,同时,对电感应该选择线绕式电感,否则压控振荡器无法起振[6]。

“三农”问题的形成具有其历史根源与现实因素。建国初期,重工业优先发展战略是我国“三农”问题形成的历史根源;改革开放后,农村资本和劳动力两种生产要素的单向双边流动是“三农”问题不断加深的现实经济根源。[2]庞绍堂认为,“三农”问题源自传统模式下国家优先发展重工业,其核心制度安排是二元财政体制,必须通过“经济——政治”改革才能根除。[3]赵忠升认为农民权益问题和农民能力问题是“三农”问题的核心。[4]这些学者对“三农”问题的形成进行追根溯源,有利于把握其本质,寻找破解之策。

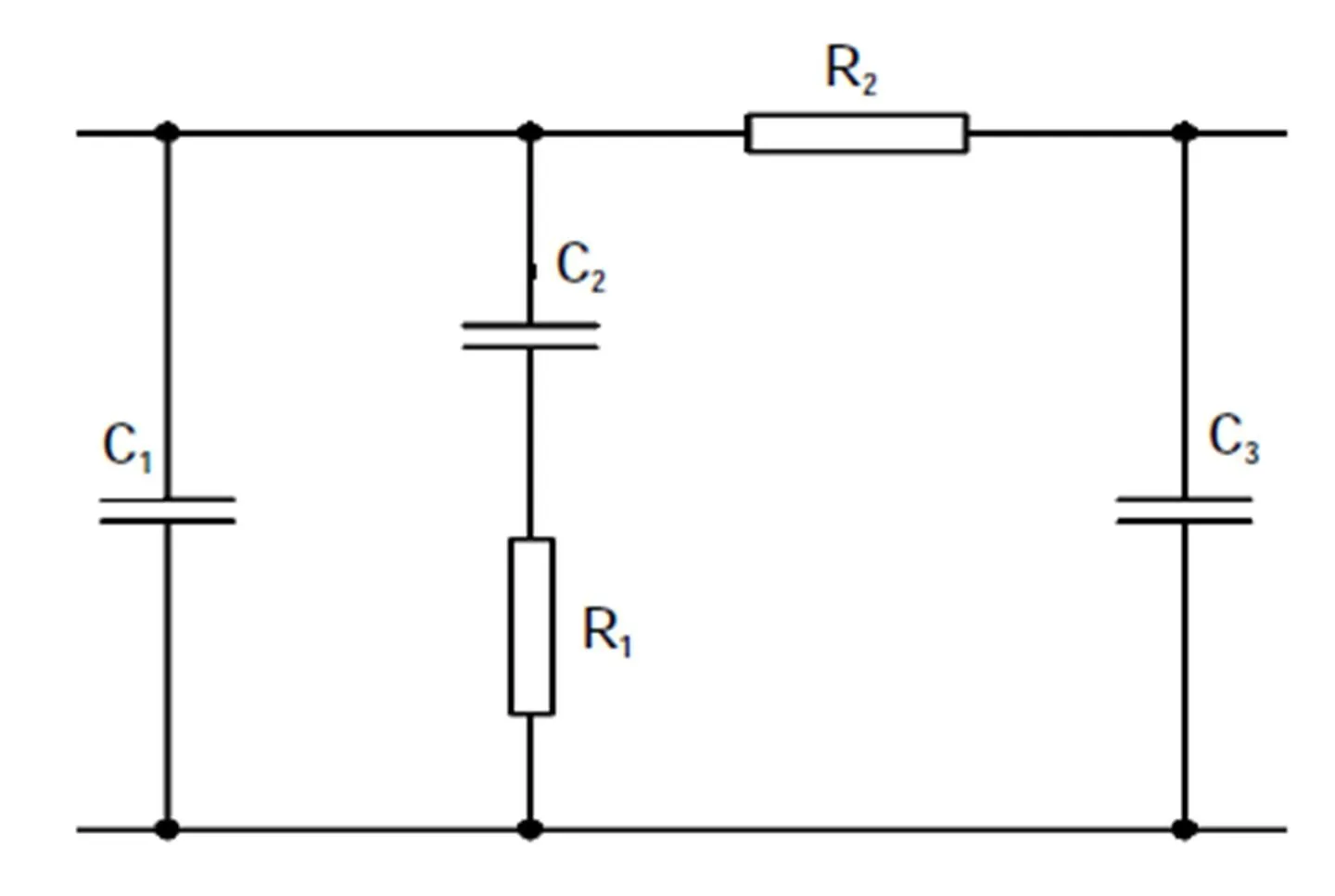

2.4 ADF4360-8环路滤波器的设计

由于ADF4360-8中已经集成了大部分的模块,因此只需要设计鉴相器与压控振荡器之间的环路滤波器就可以完成整个锁相环电路的设计。本设计采用的环路滤波器为三阶无源低通滤波器[7](如图5所示)。这样的结构可以提高环路滤波器的稳定性,同时也可以滤除压控振荡器直流控制电压带来的纹波噪声。并且进一步减少杂散。

图5 三阶低通滤波器

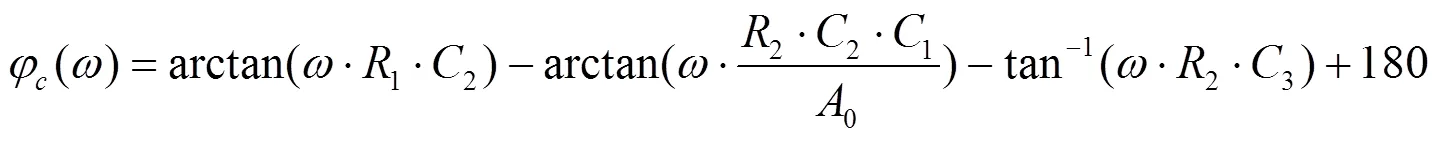

图5所示的2R3C结构的三阶无源滤波器的传递函数通过傅里叶变换可以用以下公式[8]来表示:

2.5 硬件电路的设计

图6为ADF4360-8的外围部分主要硬件电路图,该图包括了芯片的关键参数L1,L2以及环路滤波器的设计图。

图6 ADF4360-8的外围电路

另外,本文所设计的锁相环频率合成器的显示部分采用2×16-LCD显示屏LMB1206A来实现。LMB1206A的内核模块包含一个数据寄存器和一个指令寄存器,指令主要用来对显示屏进行初始化,实现基本的控制,包括清屏、光标设置、功能设置等[9]。LMB1206A既可以写数据到RAM,又可以从RAM中读出数据。该模块配置简单,功能完全满足设计的需求,因此,在本系统的设计中采用该模块来显示系统的工作状态信息。

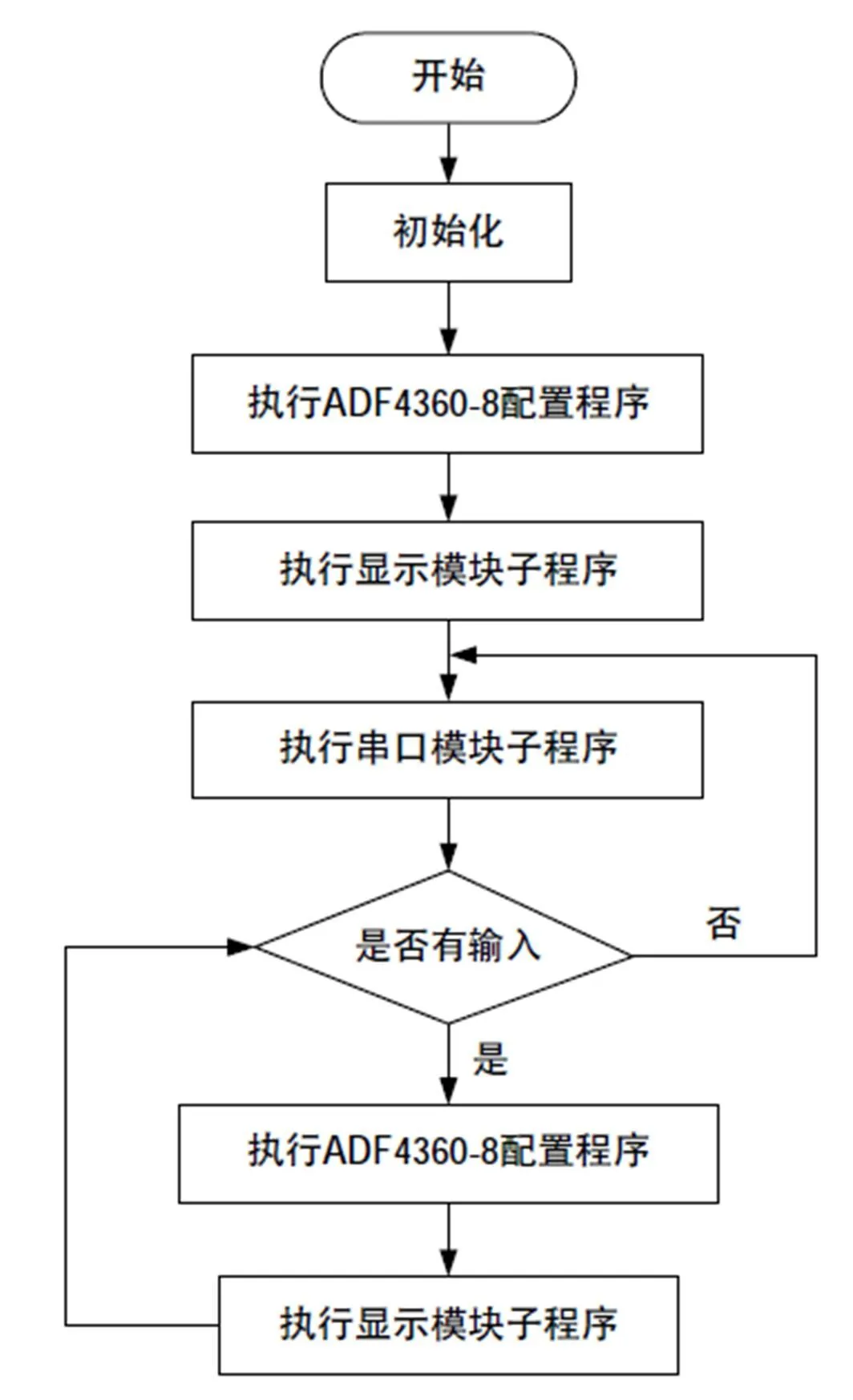

3 系统软件设计

在系统硬件设计完成之后,开始软件的设计。本系统软件模块主要包括以下3个:主控制模块、串口通信模块和LCD显示模块。软件的编写要遵循ARM控制芯片的开发环境。

图7 系统流程图

以上所示为整个系统设计的流程图。串口通信和LCD显示是常用的通信接口与显示模块,流程简单,不在此赘述。

4 放大电路设计模块

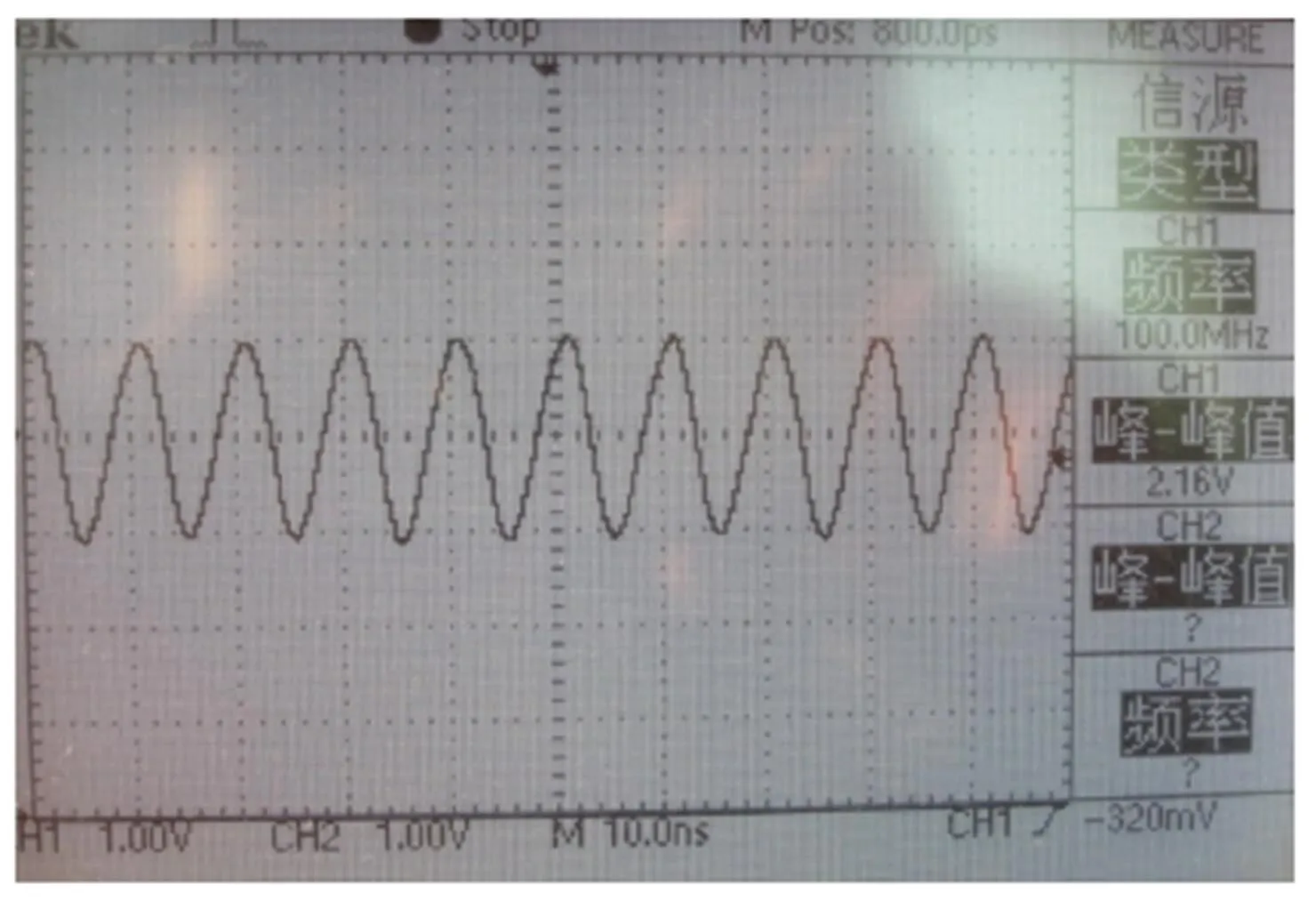

由于频率合成器电路的输出信号峰-峰值小于1V,无法达到TTL(transistor transistor logic)电平的要求,因此,在差分信号的输出端应该设计放大电路使输出信号的幅度满足计数器输入电平的要求。本设计中的输出频率为100 MHz,输出频率较高,一般放大器无法满足高频幅度的要求。因此,选择具有高性能的高速运算放大器THS3001来完成放大电路的设计,较为符合器件性能和设计要求。放大电路的原理图如图8所示。

由图8可见,频率合成器的差分输出信号首先经过差分放大,这样可以滤除外界的噪声信号所带来的干扰。经过一级放大之后,再经过同向放大,从而使频率合成器的输出信号幅度得以放大,以满足实际的需求。在实验中对放大后的效果进行了实际测量。

5 实验结果

图9是所研制的频率合成器的实物图,采用两层电路板设计,供电电压为5 V。采用有源晶振来提供10MHz的输入参考频率,通过改变ADF4360-8的外置电感并配置相应的寄存器就可以输出65~400MHz内的任意频率。本文作者所设计的频率合成器中心频率为100MHz,输出频率范围为91~109 MHz,分辨率为1 MHz。

图9 频率合成器实物图

另外该频率合成器还有一个多路检测端口MUXOUT,通过软件编程可以让该端口输出R分频后的信号、数字锁定指示、N分频后的信号、片内电源供电状态、串行数据输出等信息,从而检测锁相环芯片的工作状态进而可以从芯片内部的工作状态来分析芯片是否正常工作。

图10所示为频率合成器没有经过放大时,用示波器观察到的输入频率为10 MHz,输出100 MHz的波形图,由该图可以看出输出波形完整,未出现严重失真现象。由于输出信号经过示波器探头的衰减,观测到的峰-峰值只有280 mV,因此不能满足实际工程的需要。

图11所示为频率合成器经过放大电路之后的输出信号波形图。由该图可以看出经过放大之后的信号峰-峰值达到2.16 V,满足实际工程的需要,且输出波形平滑稳定[10]。

图12所示为本设计的锁相环频率合成器锁定后的LCD显示,从LCD显示屏可以很清楚地看到系统是否锁定,以及输出频率等内容。另外,在调试过程中,也可以显示锁相环芯片内部的配置数据,从而更加直观地看出配置数据是否正确。

图10 未经过放大的输出100 MHz的波形图

图11 经过放大电路之后的输出波形图

图12 LCD显示

另外,测试表明,本设计的锁相环频率合成器在偏离载波100 KHz范围内,总的相位噪声为-112 dBc,在偏离载波1 MHz时总的相位噪声为-138 dBc。

6 结论

根据锁相环的基本原理,介绍了一种基于高度集成化的频率合成器设计要点,同时给出了设计中的硬件原理图等,并得到了测试结果。频率合成器的输出波形与输入波形完全吻合,没有产生失真,波形光滑,没有毛刺。另外,从总的相位噪声来看,频率合成器具有低噪声的特点。此外,该基于锁相环芯片ADF4360-8的频率合成器体积小、功耗低,因此它可广泛应用于高频电路系统手持设备、测试设备以及通信导航等领域。

另外,为便于使用,下一步打算采用按键的方式输入所要输出的频率。

[1] 晋军, 程剑, 马黎丽. 基于ADF4360-X的频率合成器设计[J]. 军事通信技术, 2008, 29(1): 61-63.

[2] 王家礼, 孙璐. 频率合成技术[M]. 西安: 西安电子科技大学出版社, 2009.

[3] 陆振雨, 朱江, 张尔扬. 基于ADF4160的锁相环频率合成器设计与实现[J]. 电子工程师, 2003, 29(1): 44-46.

[4] 陈科, 叶建芳, 马三涵. 基于DDS+PLL技术频率合成器的设计与实现[J]. 国外电子测量技术, 2010, 29(4): 43-45.

[5] Analog Devices Inc. Integrated Synthesizer and VCOADF4360-8[EB/OL]. (2004-12-01) [2010-11-16]. http://www.analog.com

[6] 尹伟. 基于DDS和PLL频率合成器的研制[D]. 北京: 北京交通大学, 2007.

[7] 林巧莉. 基于ADF4360系列的小型化频率合成器设计[J]. 电讯技术, 2008, 48(10): 85-86.

[8] 陈景文. 基于ADF4360-4锁相频率合成器的混频[J]. 现代雷达, 2008, 30(1): 84-86.

[9] 樊战友,樊西青,张首刚. 基于AD9956的任意频率合成器研制[J]. 时间频率学报, 2010, 33(2): 112-113.

[10] 张帆, 胡永辉, 何在民. 一种基于GNSS的可驯频标的设计与实现[J]. 时间频率学报, 2013, 36(1): 28-29.

A phase locked loop frequency synthesizer based on ADF4360-8

XIE Liang1, 2, LU Xu1, 2, WU Cheng-ying3, YANG Jian-qing1,2, FAN Zhan-you1

(1. National Time Service Center, Chinese Academy of Sciences, Xi′an 710600, China; 2. Graduate University of Chinese Academy of Sciences, Beijing 100039, China; 3. Hubei University for Nationalities, En′shi 445000, China)

For satisfying the engineering needs, a phase locked loop frequency synthesizer with high stability and low phase noise is designed and implemented based on the phase locked loop chip ADF4360-8.The design principle, hardware constitution, software design and the implementation are described. Some main chips and the key circuits are introduced with emphasis. The amplitude of 100 MHz output signal for the frequency synthesizer reaches 2.16 V(peak-peak), being able to directively drive the TTL circuit. The test results show that the output signals of the frequency synthesizer are characterized by good stability, low noise and high amplitude.

frequency synthesizer; phase locked loop; phase noise; VCO

TN742

A

1674-0637(2013)02-0075-09

2012-07-11

国家自然科学基金资助项目(10773012)

谢亮,男,硕士研究生,主要从事高精度时间同步终端设计研究。