视频编解码器H.264的DSP实现与优化

2013-06-13杨贵新谷志锋梁丽娟

杨贵新,谷志锋,梁丽娟

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.军械工程学院,河北石家庄050003;3.邢台学院,河北邢台054001)

0 引言

H.264是ISO/IEC MPEG联合ITU-T VCEG成立的联合视频组制定的一个全新的标准,H.264能面向各种应用场合,其算法本身也包含了丰富的基于压缩和网络传输的各种编码选项。它不仅具有优异的压缩性能,而且还有很好的网络适应性[1],这些都是在实时视频通信中十分重要的。TI公司所推出的新一代开发平台达芬奇技术,不仅提供了高性能和高集成度的处理平台,而且还有一套开放的音视频标准开发框架,可以有效地降低开发周期和成本,非常适合于数字音视频方面的研究和应用开发。因此,把高性能的达芬奇平台作为多媒体数据处理平台,以H.264视频压缩标准作为多媒体的软件实现算法,通过两者的结合实现一个高效的编解码器。

1 硬件平台设计

1.1 TMS320DM6446

TMS320DM6446处理器芯片是由TI公司推出的高性能数字媒体集成芯片,内部集成了一个600 MHz工作频率的DSP核和一个300 MHz工作频率的ARM926核。ARM核负责处理系统控制和运行操作系统功能,DSP核主要实现语音和视频编解码功能,DSP核和ARM核可以通过内部寄存器的内存映射来交互。TMS320DM6446除了包含一个ARM926核和64X+的 DSP核外[2],还包含有一个视频处理子系统;此外,它还有丰富的外设资源:USB2.0接口、以太网MAC、DDR2控制器、存储卡接口和IDE接口等。非常适合应用在视频、多媒体及带多媒体功能的其他设备中。

1.2 硬件平台框架

H.264视频编码器是基于DM6446核心处理器实现的,其目标是保证数字视频图像资源的高质量、高可靠性及视频数据的互联互通。整个编解码器由视频采集子系统 TVP5150、DM6446处理器模块、FPGA模块、内存模块DDR、Flash及以太网和UART接口等组成,系统结构框图如图1所示。

图1 系统硬件平台

系统的工作过程如下:系统上电复位后,从Flash存储器加载程序到DDR内存,首先完成对各个功能芯片的初始化和外围硬件的配置工作,开始进行视频的采集,从摄像头采集到的模拟视频信号经过TVP5150转换为数字信号,送入DM6446的视频通道,处理器将接收到的数字视频信号用H.264标准编码压缩[3],将压缩码流封装成IP包经网口输出传输到对端主机上。同时DM6446也接收来自以太网的压缩多媒体数据,进行解包,分离出数字视频信号,进而按照H.264解码,最后输出显示和播放。

2 系统软件设计

2.1 达芬奇软件双核通信

TI提供的达芬奇软件框架可以分为3层:应用层、信号处理层和 I/O层,其中应用层通过 VISA API来调用DSP侧的算法,通过EPSI API来访问和操作其外设。信号处理层通常都运行在DSP一侧负责信号处理,包括音视频编解码算法、Codec Engine、DSP的实时操作系统DSP/BIOS等。I/O层就是针对达芬奇外设模块的驱动程序开发。

在达芬奇软件中,完成ARM与DSP之间双核通信是通过调用Codec Engine的VISA API接口函数完成的。Codec Engine通过这套API为算法的执行提供了一个标准的软件架构和接口。

VISA接口中的*_create()函数的可以用来传递初始化算法的相关参数,这些参数一般是一些通用的编码参数。也可以使用*_control来传递算法的动态参数。

采用VISA接口中的*_process()函数传递编码参数如H.264编码,对视频数据进行压缩处理。

2.2 视频编解码实现流程

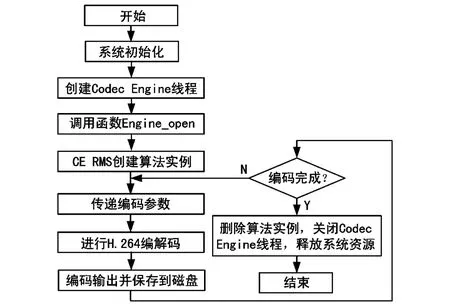

本设计中ARM端主要负责读取源图像数据和存放传输编码后文件,以及读入编解码参数等,DSP端集中完成编码类型的识别、视频编码及参考帧的存放等处理。ARM端读完一帧图像后通过VISA接口调用DSP端的H.264编解码算法来执行一次编解码。视频编解码实现流程如图2所示。

图2 视频编解码实现流程

3 H.264关键模块的优化及结果分析

3.1 整数DCT变换及DSP实现

H.264采用一系列新的压缩方法,获得了更好的压缩效果。标准中的整数离散余弦变换(DCT)和量化与先前的标准有很大的不同[4]。下面简要介绍传统的DCT变换以及H.264采用的整数DCT,着重探讨DSP的代码优化方法。

3.1.1 传统的DCT变换

二维DCT及其逆变换定义为:

式中,Xij是N×N图像块X中第i行第j列元素;Y是DCT系数。

3.1.2 整数DCT变换及优化算法

H.264对输入图像采用基于块的变化编码,但与之前的8×8点DCT变换不同,H.264采用了新的整数变换算法,以4×4像素子块为单位,在变换和反变换过程中只包含整数运算[5],这也是H.264标准区别于其他标准的重要不同之处。整数变换算法采用了全新的变换核和量化公式,变换可以通过16位运算来实现,有效地较低对存储器的要求,同时简化了运算步骤,在计算时只使用加法和移位运算,而无须使用乘法运算。使用这种算法做变换和反变换同样是可逆的,不存在误匹配问题。

矩阵形式的DCT定义如下:

Y=AXAT;X=ATYA其中X为图像或残差值的矩阵,Y为相应的频率点的DCT系数矩阵,变换矩阵A的系数为:

式中,a=c=1;b=2。

可以将矩阵乘法运算改造成2次一维整数DCT变换,例如先对图像或其残差块的每行进行一维整数DCT,然后对经行变换的块的每列再应用一维整数DCT,而每次一维整数DCT可以采用一维快速运算,以节省计算时间,其运算过程如表1所示。定义x(0),x(1),x(2),x(3)为输入的一行或一列残差数据;W(0),W(1),W(2),W(3)为正变换后的系数;xx(0),xx(1),xx(2),xx(3)为反变换后的系数;u,v,y,z为一维变换所生成的中间变量。

表1 整数变换与反变换一维算法运算过程

一维快速算法利用了矩阵乘法中的重复单元,将这些冗余计算储存起来,很大程度上减少了运算次数,易于在DSP处理器上实现。

3.2 H.264的DSP实现及优化

将编码算法移植到达芬奇平台后,还要根据达芬奇平台的特点对代码进行优化,如果不进行优化,其代码运行效率将很低,达不到实时编码要求。对代码的优化[6],主要有以下几个步骤:编译优化、系统优化和汇编优化。

3.2.1 编译优化

属于对代码的全局性优化,通过对编译选项的设置来对编译进行优化。根据达芬奇平台的特点,采用的编译选项包括:-o3/-pm/-ms0。以上选项中,-o3是对文件的优化;-pm是把所有源文件合成一个模块来进行程序优化,它可以过滤掉一些没用的函数;-ms0选项可以减少代码的尺寸。

3.2.2 系统优化

由于达芬奇处理器DM6446的DSP处理器采用了2级存储器结构,这样可以平衡2级不同大小和性能的存储器之间的资源和性能。其中一级存储器是靠近处理器,所以它的处理速度比较快,而二级处理器的速度就只有它的一半。在实际使用时,所有的代码和数据是不可能全部装入到速度最快的一级缓存中去的,所以对系统进行优化的主要目的就是解决合理的分配存储器资源来提高代码运行效率。

3.2.3 汇编优化

主要是针对算法中的一些影响到整个算法效率的部分,有必要采用线性汇编来重新编写,取代一些执行效率不高的代码。以DCT代码的汇编实现为例:虽然使用一维快速DCT算法能提高编码的效率,但DCT变换和运动估计的计算量还是很大。为了减少其运算量,采用了汇编来改写快速DCT函数,运动估计模块和量化模块。整数变换算法在DSP上的优化,主要解决的是编码效率问题。如何提高编码速度、减少算法实现的时钟数,是对算法进行优化的主要目标。为了提高速度和效率,进行软件开发时,采用C语言嵌入汇编代码的混合编程方式,具体的优化方法是:将乘法运算改为移位或是加减运算,打开软件流水,以及展开循环以减小时钟周期数,充分利用功能单元等。

3.3 实验结果分析

通过对代码进行各项优化措施后,使用代码剖析工具Profiler或者printf函数统计出某段函数耗时进行优化效果的分析[7];将关键函数的运行速度在优化前后进行了对比,如表2所示。

表2 优化前后关键函数测试结果对比

表2是对DSP优化前后的性能进行分析比较,通过几个关键模块在优化前后占用的时钟周期数的统计,可见在循环次数较多的情况下,采用汇编语言编程的效率比采用C语言提高10倍以上,这是由于对于视频编解码这样的数据密集型应用,伴随着频繁的数据访问,对于高性能的DSP芯片来说,数据瓶颈成为制约程序效率的最主要因素。通过线性汇编,有效提高了系统的执行效率。算法的运行速度和存储器占用情况都有了比较大的改善,为视频编码及其他应用留下了足够的处理空间。

4 结束语

上述提出了基于TI双核处理器DM6446为核心的应用平台,分析了双核通信的原理及过程,实现了H.264视频编解码算法;并针对DM6446芯片的特点和H.264视频编解码算法自身的特点,对程序进行了优化。测试结果表明,优化效果明显,经过优化后的编码器执行效率更高[8],且能满足对图像的实时性处理要求,本设计具有较高的数据吞吐能力和处理速度,能够满足实时性的要求;应用平台经过长时间的运行测试,视频编码的传输性能可靠,其涉及的关键技术可为实际工程应用研究提供有力的技术参考。

[1]毕厚杰.新一代视频压缩编码 H264/AVC[M].北京:人民邮电出版社,2005.

[2]陈 玉.TMS320系列DSP硬件开发系统[M].北京:清华大学出版社,2008.

[3]侯建华.基于Davinci DM6446处理器的DVS的设计与实现[J].中南民族大学报,2009,28(1):72 -75.

[4]彭超男,王京玲,张 勤.H.264编码器在TMS320DM642上的优化[J].中国传媒大学学报(自然科学版),2007(1):8-10.

[5]刘 峰.视频图像编码技术及国际标准[M].北京:北京邮电大学出版社,2005.

[6]彭启琮.达芬奇技术—数字图像视频信号处理新平台[M].北京:电子工业出版社,2008.

[7]白茂生,田裕鹏.H.264在DSP上的实现及优化[J].电子测试,2008(2):21-22.

[8]周长发,周建欣.多媒体编程技术与实例[M].北京:电子工业出版社,1999.