基于自主可控计算平台的信号采集处理系统设计与实现

2013-06-10赵星汉

赵星汉,于 洋

(中国电子科技集团公司第27 研究所,郑州 450047)

0 引 言

随着现代战争向陆、海、空、天、电多维化发展,信息系统的攻防变得至关重要。信息系统的高效、安全已经成为了决定现代战争成败的关键因素。对于我国国防建设来说,传统的信息系统硬软件绝大多数依赖进口,其设计和生产是我国不可控的,这就为国防建设造成了巨大的安全隐患。

近些年,随着国家的不断重视,关乎国防安全的自主可控信息化技术发展,逐渐成为了国防建设的重中之重。胡锦涛总书记明确指示:“要大力推进自主可控信息系统建设与应用,摆脱核心信息技术受制于人的局面”的重要指示。在政府的大力引导下,我国的自主可控计算机领域得到快速的发展,自主研发生产的计算机已经在国防、航天等领域得到广泛的应用。

本信号采集处理系统是我国某重点课题监控分系统的重要组成部分,在设计上具有一定的针对性。同时,由于信号采集处理技术引用的广泛性与本设计的通用性,本项设计在其他自主可控计算平台研究与信号处理领域的研究设计上也有一定的参考借鉴意义。

1 系统原理与构成

该系统是某大系统中监控分系统的一部分,系统总体对系统功能、性能、功耗、体积、硬软件国产化率等关键指标均作了明确的要求。经课题组分解,本系统关键设计输入如下。

(1)完成对大系统中某单路0 dB 高频信号的采集、处理与显示,采集速率:2 GHz,采集精度:8 bit;

(2)通过外部接口完成对外围设备的远程控制;

(3)可实现对采集信号的存储,内部存储空间不小于2G;

(4)显示方式:10 寸液晶显示,分辨率1024*768;

(5)输入方式:定制键盘;

(6)系统软件全自主化,元器件国产化率80%以上。

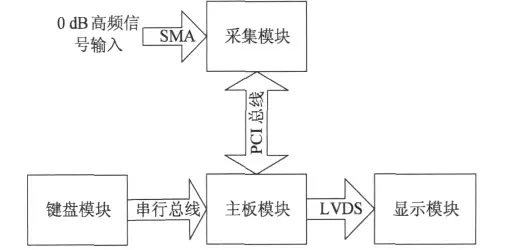

经研究,确定本系统硬软件构成模块如图1所示。

图1 信号采集处理系统硬软件构成示意图

本系统由硬件和软件两方面组成。其中硬件组成包含负责单路信号采集的采集模块、负责将采集处理后的数据显示的显示模块、负责用户输入的键盘模块,以及作为承载平台的主板模块作为主要硬件构成,四部分统一安装于铝合金系统箱体内;软件构成主要包含操作系统及包含各项硬件驱动工作的BSP(板级软件支持包),以及显示与控制信号采集与处理的监控软件。

系统的工作流程,如图2 所示。

本系统信号输入为0 dB 高频信号输入,通过位于采集模块上的SMA 插口采集成为数字信号,经过处理后通过PCI 总线与主板模块发生交互,经过主板模块上的中央处理器处理后转换成用户可用的图形传输至显示模块上进行显示。用户可通过键盘模块上的按键设置命令与切换显示形式对整个系统进行控制,完成操作过程。

图2 系统工作流程示意图

3 自主可控计算平台设计

中科龙芯公司研制的龙芯系列处理器,已经在技术及稳定性方面逐渐成熟,目前龙芯系列处理器从开始的龙芯1 代处理器,发展到现在的龙芯3 代处理器,产品系列也逐渐丰富。在软件方面,龙芯公司作了较多的研究工作,采用MIPS CPU 最常用的BIOS-PMON2000,并在其基础上进行了一些完善工作,支持BIOS 启动配置、内核加载、程序调试、内存寄存器显示、设置及内存反汇编等。支持Linux 及VxWorks 操作系统。可以说,龙芯处理器的软件支持已经比较丰富和成熟。

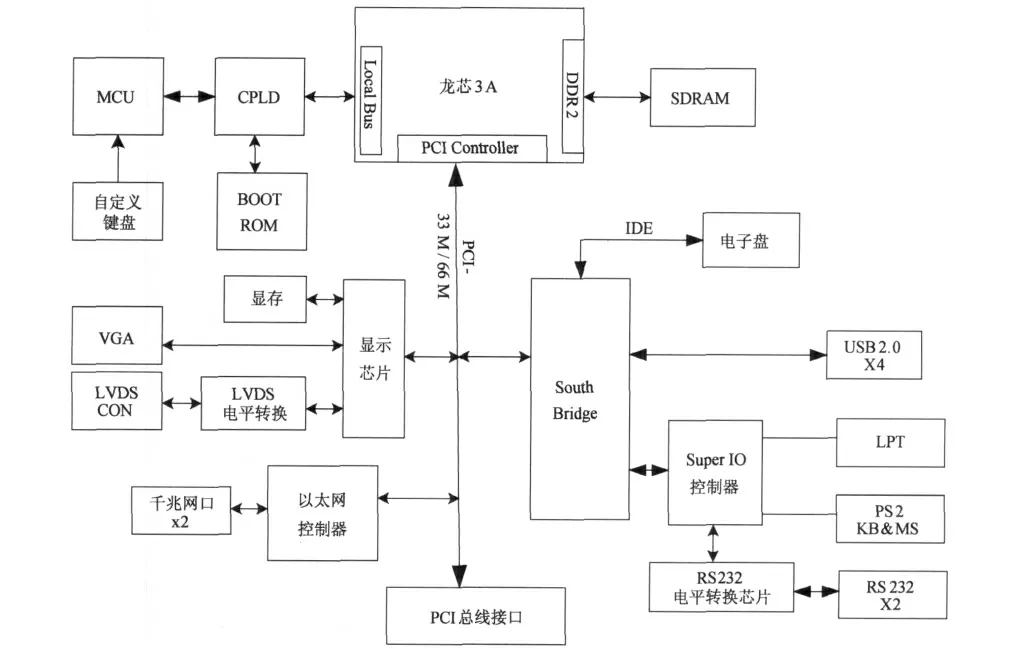

考虑到项目总体要求中对功耗和体积均有一定的要求,因此自主可控计算平台中主CPU 选用中科龙芯公司的龙芯3A 处理器。龙芯3A 是我国具有完全自主知识产权的四核CPU,采用65 ns 工艺,RISC 架构,兼容MIPS 指令,工作频率900 MHz ~1100 MHz,集成两个扩展内存控制器,单颗最大功耗15 W,满足系统的总体需求。

由于系统运行的需要,利用集成于CPU 上的内存控制器扩展出512M 的SDRAM 作为系统的扩展内存。Local Bus 总线提供了一个简单的低速总线接口,用于连接系统ROM 和低速I/O 设备。为实现裸机的系统引导,故利用CPLD 外接一块FLASHROM作为BootRom 实现最初的系统引导程序存储。

考虑到项目中需要一定的图形处理,以及外接真彩LCD 显示屏的需要,故选取集成2D 图形控制器的芯片作为显示主芯片,搭配64M DDR 作为显存。显示芯片通过LVDS 电平转换以LVDS 形式连接至机箱上的10 寸LCD 真彩显示屏,最大分辨率1024* 768。

程序存储功能通过外接2 Gb 容量电子盘实现,电子盘以IDE 总线连接至南桥芯片上。南桥芯片还能提供4 个USB2.0 控制器以供系统USB 扩展所需,其余、串口、并口、PS2 接口等统一通过SuperIO控制器连接至南桥芯片上。

南桥芯片,显示芯片,以太网控制器及信号采集所需要的采集板,均以PCI 总线节点的形式挂接在系统PCI 总线上实现系统整体的交互。PCI 总线因其与存储器之间的交互基本上通过DMA 模式,有一个突出的优点就是CPU 资源占用率低,因此它作为一种将周边设备与处理器高速结合起来的总线结构,得到了广泛的应用。PCI 总线电器驱动能力有限,每组PCI 总线上只能有效连接较少数量的PCI设备。为了提高PCI 总线驱动能力和扩展能力,获得较好的电器连接性能,PCI 总线结构的主板在扩展PCI 设备插槽的时候都会选择合适的桥接芯片以获得更好的连接性能。龙芯2F 处理器集成的PCI /PCI-X 总线控制器可以工作在主控制器模式或设备模式,总线仲裁最多支持7 个主设备。在该主板设计中,选择TI 公司的PCI2050B 芯片作为PCI 设备扩展桥,该芯片次级总线最多可驱动9 个PCI 设备,支持的PCI 总线位宽为32 bit,最高时钟频率为66 MHz,工作核心电压为3.3 V,兼容3.3 V和5 V PCI 信号电平环境。该主板系统中,CPU 作为仲裁器,PCI2050B 作为总线上的主设备之一。PCI2050B 次级总线上的扩展设备具有独自的PCI总线请求信号和允许信号,因此该扩展设备都可用作主设备与CPU 通信。

主板的网络控制器选用带PCI 总线接口的Intel 82546GB 双网口千兆网络控制芯片设计。芯片内部集成MAC(media access control)和PHY(physical layer)层功能,单芯片内集成两个全功能独立千兆网络接口,集成度高,为器件密集的主板设计节省了空间,并有利于布局布线,减少复杂线路带来的干扰,这两个接口可以通过芯片的引脚FL_DATA0 和FL_DATA1 来禁止和打开,该控制引脚可以连接至CPU的GPIO 或者南桥的GPIO 管脚,通过BIOS 控制这两个接口的通断。

该芯片通过PCI 总线与龙芯3A 连接,PHY 接口模拟信号通过网口变压器H5007 进行防护与隔离后连接到CPCI 背板,能够有效防护雷击、静电放电等现象引起的瞬时高压对网络控制器芯片的毁坏。

系统连接示意图如图3 所示。

图3 自主可控计算平台连接示意图

4 信号采集模块设计

本系统涉及的信号采集速率高达2 GHz,国产ADC 和高速信号处理芯片在技术上还不成熟,故采集系统的部分元器件只能采用国外成熟产品。但由于西方国家对话禁运等原因,2 GHz 采集速率的ADC 较难购买,价格也难以承受。因此,本系统拟采用并行时间交替采样,依靠两路1 GHz 的ADC 达到2 GHz 的采样速率。

所谓并行时间交替采样,就是在高速数据采集系统中并行设置多路ADC,使用频率相同,相位不同的采样时钟来控制多片ADC 交替、分时工作,然后对采样所得的高速数据流按照一定的顺序进行合并,这样就提高了采样速度。并行时间交替采样技术是唯一的一种对模拟输入信号没有限制的实时采样技术,可以突破当前的ADC 和相关器件频率的限制,实现超高速数据采集系统。采用这种方案,采样速率可以大幅度提高,理论上可以达到器件采样速率的总和。双通道并行时间交替采样过程如图4所示。

图4 并行时间交替采样原理图

系统设计方面,拟采用“高速ADC+高密度FPGA+高速接口”结构形式,在这种结构中,FPGA 作为系统的控制核心,控制ADC 的采样工作方式并实现高速数据流的分流缓存、有效信号检测和数据的传输。ADC 的采样数据通过FPGA 分流后,速率已降至后续处理单元可以接受的范围中,可通过高速数据传输接口PCI 总线传递给上位机PC 进行处理。此种结构PCB 面积和功耗相对较低,但所有的数据接收,缓存处理及与上位机的通信都要靠单片FPGA 完成,这将加大对FPGA 的压力。

信号采集模块的硬件构成如图5 所示。

图5 信号采集处理系统

ADC 芯片采用Atmel 公司生产的AT84AD001B,它是双通道ADC 芯片,最高采样率1 Gsps,分辨率8位。为了满足系统采样率的要求,需要两路ADC 以并行时间交替采样的方式工作于1 GHz,这样就要求系统有1 GHz 的高速采样时钟。高速系统对时钟的要求很高,时钟的抖动和相位偏差会带来数据上的错位,因此应选择温度稳定性和谐波抑制比较高的器件。这里选择MICREL 公司生产的高速差分时钟合成芯片SY89421,SY89421 是一个低抖动、高稳定时钟芯片,片内VCO 最大输出频率1.12 GHz。

5 Reworks 操作系统的特点

ReWorks 是中国电子科技集团公司第三十二研究所自主研制的、第一个提供VxWorks 兼容接口的嵌入式实时操作系统,采用面向对象和微内核技术开发,具有强实时性、可裁剪性和可伸缩性,并特别提供了VxWorks 兼容层,具体特点如下。

(1)微内核、可裁剪、可扩充性。ReWorks 的设计中不采用完全的微内核结构,而是采用一组环绕基核的类似于微内核的独立功能模块来建立可伸缩的操作系统。内核提供任务调度、对象管理等功能,而时钟、区域、分区、信号、事件、信号量、消息等作为可裁剪的、环绕内核的独立功能模块,可根据实时应用的需要进行裁剪。在Reworks 下,最小配置可小于100 K。

(2)强实时性和多任务。ReWorks 支持微秒级高精度时钟,最快响应时间可达15 ms,为正在等待消息、信号、事件或段的任务进入超时管理,为轮转调度提供时间片,在指定时间间隔以后或指定时间唤醒任务或发送一个时间报警给任务;提供高效的实时任务管理,支持多任务,任务数没有限制,上下文切换快速确定,有256 个任务优先级;任务的调度算法灵活,除了支持抢占式调度和时间片轮转调度两种常用的调度算法,还提供速率单调算法(RMA)保证任务调度性可预测。对任务间通信实现四种通信机制(消息队列、事件、信号量和异步信号),满足了任务间通信、同步和互斥的需要。

(3)支持多种网络协议。ReWorks 支持包括TCP、UDP、IP、ICMP 和ARP 等多种网络协议,可通过工业标准socket 编程接口进行访问;提供基于TCP/IP 的Internet 标准实现网络管理的管理信息库,并能和交叉开发工具一起,建立单机或多机目标系统的网络下载和调试工具;支持多种常见的Internet 应用协议如FTP、TFTP、Telnet 等。

(4)设备管理。I/O 设备通过设备驱动程序表进行管理,对设备的操作可抽象为初始化、打开、关闭、读、写、控制,当应用程序进行I/O 操作时,系统根据设备驱动程序表决定调用哪一个设备驱动程序进入点。

(5)中断管理。允许应用将中断服务例程(ISR),连接到硬件中断向量,通过提供允许从ISR退出时任务被抢占来改变任务执行的临界能力,许可快速中断响应时间,支持256 中断优先级。

(6)支持用户扩展。为了不修改内核而能够向系统增加额外的任务相关的功能,ReWorks 提供了任务创建、切换和删除的钩子函数。允许在任务被创建、上下文切换和任务被删除的时候额外的例程可被调用执行。在关键的系统事件里提供的扩展例程中,用户能够针对自己的实际情况,设计适应系统需要的前置处理,增强系统的功能。为满足开放性要求,ReWorks 提供符合POSIX 1003。1b 实时扩展标准规范的基本系统调用。包括:进程原语,消息队列,信号,内存管理(页面锁定),调度控制,文件目录,I/O 原语,语言服务,以及目录管理等。

6 系统软件在Reworks 上的应用

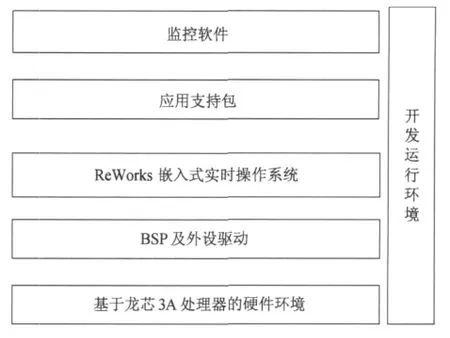

根据设备总体功能、运行环境、系统信息交互等需求,系统软件包括BSP 及外设驱动,ReWorks 实时操作系统支撑环境层软件组成,各层软件按照构件化模式进行设计,实现软件的按需组装和快速、灵活配置。系统的体系架构如图6 所示。

图6 系统软件的体系构架示意图

ReWorks 嵌入式实时操作系统为整个软件系统提供包括内核、设备驱动、通信协议、图形引擎等,是应用软件运行环境的重要组成部分,为上层应用软件提供对底层物理硬件的抽象和封装,组织和管理软硬件资源,控制程序执行流程,提供系统调用接口、驱动程序等,为方便与其他软件(如嵌入式数据库、集成部署框架)集成,ReWorks 嵌入式实时操作系统还为上层软件提供标准的硬件访问接口和其他的基本操作系统服务。

作为实时操作系统,Reworks 编程的核心在于任务的制定与流程调度。系统程序对逻辑和时序要求比较严格,不仅任务响应须实时,而且须在规定的时间内完成事件的处理。Reworks 提供了任务的创建、关闭、挂起、恢复以及获取任务信息等操作接口。不同的任务依靠任务制定时的TCB 数据结构体确定优先级,优先级为一个无符号的字符数(0 ~255),0 最高,255 最低。

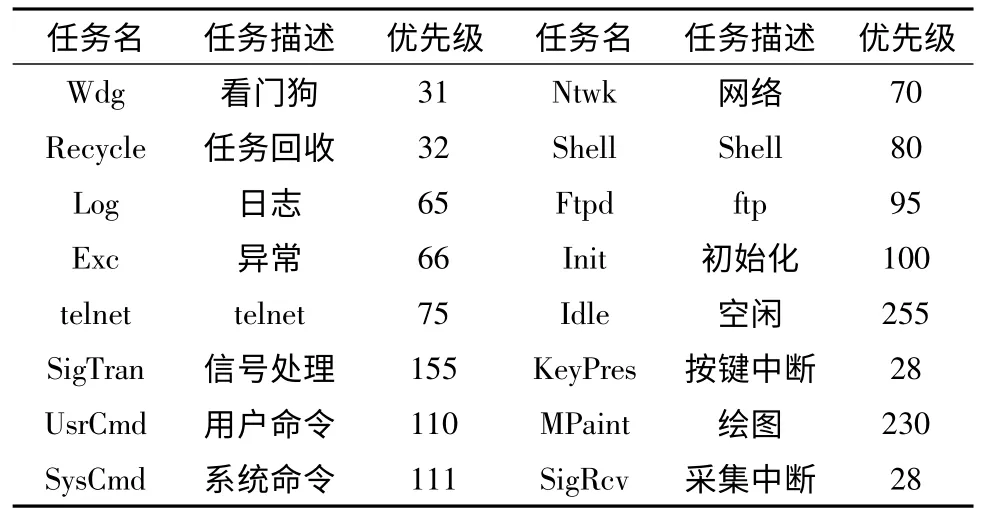

本系统监控程序任务相对单一,任务耦合度不高,因此系统任务调度采用基于优先级的调度,关闭轮转调度。部分任务优先级安排见表1。

表1 任务的优先级安排表

在监控软件编写和调试过程中,为便于程序功能与环境的扩展,软件设计时控制参数不能提前确定,确定后也须根据实际情况修正。Reworks 系统采用文件实时存储、读取的方式,保证控制参数的有效性。当系统上电时,采用最新的配置文件初始化。如模拟采集数据的非线性化校正,采用配置文件中的区间分割曲线作二次映射后,即可实现对配置的合理调控。

ReWorks 具有与DOS 兼容的文件建立与读写功能,可实现类似DOS 下的文件读写操作。控制软件先在板载的电子盘内建立dosFs 文件系统,即可通过I/O 读写函数读写文件。数据的存储按照事先定义的结构类型进行,读出时取出字节到相应的结构类型中即可。

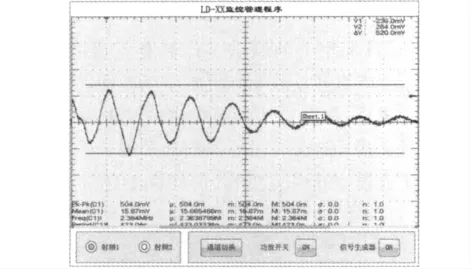

7 实际测试运行结果

系统在研制完成后进行了,对系统性能、可靠性进行了全面的测量,监控界面如图7 所示。经检验,本系统能较好的完成单路2 GHz 频率8 bit 精度的采集任务,并能将信号在软件上显示和依据程序设置算法进行处理,除数据处理过程外,常用操作基本没有明显的延迟。系统常温烤机工作72 小时,无明显过温现象,无发生任何死机崩溃故障,基本满足可靠性需求。

图7 系统监控软件工作界面

按照系统最终成型后国产化率统计,虽然采集模块某些部件采用了国外进口器件,但本系统总的元器件国产化率达到了91%,软件系统实现了纯国产,满足系统总体关于国产化的要求。

8 总 结

本系统采用自主可控的龙芯计算平台、国产Reworks 操作系统与部分自研的软硬件,实现了2 GHz 采样率,8 bits 精度要求的信号采集处理系统。系统软硬件国产化率高,工作稳定可靠,可满足大部分监控系统设计的需要。

但本系统还无法做到完全自主化,高速信号采集部分还有某些关键元器件要依赖进口,但按照如今国产元器件发展速度来看,本系统做到完全自主化应该为时不远。

[1]吴量. 高速数据采集系统的设计[J]. 电子测量技术,2006(03):92-93.

[2]郑成波,杨科技.一种基于CPCI 总线的高速雷达回波信号采集系统[J].电子设计工程,2011(18):130-132.

[3]陈钟,刘鹏,刘欣. 可信计算概论[J]. 信息安全与通信保密,2003(11):17-19.

[4]田晓霞,阮林波,田耕. 2Gsps 高速数据采集系统的设计与实现[J]. 微计算机信息,2011(03):49-50.

[5]JOE SAWICKI. 从PCB 和IC 设计领域管理信号完整性[J]. 电子产品世界,2006(01):58.

[6]管洋. ReWorks 嵌入式操作系统在船舶PMS 上的应用[J]. 船舶工程,2010(01):41-44.

[7]陈世奎.基于龙芯2F 处理器的CPCI 主板设计[J]. 测控技术. 2011(08):107-111.