基于多处理器的可识别方位引信信号处理系统

2013-04-25苏宇逍

陈 彬,苏宇逍

(1.中国空空导弹研究院 第8研究所,河南 洛阳471009;2.中国空空导弹研究院 总体部,河南 洛阳471009)

在现代战争模式中,导弹定向爆破能大幅提高作用于目标方向的杀伤能量,使导弹获得更大的命中和毁伤概率、作战能力。引信作为导弹的重要组成部件,具有方位识别能力是实现导弹定向爆破的前提条件。信号处理系统作为引信的核心部件,是方位识别功能和目标检测功能的主要实现单元。其结构和性能对引信的整体性能有着至关重要的影响。随着FPGA、DSP技术的发展,数字信号处理技术在引信中的应用大幅增强了引信信号的处理能力,有利于方位识别引信的实现。文中在采用FPGA+DSP架构的基础上,实现一种具有8象限方位识别能力的引信信号处理机。

1 可识别方位引信系统原理

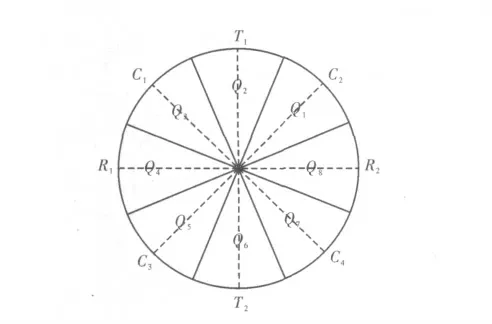

本方位识别算法旨在实现引信周向8个象限的方位识别,利用双收双发收发分离共4根天线,在导弹圆周方向形成360°均匀探测场。其布局如图1所示,T1/T2为发射天线,R1/R2为接收天线,根据方位识别算法,可实现Q1~Q8共8个象限的方位识别。

图1 天线布局及各象限位置关系图

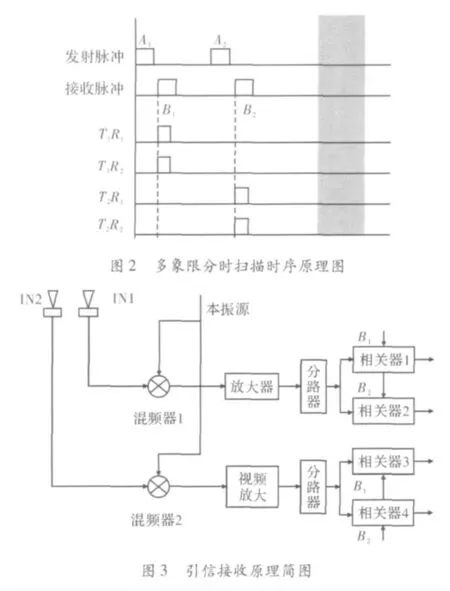

根据时分复用原理得到4个通道的多普勒信号,是多象限分时扫描的最终目的。算法中的多象限分时扫描采用接收支路同时接收回波,再利用接收脉冲相关特性将接收到的回波进行分离,这种定向探测系统实现相对简单,收发隔离度高,并且能够降低回波多普勒的距离副瓣[1]。图2为多象限分时扫描时序原理图,图3为引信系统实现框图。

2 信号处理系统设计

2.1 功能要求

设计中定向探测引信的信号处理器是一个功能复杂的处理器,采用数字频域处理方式实现,包括A/D转换电路及信号处理模块,实现对多普勒信号的采样、量化,数字信号的FFT、CFAR处理,完成对目标的检测、启动判断、干扰判别。其功能包括:(1)对4路多普勒信号进行数字化。(2)依据4路多普勒信号,实现时频转换及相关频域处理。(3)在符合目标检测判据时给出目标存在信号。(4)将多普勒信号的频域峰值作为目标能量信息,对4路目标能量信息进行比较,实现引信周向8个象限的方位识别[2]。

2.2 数字信号处理系统工作原理

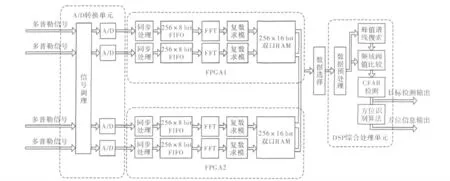

目标或环境回波经过引信接收前端,根据分时扫描原理得到4路多普勒回波,4路信号同时输入信号处理电路。4路多普勒信号首先经过A/D采样,形成回波时域数据,然后进行FFT频域分析和坐标系转换,基于线性逼近近似算法的求模运算、多处理器协同工作下的数据传输缓存,最终输入DSP芯片中进行目标检测和方位识别,得如果满足一定的信噪比则给出目标存在信号,在目标存在的前提下继续进行目标方位识别,输出目标方位信息。设计信号处理系统采用了FPGA+DSP架构,由FPGA完成4路FFT运算,由DSP完成目标检测、脱靶方位识别,由2片FPGA芯片和单片DSP芯片构成了一个多处理器协同工作的数字信号处理机。图4给出了本设计中引信信号处理单元的流程框图。

图4 数字信号处理功能框图

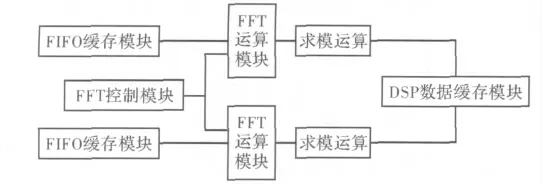

2.3 FPGA单元设计

引信信号处理系统中两片FPGA芯片,主要实现4路多普勒信号的时频域转换以及频域信息的预处理,要求4路并行处理。FPGA芯片选用两片Altera公司的EP1K100QI208-2,分别记为FPGA1和FPGA2,单片FPGA进行两路FFT运算、求模运算以及计算结果的缓存[3]。模块化思想能够大幅优化数字信号处理系统设计,增强代码的可读性和维修性,设计中广泛采用了模块化设计思想,对信号处理中的各项功能合理划分。单片FPGA内部主要包含FIFO缓存模块、FFT时频转换模块、求模运算模块、DSP数据缓存模块。图5为单片FPGA内部系统框图。

图5 单片FPGA系统框图

2.4 DSP单元设计

引信信号处理系统设计中选用了TI公司的F2802芯片,作为FFT运算后续处理检测、判别的主处理器。F2812有内置Flash存储器,无需外挂存储芯片。F2812是一款高速成熟的DSP处理器,具有很强的数字信号处理能力,最高核心频率可达150 MHz,程序中系统时钟设定为100 MHz,既能满足信号处理的实时性要求,同时又保证了器件工作的稳定性。

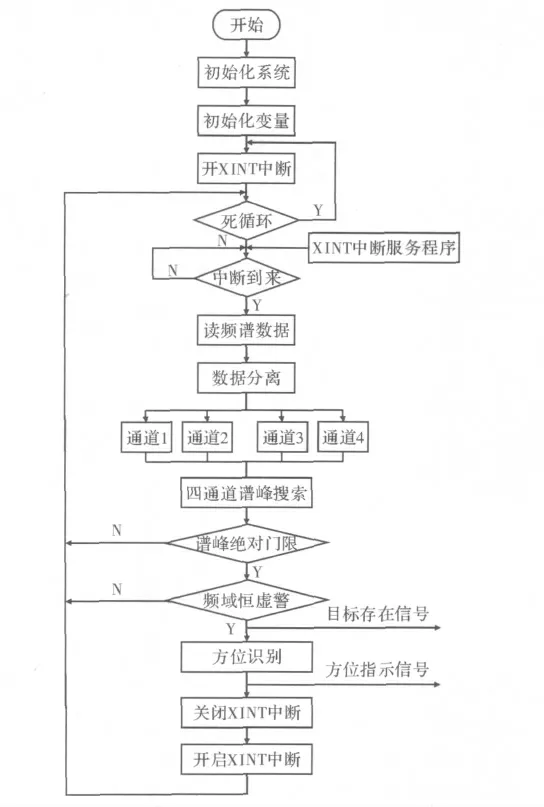

DSP信号处理器接收到FPGA发送的中断请求后,从FPGA双口RAM中读取128点频谱x(k),对x(k)进行逐点选大,找到目标所在频谱位置。将单元内其他谱线能量相加平均作为噪声能量N。为弱化信号截断引起的频谱泄漏,计算噪声能量时,去掉最大谱线两侧相邻的两根谱线,将最大谱线及噪声能量的比值与既定门限进行比较,判断目标是否存在,若不存在,则进行下一帧运算;若存在,则进入方位识别程序,进行方位识别,若能识别出目标方位,则给出二进制3位方位指示信号3`b000~3`b111,分别对应导弹周向8个方位。DSP软件处理流程图如图6所示。

3 关键技术及其实现

3.1 方位识别算法的具体实现

根据文中方位识别算法设计,可以得到可识别方位信号处理系统的测向工作原理,但判据的确定仅是理论的推导,只有对实际多普勒回波的时域和频域特征进行分析,从中得出各通道多普勒信号,对应频谱谱峰与实际目标方位的对应关系。设计中,基于多普勒比幅算法的方位识别功能最终判据的确定是一个不断试验、根据试验结果又去不断修正的过程,由于DSP芯片对于复杂算法的实现有着较好的灵活性,经过不断的试验和软件优化,最终得到一个稳定可靠的可识别8象限方位信息的引信信号处理系统。

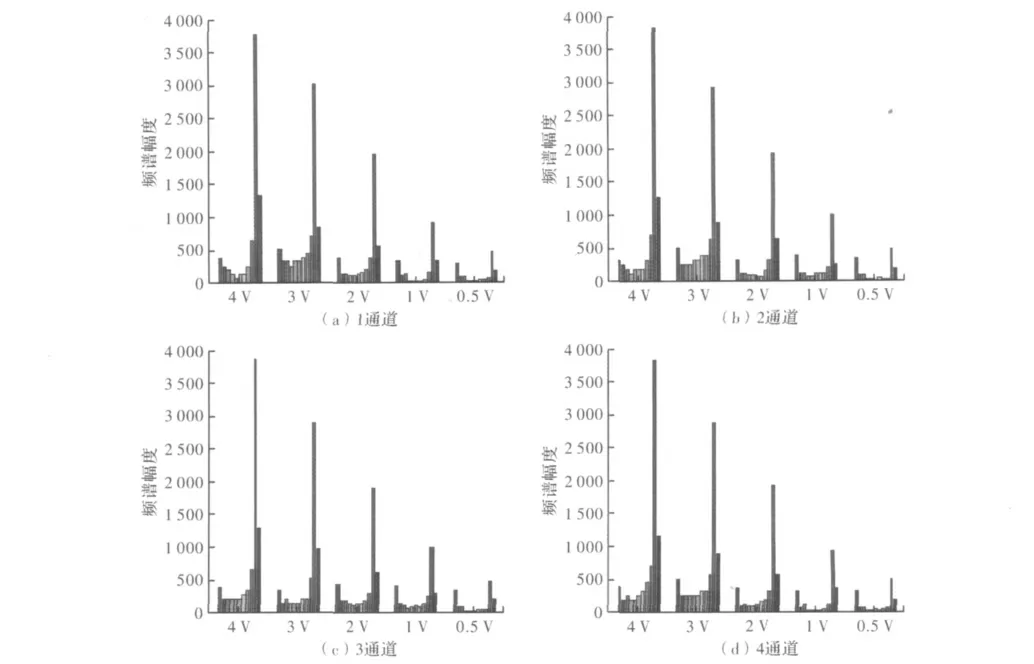

采用多普勒信号最大值比较法来识别目标脱靶方位,即根据4路多普勒信号进行频谱分析后,按照频域能量比幅的方法进行方位识别,4通道多普勒接收机和信号器多通道处理之间的指标一致性将影响测向的精度,对接收机和信号处理器的通道一致性进行了标定,如图7所示。

61图6 DSP工作流程图

3.2 多处理器协同工作下高速数据传输

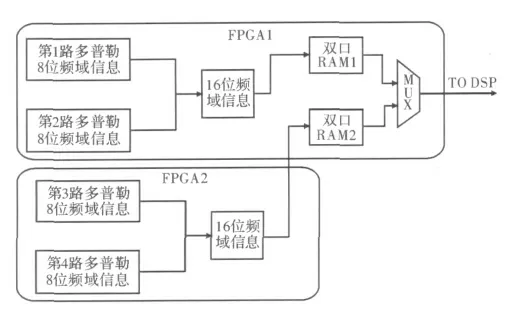

由于设计中采用FPGA+DSP的系统构成方式,由两片FPGA完成4路多普勒信号的FFT运算、求模运算等,由DSP完成后续复杂算法计算。对于每帧运算,经2片FPGA处理得到的4路信号频域信息能够快速、同步、准确的传到下级DSP芯片中,是多处理器设计中的难点。

以256点,8位FFT运算为例,在两片FPGA进行完FFT运算和模值运算后,得到4路多普勒信号的频域信息,共4路×256点×8位数据,这些数据之后要进行频域单元平均恒虚警算法判断是否存在目标,以及用消比幅算法来判断目标的方位信息。而进行下一步处理,首先要完成4路频域数据的传输问题,在信号处理系统设计中,数据处理有实时性处理的要求,并且FPGA与DSP之间只有一个数据通路,如果将4路数据串行传输,传输时间将大幅增加,直接导致信号处理系统不能满足实时性要求。基于这样的考虑,在传输数据之前首先将4路×256点×8位数据,转化为1路×512点×16位的频域数据,通过DSP的16位数据通路传输数据,这种数据预处理方法需要将两片FPGA的数据进行融合,在缓存模块的软件设计中,首先将FPGA1和FPGA2中的两路FFT运算结果2路×8位融合成1路×16位数据,再将FPGA2中的处理结果传至FPGA1中,将两片FPGA的处理结果分别存入两个双口RAM中,两个存储器统一由DSP地址总线控制,增设存储器选择端,同一时刻仅有一个RAM向DSP传输数据。多级数据缓存示意图如图8所示。

图7 4通道多普勒信号频谱分析对比图

图8 多级数据缓存原理框图

根据上述原理进行数据缓存设计,本系统能够快速、4通道同步、准确地将频域处理结果送至下级运算中,保证了系统的准确性和快速性。

3.3 高速信号处理中的多级流水设计

由于引信与目标高速交会,要正确识别目标、精确控制炸点,就必须在较短的时间内处理大量的回波信息。定向毫米波引信数字信号处理立足于干扰条件下探测识别目标的设计理念,更需要在短时间内对多个象限的回波信号做多批次的处理并进行特征积累,完成干扰模式的识别和目标的精确检测及定位。因此,对信号处理的快速性、实时性要求更高。

为保证系统工作的实时性,在整个信号处理系统设计中采用了多级流水线处理,首先将整个信号处理系统分为时频转换和目标检测、方位识别两级大流水线,在FPGA的设计中,将整个时频转换也分为数据接收缓存、FFT运算、求模运算、数据输出缓存等模块。在每个模块设计中,又将各模块运算进行分级处理,多级流水线处理保证了整个信号处理系统的实时性和快速性。多级流水的思想利用了FPGA内部的丰富资源、面积换取了速度,大幅提高了系统关键路径的最高时钟频率fmax。

4 结束语

文中设计了一种基于多处理器的数字信号处理机,不仅实现了引信的频域目标检测算法,同时实现了基于多普勒比幅算法的方位识别算法,具有8象限的方位识别能力,信号处理器装调完成后,对信号处理电路进行了不同交会状态的数据回放,结果表明,该信号处理器能够在不同的交会条件下,准确给出目标存在信号和目标方位信息,实现8象限的目标方位识别。

[1] 刁海南.判断导弹脱靶方位的多普勒信号比幅算法[J].宇航学报,2003,24(3):239-243.

[2] 张清泰.无线电引信总体设计原理[M].北京:国防工业出版社,1985.

[3] 吴继华,范丽珍.Altera FPGA/CPLD设计[M].北京:人民邮电出版社,2005.