一种基于FPGA的DDR SDRAM控制器的设计

2013-04-25陈根亮

陈根亮,肖 磊,张 鉴

(1.合肥工业大学 电子科学与应用物理学院,安徽 合肥230009;2.温州大学 物理与电子信息学院,浙江 温州325035)

随着超大规模集成电路技术的成熟,以及数字信号处理技术的广泛应用,高速大容量缓存逐渐成为一项关键技术。DDR SDRAM即双倍速率同步动态随机存储器,它采用地址复用技术,在时钟的上升沿和下降沿均能触发数据进行传输,并且能与系统保持良好的同步性。DDR SDRAM以其大容量、低成本以及更高的数据传输质量等优势,逐步取代SDRAM而被各集成电路制造厂家所青睐。而要实现各微处理器和数字信号处理器的存储器接口与DDR SDRAM接口相连接,必须要借助DDR SDRAM控制器才能实现控制读写等功能。微电子制造工艺的迅猛发展使得FPGA的集成度和性能也不断提高,在各种嵌入式系统中的应用也越来越广泛。FPGA内部集成了DDR触发器、PLL锁相环等逻辑资源,并且其引脚均能满足SSTL-Ⅱ电器特性的要求,因此FPGA是实现DDR读写控制的最佳平台,研究如何利用FPGA实现DDR SDRAM控制器具有重要的现实意义。

1 DDR SDRAM的工作特性

一个DDR SDRAM通常包含有地址总线15个、数据总线16个、数据捕获探针2个、写掩码信号线2个、差分主控时钟线1个、时钟使能信号线1个、以及命令信号线4个:CS_N,RAS_N,CAS_N,WE_N[1]。

1.1 DDR SDRAM的初始化

DDR SDRAM的工作模式必须由初始化操作来配置,初始化的过程通常包含:首先发送一个Precharge all bank命令完成对所有块的预充,接下来是两个或多个Auto Refresh命令使DDR SDRAM进行自动刷新,最后由模式配置命令完成对DDR SDRAM内部模式设置寄存器的配置。

1.2 访问存储单元

为减少输入输出引脚的数量,初始化完成后要对各个Bank中的阵列进行寻址以访问存储单元:在Read/Write状态下先由Active命令激活相关的Bank,并锁存其行地址,当Read/Write命令有效时锁存列地址。对于已被激活的同一个Bank,再次激活必须重新执行一次Precharge all bank命令。

1.3 刷新

DDR SDRAM的存储单元由晶体管和电容器组成,电容器会由于漏电而导致电荷丢失,为保证数据存储的稳定性,必须周期性地对DDR SDRAM进行刷新。控制器内部的自动刷新计数器每隔一个刷新周期便会发送一个刷新请求,控制器在接收到请求后会根据当前DDR SDRAM的状态做出不同响应:如果此时DDR SDRAM处于Idle State,控制器便会发出一个Auto Refresh命令对DDR SDRAM进行刷新;如果此时DDR SDRAM正在进行Read/Write操作,控制器会等到当前操作完成之后再发送Auto Refresh命令。

1.4 操作控制

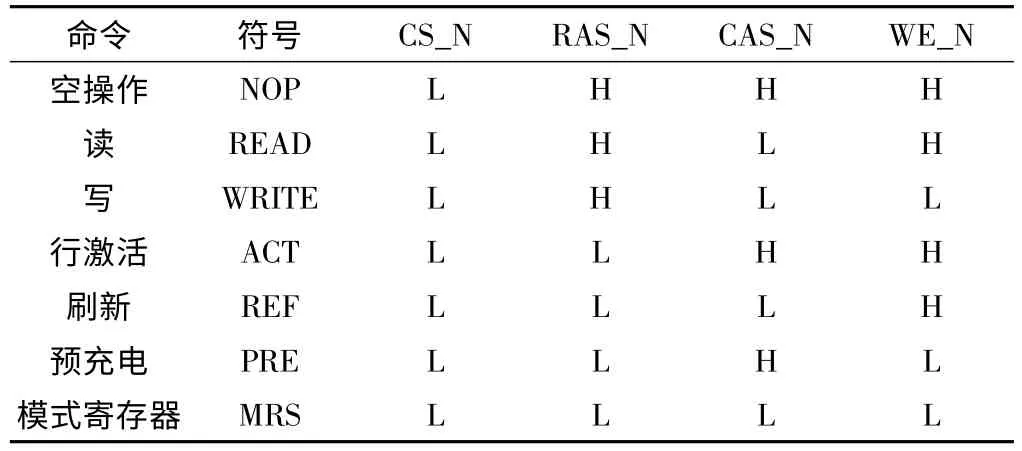

DDR SDRAM的操作命令由专用的命令控制信号决定。具体会执行何种操作动作决定于系统时钟上升沿时的CS_N(片选信号),RAS_N(行地址使能信号),CAS_N(列地址使能信号)以及WE_N(写使能信号)的状态。DDR SDRAM操作命令真值表如表1所示,选择控制信号线和地址信号线只作为辅助参数输入[2]。

表1 DDR SDRAM的操作命令真值表

2 DDR SDRAM控制器的设计

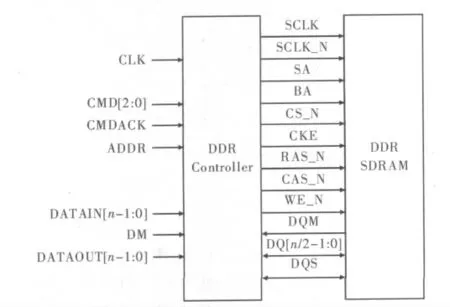

为能像操作普通存储器一样对DDR SDRAM进行控制,必须要通过一系列的初始化操作完成对DDR SDRAM复杂的读写时序转换。同时DDR SDRAM控制器还要自行产生周期性的Auto Refresh命令自动刷新DDR SDRAM,以保证存储数据的稳定性[3]。图1为DDR SDRAM控制器管脚接口示意图,控制器右端的管脚接口与DDR SDRAM所对应管脚接口直接相连,控制器左端的管脚接口则是接收来自系统发送的控制信号。

图1 DDR SDRAM管脚接口示意图

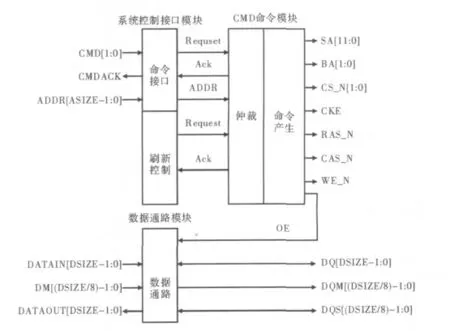

DDR SDRAM控制器的基本构造框架如图2所示:分别是系统控制接口模块ddr_control_interface、CMD命令模块ddr_command和数据通路模块ddr_data_path。ddr_control_interface包括命令接口模块和刷新控制模块,系统发出的控制信号会首先进入ddr_control_interface,进而产生不同的command信号组合;ddr_command用于接收系统控制接口模块产生的command,并解码成具体的操作命令对DDR SDRAM进行控制;ddr_data_path主要是对输入和输出数据进行有效的控制。

图2 DDR SDRAM控制器的基本构造框架

2.1 系统控制接口模块

图3为系统控制接口模块ddr_control_interface的有限状态机。控制器接收到后模块发送的LOAD_REG1命令后进入载入模式,然后由一个LOAD_REG2命令将刷新计数器值载入控制器。控制器发送Read/Write操作请求时,如果DDR SDRAM正处于Idle State,则需要使用Active命令打开相应的行之后才能进入Read/Write状态。DDR SDRAM的Read/Write访问是基于突发方式,有2、4、8这3种突发长度。在突发长度为8的状态下,DDR SDRAM接收Read命令后会在指定的延迟后的4个时钟周期内,由DQ数据线给出8个16位数据,完成1次突发Read操作。执行完1次突发Read操作,控制器便会自动转入Read等待状态,这个等待状态将持续到控制器接收到下一个Read命令。如果此时发送1个Precharge命令关闭当前正在工作的行,控制器就会进入Idle State。连续突发Read操作可以通过设置Read等待状态来实现而不必重复Active操作。当Read操作发生在不同的行时,需要先使用Precharge命令关闭正在工作的行,再由Active打开需要读取的另一个行,而此时的访问耗时最长[4]。

2.2 CMD命令模块

CMD命令模块ddr_command由仲裁模块以及命令产生模块构成。仲裁模块的作用主要是仲裁初始化请求、刷新请求以及读写请求的优先级,并产生初始化响应initial hold、刷新响应refresh hold和读写响应sdram wr hold。命令产生模块则是实现存储器与控制之间的命令通信,直接产生存储器所需的CKE、CS_N,RAS_N,CAS_N,WE_N等命令信号。除此之外Read/Write所需的行列地址和簇地址也由命令模块产生。命令产生模块接收到来自CMD命令解析模块的操作命令后,根据数据选通信号OE对数据通路模块进行有效控制:OE为1时,进行Write操作;OE为0时,进行Read操作。

2.3 数据通路模块

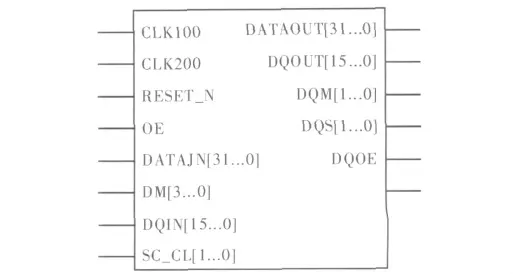

数据通路模块ddr_data_path受命令产生模块的OE信号控制,其管脚接口如图4所示。OE为1时,数据可由DQIN引脚写入DDR SDRAM;OE为0时,数据可从DDR SDRAM的DQIN引脚读出。

图4 数据通路模块管脚接口示意图

由于DDR SDRAM在时钟的上升沿和下降沿能均触发数据,使得用户端的数据宽度是DDR SDRAM的两倍。进行Read操作时,DQ pins上的双倍速率数据经过边沿触发器,在DQS信号的两个边沿同时采样数据,然后这些数据会通过另一套可配置的寄存器被传送到系统的时钟域。进行Write操作时,用户端寄存器输出的数据会被传送到控制器的寄存器中,进而被存放到DQ pins上。数据通路模块在与存储器的接口处完成了两个转换:一是翻倍来自存储器的数据总线宽度;二是以400 MHz的时钟频率接收存储器在时钟上升和下降沿发出的数据[5]。

3 DDR SDRAM控制的仿真和验证

3.1 DDR SDRAM控制器的软件仿真

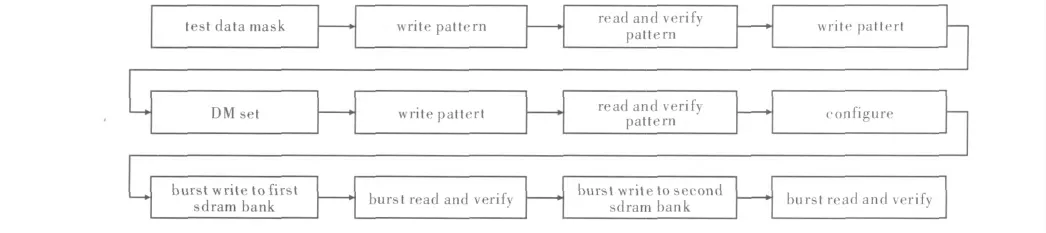

设计的软件功能仿真是利用硬件描述语言Verilog HDL写出测试代码,在Mentor公司的Modelsim软件中进行,通过检查波形完成。DDR SDRAM控制器测试流如图5所示,实现了写数据到第1组寄存器,读校验数据,写数据到第2组寄存器,读校验数据。

图5 DDR SDRAM控制器测试流

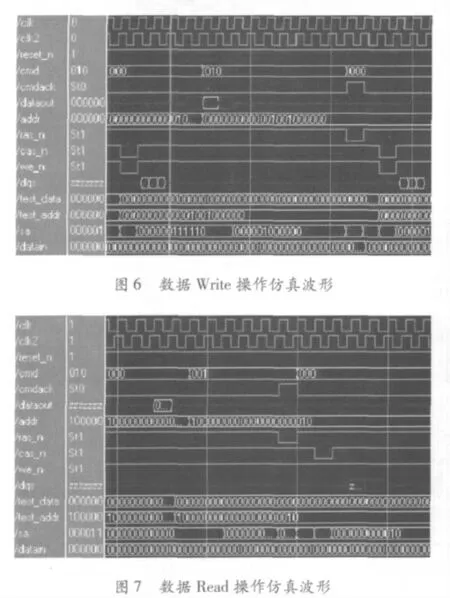

当控制器接收到请求发送数据的命令后,由命令引脚产生相应的Write命令传送给DDR SDRAM,接下来会反馈一个握手信号ready以告知用户端已准备就绪可以继续接收数据,而接收到的数据通过dq端口直接传给DDR SDRAM。经过Modelsim功能仿真Read/Write波形如图6和图7所示,结果表明DDR SDRAM能顺利地完成读写、刷新和预充电,行与行、块与块之间的交换平稳迅速,无论是连续还是单个操作都非常顺畅[6-7]。

3.2 DDR SDRAM控制器的FPGA验证

设计的DDR SDRAM控制器硬件验证在Altera公司CycloneII系列的EP2C5Q208C8 FPGA芯片中进行,利用在线仿真技术快速建立芯片设计的硬件模型,然后将设计映射至目标FPGA电路中,通过加载设定的激励信号,观察所输出的结果并与所期望的输出结果进行比较,发现写入和输出的数据完全吻合。经过综合,基础逻辑单元资源占用率为12.33%,引脚资源占用率为62.5%,锁相环PLL资源的占有率为50%,流片频率测试也能达到期望要求,能完全胜任对DDR SDRAM控制。

4 结束语

在研究DDR SDRAM的主要工作特性以及时序的基础上,利用Verilog HDL硬件描述语言提出了一种适用于DDR SDRAM的控制器的设计。并且通过了Modelsim软件功能仿真、FPGA硬件验证,结果表明该设计传输数据稳定可靠,读写效率较高,接口电路简单,可应用于各种高速度、大容量存储器场合中。

[1] 何云斌,张玉芬.多端口SDRAM控制器的设计与实现[J].微计算机信息,2009(14):49-50.

[2]KILTS S.高级FPGA设计结构、实现和优化[M].北京:机械工业出版社,2009.

[3] 王金明.数字系统设计与Verilog HDL[M].北京:电子工业出版社,2002.

[4]KWANG I O,LEE S K,KWANG I P,et al.Cancelation of a crosstalk induced noise in a DDR memory interface[C].SoC Design Conference,2008,3:III-62-III-63.

[5] 赵刚.数字电路与系统课程精粹与题解[M].成都:四川大学出版社,2008.

[6]邓可学.队列管理和SDRAM控制器的FPGA设计[R].南京:中国电子学会,2007.

[7] 郭连平,田书林.高速数据采集系统中触发点同步技术研究[J].电子测量与仪器学报,2009(3):224-229.