基于PCI总线的HOTLink通讯卡设计

2013-04-23咸阳市公安消防支队

咸阳市公安消防支队 姚 嫚

Hotlink技术是CYPRESS公司提供的一种高速背板串行数据传输技术,传输码率为150Mbit/S—400Mbit/S,符合DVB-ASI、ATM、SMPTE-259M以及ESCON等标准,其产品可用于构建上述标准的通讯产品物理层,支持同轴电缆、双绞线以及光纤接口,传输距离与传输介质有关,例如Hotlink系列中应用比较广泛的CY7B923/933收发器,在不加任何补偿电路、330Mbit/S传输速率的情况下,使用50欧姆同轴电缆最大传输距离为35m,使用75欧姆同轴电缆最大传输距离可达150m,若使用光纤传输则可以达到数十千米以上或更远距离[1]。由于具有速度高、支持多种传输介质的优点,目前CYPRESS公司的Hotlink系列产品在高速图像传输[2]、光纤通信[1]、拖曳阵声纳数字传输[3,4]等领域得到广泛应用。前述的HOTLink产品方案多为专用方案,使用HOTLink技术传输的数据无法直接用计算机进行处理及收发,而对传输数据的格式转换等处理均采用专用硬件完成,不仅成本高而且灵活性较差。本文使用应用比较广泛的HOTLink收发器CY7B923/933以及PCI桥芯片PCI9054设计了一种基于PCI总线的Hotlink通讯卡,支持光纤和铜缆两种接口,通过PCI总线计算机可以直接对传输数据进行处理及收发,利用通用计算机灵活的优势取代专用硬件完成传输数据的协议转换、格式转换、记录等操作,并且还可为HOTLink产品的前期研发提供测试及验证服务。

1.HOTLink通讯卡结构及硬件设计

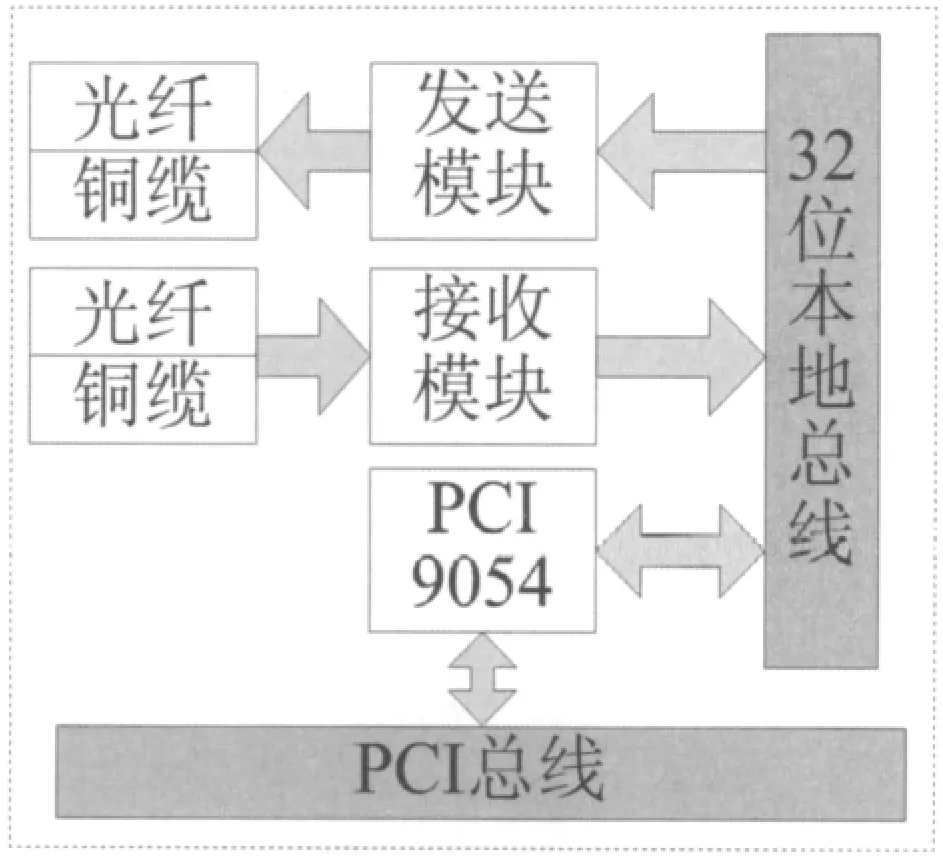

CY7B923/933收发器是HOTLink系列产品中应用比较广泛的产品,本文所设计的HOTLink通讯卡分别使用了CY7B923和CY7B933作为HOTLink的发送芯片和接收芯片,通过板上跳线可选择铜缆和光纤两种接口。通讯卡的总体结构如图1所示,分为发送模块、接收模块以及PCI9054三个部分。

考虑到CY7B923/933收发器所能支持的最大传输速度为40MByte/s,而PCI9054所支持的最高时钟频率为33MHz,如果采用9位单FIFO的结构,PCI总线的一个时钟周期仅能传送一个字节的数据/协议信息,理论上的最高传输速率仅为33MByte/s,将会造成数据溢出,考虑到不同场合的应用需求,发送模块和接收模块均采用了双9位FIFO并联的模式,即一个时钟周期可以传输两个字节的数据/协议信息,位15-位0为双字节数据,位17和位16分别表示高字节和低字节的内容类型,为1表示内容为协议信息,为0低表示内容为数据。相应的PCI9054的本地总线模式采用了32bit位宽模式。在CY7B923的数据手册中指出外部时钟源决定了数据传输的速度,并且在CY7B933的数据手册中还特别要求外部时钟源频率误差不得超过±0.1%。为了配合不同速率的数据收发应用,使用了直接数字频率合成芯片AD9850来实现16MHz-40MHz的可变时钟输出,其精度为±1/232。

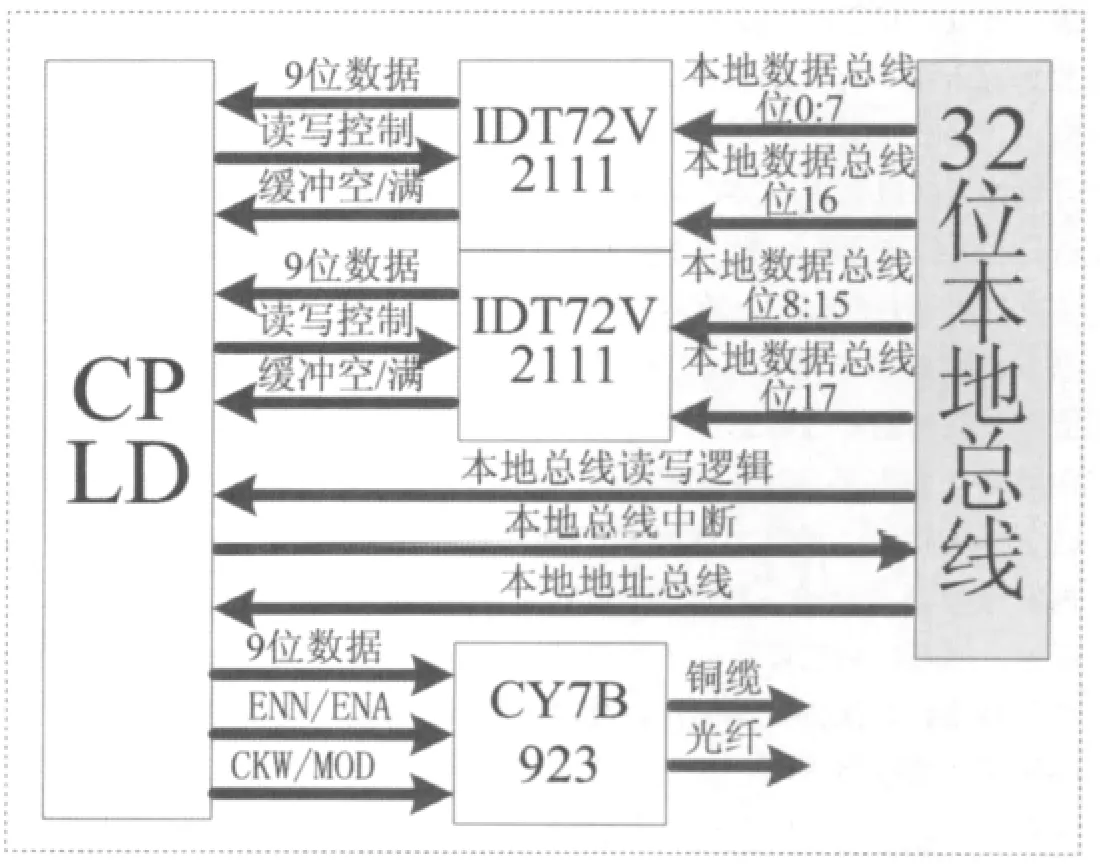

1.1 数据发送模块

图1 总体结构

图2 数据发送模块

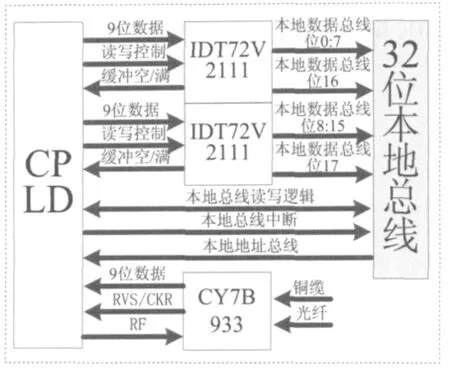

图3 数据接收模块

图4 数据发送模块

发送模块的硬件框图如图2所示。FIFO由两片IDT72V2111并联组成,总容量为524288*18bit,其数据输入端挂接到本地数据总线上,本地地址总线和读写控制信号接入CPLD,即CPLD在FIFO未满情况下允许PCI总线透过本地数据总线对FIFO写入数据。FIFO的数据输出端以及CY7B923数据输入、ENN、ENA、CKW等发送控制信号也接入CPLD,即CPLD在FIFO非空的情况下读取FIFO内的数据,并产生符合CY7B923发送控制逻辑的时序信号,将FIFO内的数据发送出去,直至FIFO变为空状态。由于FIFO为两片并联,因此发送时需要顺序读取FIFO内的数据,时序控制由CPLD完成。

1.2 数据接收模块

接收模块的硬件框图见图3。同接收模块一样,FIFO由两片IDT72V2111并联组成,数据输出端挂接到本地数据总线上,本地地址总线和读写控制信号接入CPLD,即CPLD在FIFO非空的情况下允许PCI总线透过本地数据总线对FIFO内数据进行读取,直至FIFO变为空状态。FIFO的数据输入端、写控制以及CY7B933的数据输出、RVS、RDY、SC/D、RF等接收控制信号均接入CPLD,即FIFO在未满状态下允许CY7B933在CPLD的控制下将接收到的数据依次写入两片FIFO中,直至FIFO变为满状态。在编码工作模式时,为了使CY7B933能够在高速的串行数据流中正确的恢复出传数据,需要外部控制器根据RVS(接收数据错误指示)的状态来控制CY7B933所内置成帧器的启动,根据CY7B933的数据手册,当接收到的连续64个数据中出现16次数据错误即认为数据失步,此时外部控制器应该将RF置为高,使能内部成帧器,数据同步后,CY7B923的RDY将会变低,表示同步完成,进入数据接收状态。上述逻辑也由CPLD完成。

1.3 PCI9054

PCI9054是PLX公司生产的PCI桥芯片,符合PCI总线规范2.2版,本地总线针对不同的处理器具有M、C、J三种模式,根据发送模块及接收模块的硬件接口及速度的要求,选择了C模式,即地址总线和数据总线独立,硬件结构见图4。在通讯卡收发数据时,PCI9054[5]作为本地总线的主处理器,对接收模块和发送模块的FIFO分别进行读操作和写操作,读操作和写操作的逻辑握手信号分别有数据接收模块和发送模块的CPLD完成。本地总线控制仲裁用于本地总线控制权的裁定,由于通讯卡只有一个本地主机—PCI9054,因此该仲裁器使用了一片D触发器,即PCI9054发出请求信号后,在下一个本地时钟周期,仲裁器立即允许9054取得本地总线控制权。EEPROM用于系统启动时PCI9054内部寄存器的初始化,即当计算机系统启动时,9054自动加载EEPROM内容,初始化9054并向操作系统申请地址空间以及中断资源。根据PCI9054数据手册对EEPROM的要求及兼容列表,选择了ATMEL公司的AT93C66A,其容量为4Kbit。

2.结论

本文给出了一种基于PCI总线的HOTLink通讯卡的设计方案,根据方案所开发的HOTLink通讯卡采用了与PCI总线兼容的PC104-PLUS总线,与一块通用的PC104主板构成了一个数据记录仪,成功应用于某型号装备的数据记录系统中,采用低成本的铜缆以200Mbps的速率进行传输,可靠距离可达20米,若使用光缆接口,距离可达1km。借助于灵活的通用计算机技术,本文所设计的HOTLink通讯卡除了作为数据采集外,还可以用作协议转换(例如HOTLink与以太网互转)、HOTLink节点控制,HOTLink产品开发及验证。

[1]高进,谢艳,覃宗厚.基于FPGA的CY7B923/933复用/解复用器在光纤通信中的应用[J].光通信技术,2007,31(3):40-41.

[2]向冰.高速图像串行总线传输[J].现代电子技术,2006,29(24):97-100.

[3]冯师军,李启虎,孙长瑜.拖线阵声纳数字式水下数据高速传输的设计[J].声学技术,2007,26(3):362-366.

[4]包玉华,郑剑锋,冯师军,蒋飚,孙长瑜.HOTLinkTM高速串口至以太网的声纳数据传输模块设计[J].声学技术,2003,2:369-370.

[5]朱惠静.PCI9054及其在高速数据采集系统中的应用[J].国外电子测量技术,2008,27(2):72-74.