数字频率计电路设计与分析

2013-04-23苏州大学王伟明

苏州大学 王伟明

一、问题的提出

在电子信息领域,仅仅电压、电流和电阻的测量已远远不能满足其飞速发展的要求,所谓一块万用表在手可走偏天下的时代也已一去不复返。目前信号频率、电磁辐射、有害气体等等的测量要求非常广泛。价格低廉、简单实用的检测设备是普通电子爱好者需求的目标之一。

本文利用价格低廉的集成电路CD4541、4528、4093、4026设计制作一款数字频率计,并对具体电路进行分析。

二、电路功能

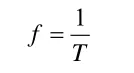

频率是指在1S时间内周期信号变化的次数,单位为Hz,用f来表示,周期用T来表示,他们的关系为:

当信号每秒变化N次,用上式表示的关系为:

由此可见,数字频率计在1s标准时间内,测出信号变化的次数,然后再用数字形式显示出来,即完成其功能的主要部分。具体来说,数字频率计必须具备以下三个功能部件:

图1 数字频率计电路功能框图

图2 数字频率计电路原理图

1.能产生1s标准时间的功能部件。

2.计数部件。

3.显示部件。

电路功能框图如图1所示。

三、电路原理

1.电路原理图

电路原理如图2所示,被测信号经“IN”输入,经整形后送到计数控制器输入端,当控制定时器跳变为高电平(TH:1s)时其波形前沿触发置零电路,使计数器瞬时置零,同时闸门打开,信号通过,允许计数,并通过LED显示计数值。当控制计时器为低电平时,闸门关闭,计数技术停止,所计数值保持不变并被稳定显示。

2.单元电路工作原理分析

1)整形电路和内置振荡

整形电路和内置振荡器单元由集成电路4093中的IC3:A和B组成,集成电路4093内部结构是4个双输入与非门电路组成。

整形:当SA置于“外接”时,IC3:A和B的输入端分别短接,电路成为反相“非门”,两个反相“非门”串联,则总相位不变。由于门电路输入输出特性,其输出只有“0”和“1”两种状态,整形效果较好。但要注意信号幅度必须足够大,一般应大于4/5电源电压,否则有可能无法计数显示。

内置振荡:当SA置于“校准”时,IC3:B、RP2、RP3、C3构成内置振荡器,调节RP2(粗调)与RP3(细调)设定为5000HZ,5V,可作为“校准信号”,其原理与门控振荡器相仿,这里不再重复。

2)闸门

闸门电路单元主要由集成电路4093中的IC3:C和D组成该电路利用了与非门任一输入端输入为“0”,其他输入端不再对输出状态起作用的特点,将IC3:C的一个输入端(4093⑨脚),另一输入端作为信号输入,是与非门变成一个受控的闸门。

受控输入端接控制定时器输出端,当控制定时器输出“0”时,闸门关闭,无输出。当控制定时器输出“1”,闸门打开,波形输出与输入相位一致,能够传递到计数器。

3)控制定时器

控制定时器单元是由集成电路4541和R1、RP1、C1组成。该电路输出一周期为2s(TH和TL各为1s)的方波波形,电路主要由R1、RP1、C1选频电路决定4541的内振荡频率,再经29分频得到上述波形,当输出Q端为“1”时闸门打开,开始计数,OUT端有波形输出,LED显示数字快速变化,Q端为“0”时,闸门关闭,计数停止,LED显示数字不再变化,保持,OUT端无输出波形。

4)置零电路

置零电路单元主要由集成电路IC2(4528)和R2、C2等组成。该电路是利用脉冲的上升沿进行触发的单稳态电路,R、C大小决定置零脉冲的宽度,置零脉冲的宽度应远小于被测信号的周期,IC2④脚是输入端,接4541输出端,当接收到“1”信号上升沿时,产生一个正窄脉冲信号,计数器置零。窄脉冲过后,计数器恢复计数状态。

5)显示电路

显示电路单元由4片4026集成电路和4只共阴极LED数码管组成。4026集成电路是十进制译码、直接驱动LED电路,4为十字分别表示千位、百位、十位、个位。①脚为输入端,上升沿有效,⑤脚为进位信号输出端,在本电路中又为高一位计数器提供计数脉冲。图2是数字频率计电路原理图。

四、结论

本电路设计结构简单,功能比较齐全,作为电子爱好者自行设计信号源时的频率显示辅助电路具有一定的实用性,在调试过程中,须将标准信号源接入,SA在“外接”位,信号源频率调节为5000HZ,然后调节定时器电路阻容网络(调节RP1),使Q端输出为T=2S,即为正电平1S,使闸门打开时间为1S,操作时为调节RP1使数码管显示5000。SA放到“校准”位时,调节RP2到中间位,再调节RP3使数码管显示5000即完成。

[1]杨帆.数字频率计的设计与实现[J].科技广场,2011(9).

[2]武卫华.基于SoPC的嵌入式数字频率计设计与实现[J].电子测量与仪器学报,2010(2).

[3]沈亚钧.基于单片机的数字频率计设计[J].山西电子技术,2012(10).

[4]徐秀妮.基于VHDL语言的全同步数字频率计的设计与研究[C].长安大学,2011-05-25.