协作多点传输中板间串行高速通信的FPGA设计

2013-03-11李铁峰李红波

李铁峰,李 鸥,李红波

(解放军信息工程大学 信息系统工程学院,河南 郑州450002)

协作多点传输技术(CoMP)被认为是LTE-Advanced最有前途的技术之一。它用来提高数据速率,增加小区吞吐量,减少小区干扰等[1]。一个基站通过光纤连接多个天线站点,所有的基带处理仍然集中在基站,形成集中的基带处理单元[2]。基站负责维护与用户的物理层链路,进行大量的信号处理与数据交换。基站中所有的射频和数字基带板都是交互连接的,并且通过高速背板链路与多种控制、接口板相连,数据必须从电路板发出,通过背板传输至交换卡,而交换卡可将数据发送至机架内的其他位置。在这些板上,芯片到芯片的数据率非常高。在IMT-Advanced协作多点传输中,由于还要传输协作节点间的相关信息,基站间、扇区间互相传输的数据率更是达到了数Gb/s。图1是IMT-Advanced协作多点传输中的一个典型数据交换结构,大量的基站与移动台间信道信息需要交换,可见其对高速通信的需求非常高[3]。

图1 CoMP中的数据交换示意图

传统的系统中,处理器、处理器簇、FPGA之间的高速数据通信基于并行的共享总线方式进行,所有的设备通信竞争带宽,使得交互数据成为了整体系统性能的瓶颈。并行总线所需要的大量IO引脚和馈线要求系统的电器性能和机械性能足够健壮,电路板的设计也变得越来越复杂。目前新型的体系结构是基于点对点串行交换结构的体系。相比传统的并行共享总线结构,串行交换结构中的两个端点交互数据不影响其他端点之间的数据交互,可大大提高系统带宽。串行交换结构所需要的引脚也大幅减少,而且串行结构采用的差分线连接也提高了信号传输的距离和可靠性。SRIO(Serial RapidIO)是当前流行的主要串行交换结构之一。相比PCI、PCI-X、PCIE和Infiniband来说,RapidIO主要特性是具有极低的延迟性和高带宽,并很容易实现与PCI、PCI-X、PCIE、FPDP、以太网等的桥接,适合用于芯片与芯片、板与板、系统与系统之间的高速数据传输[4]。

本文主要讨论CoMP的实验床中的背板间SRIO通信的FPGA设计,分析了任务需求和数据传输特点,并给出了关键的SRIO设计和测试结果分析。

1 应用需求分析

在CoMP实验床中,存在着大量的数据交换,如图2所示,上行基带处理通常需要在FPGA和DSP中进行FFT、信道估计、解调、解重复、解交织、解扰、译码以及数据校验等处理。这些处理可以根据其在FPGA和DSP中实现的难易程度以及资源消耗率对实现器件进行选择。经过校验后,上行数据再通过SRIO Switch发往CPU进行MAC层的处理,处理完成的数据最后通过CPU的GE接口进入核心网。

图2 CoMP实验床中的SRIO数据交换

对于下行处理而言,下行数据通过GE接口进入CPU,CPU再将数据发往相应的处理器件进行处理。当处理器件完成对下行数据的编码、加扰、交织、IFFT等处理后,再通过SRIO发送到射频板。FPGA模块完成底层的数据交换与处理,除了本板上与DSP模块之间的数据交换外,多点协作传输所必需的基站间数据传输也通过FPGA经背板串行交换实现。DSP模块实现协作算法及其他上层应用。FPGA、DSP、Switch之间通过SRIO接口高速交换数据。由于DSP和Switch芯片本身就支持SRIO传输,所以SRIO的设计工作主要集中在FPGA模块上。

根据上述的CoMP数据传输需求,FPGA通过背板进行SRIO传输的数据速率要达到6 Gb/s以上。

FPGA设计在Xilinx ISE Design Suite开发环境中完成,以Xilinx提供的SRIO core为基础,对其进行裁剪与修改。原core代码仅可用ModelSim仿真,但不可综合,不能下载到电路板进行实际电路运行,且功能繁杂,不适合CoMP系统实际应用。因此,需设计满足CoMP系统实际应用的用户接口,并通过自编的主机程序模拟上层应用数据的产生,用于板级测试,验证是否可达到用户接口所需的功能。

主机程序对于数据传输的时序要求主要有:

(1)数据帧时钟为156.25 MHz,且与SRIO内部的sys_clk同步。

(2)数据帧长度为256 B的整数倍,最长1 024×64 bit,最小32×64 bit。若实际数据长度不是256 B整数倍,由数据产生模块填空至整数倍,帧的起始/结束定界由上层逻辑负责。

(3)以SWrite事务模式发送,每个SRIO包有效数据载荷固定为256 B。虽然SRIO协议有多种IO逻辑操作事务模式,但SWrite模式由于减少了头部开销,对数据对齐和数据载荷大小做了一些简化设置,其传输效率可高达95%,更适合于CoMP中的高速数据传输。

2 SRIO内部模块及用户接口设计

SRIO内部由时钟模块(srio_clk)、复位模块(rio_reset)、物理层与IO逻辑模块(rio_wrapper)、用户接口模块(user_top)和主机模块(host)组成,如图3所示。除用户接口模块和主机模块外,其余模块都可直接利用SRIO core源代码。结合CoMP的实际应用,用户接口模块包含发送子模块(initiator_user)、接收子模块(target_user)和FIFO模块(fifo_srio)。其中initiator_user用于完成数据的流写事务(Swrite),是SRIO FPGA设计中的核心部分。它根据主机模块提供的控制信号读取FIFO中的待发数据,按照Swrite包格式封装数据,与物理层及IO逻辑模块协同完成数据发送任务。

图3 Srio内部功能模块

根据SRIO协议,initiator_use模块工作机制设计如下∶当ireq_rdy_n=′0′,FIFO内数据超过x1F且不处于config状态时,开始一个新的ireq发送周期,在每个周期内计数器i从初值0递增到datalength+14,共需datalength+17个时钟周期。initiator_use模块接口如图4所示。

图4 initiator_user模块接口示意图

考虑到读FIFO时延及ireq_rdy_n信号时序特点,经大量ModelSim仿真得出只有满足如下设计规则,才可保证每个ireq发送周期都能正常连续无误工作:

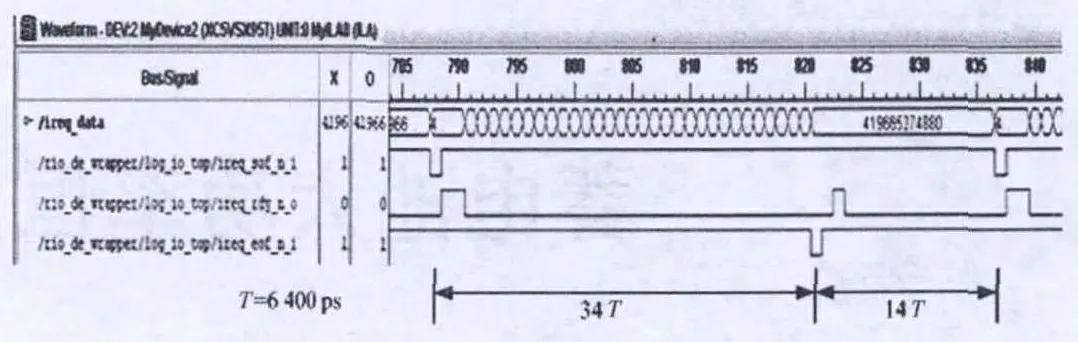

(1)仅当i=1或3 (2)仅当i=2时,ireq_sf_n置0; (3)仅当i=datalength+2时,ireq_eof_n置0,并更新ireq_tid值; (4)当i值在2~datalength+3之间时,ireq_vld_n置0。 ireq发送周期仿真时序如图5所示。 图5 ireq发送周期仿真时序图 在Host模块中设计了一个双口FIFO,用于缓存待发送数据,并与SRIO发送速率相匹配。当FIFO里至少有32×64 bit数据(即fifo_data_count≥x1F)时,才可开始一个ireq发送周期,即有足够的数据需要传输,这样可以确保Swrite模式的数据大小要求。不检测是否需重传,因底层的纠错机制已可保证正确性。 当fifo_data_count=x2FF时,表明当前initiator_use模块不能及时将待传输数据发送出去,为了不发生丢包事件,需向Host模块指示忙状态,以使FIFO暂停数据写入。此时tx_rdy_n置1,直至fifo_data_count回落到x1FF时,tx_rdy_n置0,允许继续向FIFO写入数据。 接收子模块target_user的接口设计如图6所示。 图6 target_user模块接口示意图 最终完成的程序代码经综合、编译后分别下载到两块实际电路板,进行双向数据同步透传测试,测试时间持续4 h,FPGA型号为XC5VSX95T,通过ChipsCope工具软件监测数据传输情况。测试结果表明,电路工作稳定,数据传输准确无误,传输速率达到了预期目标,如图7和图8所示。 图7 全双工工作 图8 传输速率达6.67 Gb/s 在48个时钟周期内,传送了32×64 bit净数据,即传输速率为: 在电路板设计及测试过程中,还需要注意Rx/Tx buffer芯片的工作状态与SRIO的初始化过程之间的配合问题。现有的buffer芯片只有当4对Tx差分线上都有信号,即它们符合“线与”关系时,芯片才能转入工作状态,否则它一直处于休眠状态。而通过SRIO的ModelSim仿真可以观察到,在SRIO运行的初始化阶段,4对Tx输出并不是同步完成初始化,直接影响了buffer芯片的正常工作。因此,在Rx/Tx buffer芯片的外围电路设计中需作相应的适应性修改。 本文介绍了串行高速通信接口(SRIO)在IMT-Advanced协作多点传输测试床中的应用,详细分析了SRIO的FPGA设计关键点。仿真与实测结果表明,本文所设计的SRIO接口可实现全双工可靠通信,数据速率达到6.67 Gb/s。 [1]3GPP TR36.913.Requirements for further advancements for E-UTRA(LTE-Advanced)[S].2009. [2]何玉申,宫芳.下一代无线移动通信LTE及LTE-Advanced的研究[J].信息技术,2010(11)∶132. [3]王存祥,邱玲.协作多点传输中一种基于特征子信道的干扰对齐预编码矩阵优化方案[J].信号处理,2011,27(3)∶395-399. [4]FULLER S.RapidIO∶The embedded system interconnect[M].John Wiley & Sons,Inc.,2005.

3 板级测试结果分析