基于噪声抵消和线性度提高的差分LNA的设计

2013-02-05何国荣

纪 娜,何国荣

0 引言

低噪声放大器(LNA)是射频接收机前端的主要部件。由于其位于接收机前端,所以它需要有较低的噪声系数,并具有足够的增益来抑制后面各级噪声对系统的影响,同时要求有一定的线性度来保证不失真的接收射频信号,另外为了达到功率最大传输或最小的噪声系数,LNA的输入阻抗应该与前端源阻抗匹配。

由于电感负反馈的共源LNA优越的噪声特性,得到了广泛的应用[1-3]。共栅LNA能够很容易地实现输入阻抗的匹配,但是却具有较差的噪声性能[4],交叉耦合电容技术能够降低共栅LNA结构中的栅极对输出端口的噪声贡献,从而优化噪声特性[5],然而在共源共栅 LNA中,共栅晶体管源端的寄生电容会对整个LNA的噪声特性造成影响。本文中,引入一对电感与交叉耦合电容相连,消除了共栅极噪声,一定程度上提高了LNA的线性度和增益。

1 噪声抵消

本文设计了一种差分形式的LNA,电路图如图1所示:

图1 提出的LNA电路结构

Lg,Ls主要完成输入端口的匹配,输出端增加一个电阻Rd以提高电路的稳定度,Rd,Ld,Cout1和Cout2完成输出端口的匹配,Cb,Cout1用于隔离直流信号,Vdd是电源接点,Vb1、Vb2分别为 M1、M2提供偏置电压。为了抵消共栅晶体管产生的噪声,并提高LNA的线性度,在图1的X点处引入一对交叉耦合的电容Cc,其电容值远远大于M2栅源极之间的寄生电容 Cgs2,并在 M2的栅极加入一对电感 Ladd,此改进技术如图1中虚线所示[6]。

在工作频率ω0下,图1中X点处的等效输入电导为公式(1):

其中gm2为M2的跨导。

在ωCc远远大于ωCgs2-(1/ωLadd)的情况下,X点处的等效输入电纳为公式(2):

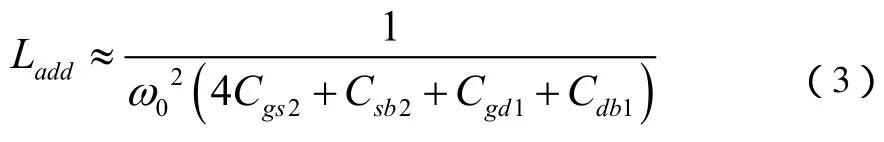

其中Csb2为M2源极对衬底之间的寄生电容,Cgd1为M1栅漏极之间的寄生电容,Cdb1为M1漏极对衬底之间的寄生电容。当等效电纳等于0时,X点处的寄生电容效应就可被消除,如公式(3):

引入此技术后得到的LNA的噪声系数为[6]公式(4):

其中F1为M1的噪声,Fc为M2的噪声,Rs为源阻抗,C2为M5与偏置相关的参数,gd02为M2管零偏时的漏极电导,ωT是截止频率。

由此可见,当满足式(3)时,可使等效电纳等于 0,从而共栅管的噪声Fc可被消除掉[7]。

2 线性度提高

对于共源共栅结构的LNA,线性度主要取决于共源级晶体管,然而当共源级的电压增益较大时,共栅级将对整个LNA的线性度起主要影响。为了在高增益下得到较高的线性度,必须提高共栅级的线性度。引入交叉耦合电容和电感技术的 LNA就可消除共栅级对线性度的影响。改进后的LNA的输出电流为公式(5)

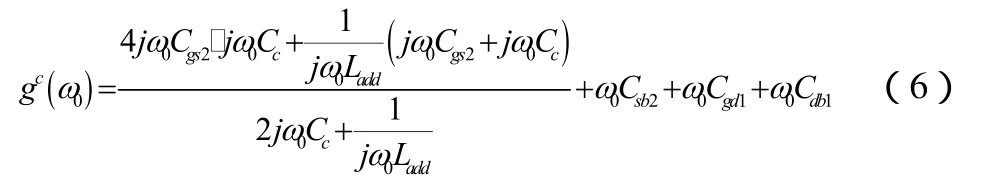

其中i1为共源级的输出电流,Vgs2为 M2的栅源极间电压,且公式(6)

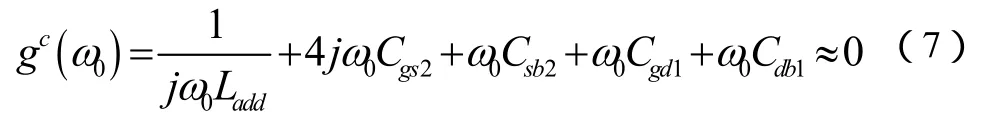

若满足远大于ωCc远远大于ωCgs2-(1/ωLadd)且电感Ladd和X点处的寄生电容在工作频率处共振,如公式(7):

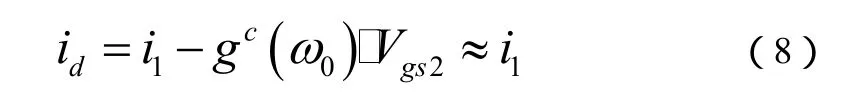

进而得公式(8)

可得出LNA的线性度只取决于共源级,共源级并不影响LNA的线性度。

3 增益提高

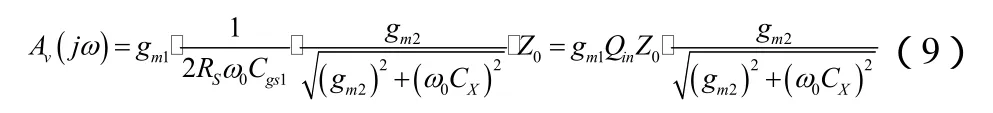

在输入阻抗匹配的情况下,传统的电感负反馈共源共栅结构的LNA的增益为公式(9)

其中公式(10)

式中Qin为LNA输入网络的品质因数;Z0为LNA电路的输出阻抗;CX是图1中X点处的总寄生电容。当采用图1虚线部分所示的技术后,共源结构的LNA的增益变为公式(11)

当BeffX等于0时,LNA的增益为公式(12)

可以看出,与式(9)相比,增益得到了一定程度的提高。

4 LNA仿真结果

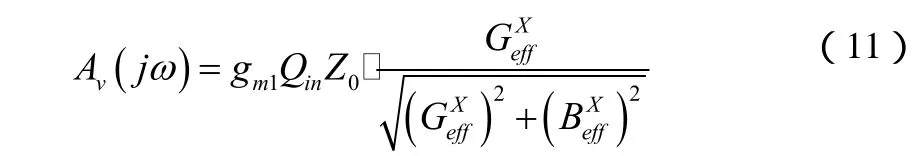

电路设计采用了 TSMC 0.18µm CMOS工艺库,使用ADS2009软件进行电路的仿真和优化。小信号S参数如图2所示:

图2(a)S11,S22随频率的变化关系

图2(b)S21,S12随频率的变化关系

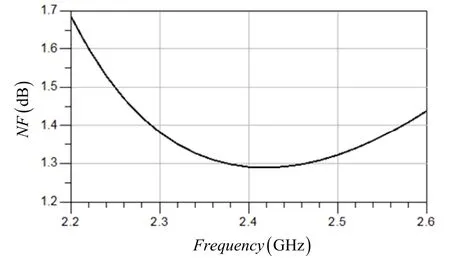

从图中可以看出,在工作的中心频率 2.45GHz处,S21为17.8dB,表现出较高的增益;S11和S22分别小于-30dB和-35dB,表明端口反射较小;S12小于-40dB,表明反向隔离度较高;噪声系数随频率的变化曲线如图3所示:

图3 噪声系数随频率的变化关系

在中心频率点2.45GHz的噪声系数为 1.3dB;使用双音测量法测量输入三阶交调点IIP3,输入射频功率为-40dBm,输出频谱如图4所示:

图4 双音测量法输出频谱

可得IIP3=-40+(-25.9-(-104.1))/2=-0.9dBm,表现出电路较高的线性度,在 1.8V电源电压供电的情况下,功耗为9.36mW,小于10mW。

5 结论

设计了一个中心频率为 2.45GHz的差分低噪声放大器。主要考虑传统的共源共栅结构 LNA的共栅级对 LNA的噪声、增益和线性度的影响。通过在共栅级上引入一对交叉耦合电容和电感,以消除共栅级的噪声并提高放大器的线性度和增益。仿真结果显示,在 2.45GHz时,整个电路能够提供 17.8dB的正向功率增益,噪声系数为 1.3dB,IIP3为-0.9dBm,直流功耗 9.36mW,同时输入输出匹配和反向隔离性能良好。

[1]Madan A,McPartlin M J,Masse C,et al.A 5 GHz 0.95 dB NF Highly Linear Cascode Floating-Body LNA in 180 nm SOI CMOS Technology [J].IEEE Microwave and Components Letters.2012,22 (4):200-202.

[2]Belostotski L,Haslett J W,“Noise figure optimization of inductively degenerated CMOS LNAs with integrated gate inductors [J].IEEE Transactions on Circuits and Systems.2006,53(7): 1409 –1422.

[3]Sakian P,Janssen E,Roermund A H,et al.Analysis and Design of a 60 GHz Wideband Voltage-Voltage Transformer Feedback LNA [J].IEEE Transactions on Microwave Theory and Technology.2012,60(3): 702-713.

[4]Darabi H,Abidi A A.A 4.5 mW 900-MHz CMOS receiver for wireless paging [J].IEEE J.Solid-State Circuits.2000,35(8): 1085–1096.

[5]Ziabakhsh S,Alavi-Rad H,Yagoub M C E.A high-gain low-power 2–14 GHz ultra-wide-band CMOS LNA for wireless receivers [J].Int.J.Electron.Commun.2012,66(9): 727-731.

[6]Fan X,Zhang H,Edgar S S.A Noise Reduction and Linearity Improvement Technique for a Differential Cascode LNA [J].IEEE Journal of Solid-State Circuit.2008,43(3): 588-599.

[7]刘华珠,贺前华.基于噪声相消和线性度提高的低噪声放大器 [J].华中科技大学学报(自然科学版).2009,37(3): 43-45.