基于FPGA的误码仪设计与实现

2013-02-03陈小敏朱秋明虞湘宾孟田珍

陈小敏 朱秋明 虞湘宾 孟田珍

南京航空航天大学电子信息工程学院 江苏南京 210016

在数字通信系统中,通常使用误码分析仪对系统的误码性能进行测量,并以此来判断该系统的性能优劣。因为误码分析仪有丰富的测试接口和测试内容,能将结果直观、准确地显示出来而得到广泛应用,并为工程实际应用带来极大便利。但是由于通用误码仪价格昂贵,并且通常需要另加外部辅助长线驱动电路才能与某些系统接口适配而严重制约了它在实际中的应用。基于工程的需要,并考虑到实际应用中的困难,提出一个基于FPGA的多功能误码测试方案,借助FPGA实验平台、Verilog语言在FPGA芯片上通过编程实现数字基带信号的产生、星座映射、基带成型、信道、匹配滤波、判决、解映射、误码计算等模块,并通过FPGA的数码管显示误码率[1,2]。

1 数字基带系统

无线信道的广泛应用,使得无线衰落信道下数字基带系统的误码性能研究具有更重要的意义[3,4],数字基带系统模型如图1所示。

图1 数字基带系统模型

在图1中,通过星座映射将比特信息映射为符号信息,脉冲成型使信号转换成适于信道传输的信号波形。对于低通基带信道,适合于信道传输的时间响应波形通常为近似矩形波。这里假设图1中的信道为狭义信道,即传输媒介,包括电缆、光纤、无线信道等,并必然存在噪声干扰。其中,脉冲成型、信道和匹配滤波统称为广义信道。通常利用匹配滤波器(均衡器)对广义信道的传递函数进行均衡,使其达到理想低通或者余弦滚降低通特性以及限制带外噪声的作用。抽样判决器是在有噪声的情况下用来判定与再生数字基带信号的,解映射之后恢复比特信息。

2 方案及指标介绍

2.1 硬件平台及总体方案设计介绍

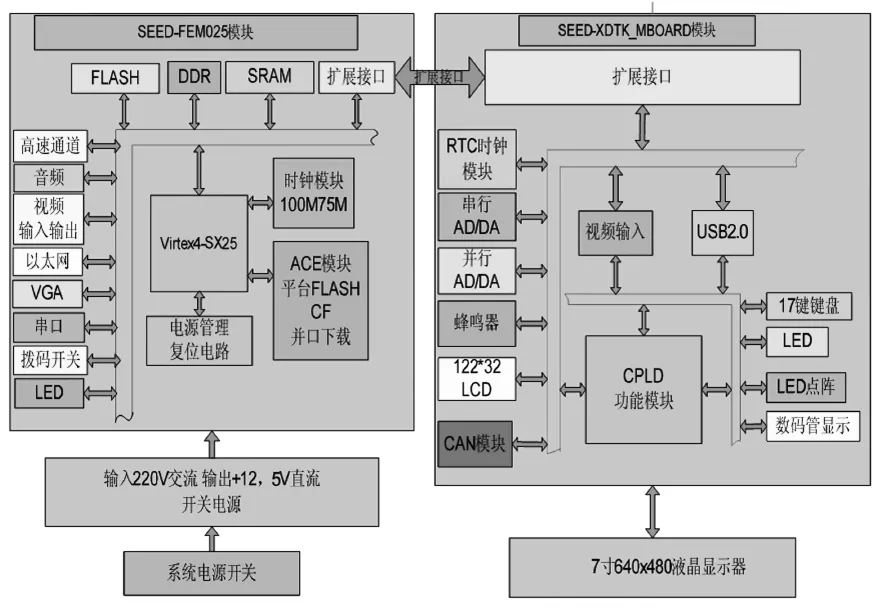

由于FPGA具有硬件的高密度性和高灵活性,在通信信号处理中得到广泛应用。并凭借其专用处理系统的性能,通用计算系统的灵活性、可重构性以及对实现高性能信号处理有很高的应用价值,它可以根据算法来调整相应的数据字长和通信结构。通过一片FPGA及其外围电路来实现误码检测功能, 并通过外部数码管显示误码信息。研究所使用的主芯片为Xilinx公司生产的Virtex4-SX25,系统硬件结构如图2所示。

图2 实验箱原理框图

我们所用实验平台是Xilinx公司提供的集成化开发平台Foundation Series ISE(简称 ISE,是一个集成环境),利用ISE进行设计输入、综合、仿真、实现和下载,可以完成整个 FPGA/CPLD开发过程,界面设计简洁流畅。

集成工具包包括综合、实现、辅助设计、仿真及其他工具等5类。能够完成设计输入、仿真、综合、布局布线、生成BIT文件、配置以及在线调试等。

2.2 系统性能指标

设计的通信系统误码仪具有如下预期指标:

输入输出信号为带巴克码的伪随机序列;

IQ双支路基带传输(QPSK);

数字采样率100 MHz;

高斯白噪声功率范围0~30 dB。

2.3 总体方案设计

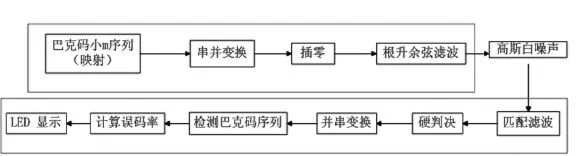

FPGA实现的数字基带系统误码仪流程如图3所示。

图3 数字基带系统误码仪设计框图

基带系统误码仪的实现包含三大模块:发送带巴克码的小m序列经QPSK调制,基带成型后发送;产生高斯噪声的信道;对接收信号进行匹配滤波解调和检测,计算误码率并通过数码管显示。

3 基于FPGA的误码仪设计与实现

3.1 滤波器设计

由图3可见,首先在数字基带处理器接收上层单元传送的数据流,然后对接收的数据流按照QPSK规则进行映射,完成比特流信息到符号的映射。

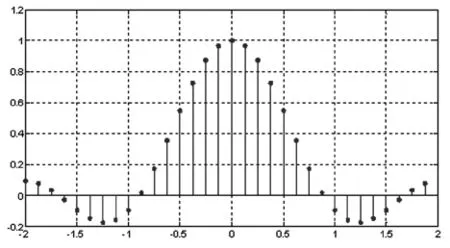

基带成型可以有效减小符号间干扰。理想的成形滤波器即理想的矩形低通滤波器,基于它的陡峭截止特性难以实现,且同步要求很高,不能出现偏差,所以实际系统常采用升余弦滚降滤波器。接收端通常还需要加一个匹配滤波器,其频域响应和发送端的成形滤波器要满足复共轭关系,从而实现对信号的最佳接收。成形滤波器和匹配滤波器共同作用下的等效滤波器为升余弦滤波器。因此脉冲成形滤波器和匹配接收滤波器都采用根升余弦滤波器。滤波器的单位冲击响应如图4所示。

图4 根升余弦滤波器单位冲击响应

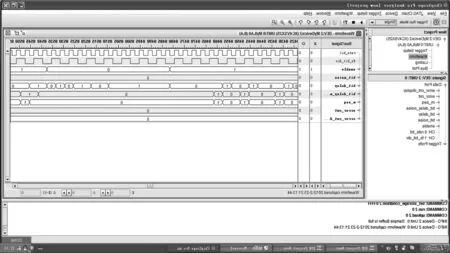

3.2 FPGA设计实现

在数字域中,滤波器以FIR滤波器实现为主。为增加D/A转换后的精确度,可以先通过内插器在相邻两输入序列点之间补7个零[5],从而将输入序列速率提高8倍。采用32阶FIR 滤波器、滚降系数α=0.5,并考虑到内插后原相邻序列点之间有7个连零,FIR滤波器含有原序列的可能非零输出抽头只有4个,所以可用这4个x(n)的组合作为ROM的地址,FIR的输出值是根据x(n)的组合计算好并预存在ROM中的,将这个FIR输出值取出并通过八选一选择器选择相应的地址线。FPGA的设计主要分为3个步骤:首先通过Matlab计算滤波器的系数,然后设计实现滤波器,滤波器的单位冲击响应如图5所示,然后完成FPGA中IP核生成,最后完成IP核的调用。

图5 滤波器FPGA实现

3.3 误码计算和显示模块

巴克(Barker)码是一种二相编码信号,具有良好的非周期自相关特性,在数字通信系统中,因它具有尖锐的自相关函数,很容易与随机序列区别开来,因此常应用于帧同步。巴克码中尤以13位巴克码1111100110101性能最优,其主旁瓣比可以达到2 212 dB,在脉冲压缩等领域得到广泛的应用。

巴克码用于识别数据帧的起始,通过图6的电路(以13位巴克码为例)从串行码流中找到同步点。

图6 13位巴克码同步检测电路

3.4 误码率显示

若同步点出现尖峰,便默认检测到巴克码序列,并产生使能信号enable,将恢复的信号与发送信号的码元逐个进行比较,如果出现误码,两列码序列原来相同的码元就会变得不同。依据这个原理,在位同步时钟的控制下通过异或计算对码元进行逐个比较,比较的结果通过累加电路得到误码数[6],将误码数送到数据显示电路,图7~图8为硬件实现系统照片,图9~图11为硬件实测结果。

在FPGA的编程设计上,通过扫描法逐个连接8位LED,其中的两个控制位,一个一次输出段选码,另一个依次选中一位LED,这样各位上就会显示不同的数字,由于眼睛的视觉惯性作用,当采用一定的频率循环地往8位LED上输送显示代码和扫描代码时,就可以看到稳定的数字显示。

图7 硬件实现图

图8 数码管显示模块

图9 硬件信号产生、串并转换、内插后波形

图10 同步检测和误码数计算时序图

图11 5 dB误码数显示

3.5 硬件实测结果

系统计算5 dB噪声时999帧数据的误码数,误码率为54 634/999×1 024=0.053 4。

4 结束语

设计了高斯信道下数字基带系统的误码分析仪硬件实现方案,并对各个模块进行了详细的设计与实现,最后成功实现了加性高斯噪声信道下数字基带系统误码分析仪的设计与实现。

[1]张水英,金学波,杜晶晶.数字基带传输系统的FPGA设计与实现[J].现代电子技术,2011,34(1):182-188.

[2]方琪.基于FPGA的信道误码测试仪设计与实现[D].北京:北京交通大学,2011.

[3]张水英,金学波,杜晶晶.数字基带传输系统的FPGA设计与实现[J].现代电子技术,2011,34(1):182-188.

[4]J.G.Proakis, Digital Communications[M].Fourth Edition, New York: McGraw-Hill, 2001.

[5]周文辉,程刚,苏凯雄.一种新型的基带成型SRRC滤波器的设计[J].福州大学学报,2009,37(4):514-518.

[6]卢艳萍,陶成.基于FPGA的误码率测试仪[J].电子产品世界,2004(4):79-81.