卫星移动通信终端的低功耗设计

2013-01-14王艳君庄云胜

王艳君,庄云胜

(1.通信网信息传输与分发技术重点实验室,河北石家庄050081;2.中国电子科技集团公司第五十四研究所,河北石家庄050081)

0 引言

低功耗设计是指在产品的设计中,通过采用各种技术手段、降低产品功耗的技术[1]。低功耗的概念是由电子手表等工业首次提出的[2],进而在小型化、高集成度的消费类电子产品中得到了广泛应用。

为了降低电路成本,提高电路稳定性、可靠性,需要进行低功耗设计,以保证在集成度提高时,单位面积可以维持同样甚至更低的功耗;同时,因为在过去的30年中,电池的容量仅仅增加了2~4倍[3],远没有VLSI技术的发展迅速,所以在电池供电的手持设备中,电路的低功耗设计是延长待机时间的最有效手段;此外,在军事应用中,在满足使用要求的前提下采用更小的电池以减小整机的尺寸和重量,即意味着减小作战负荷提高战斗力,因此军用手持设备的低功耗设计显得尤为重要。

1 低功耗设计的研究内容

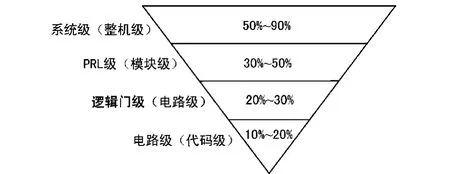

低功耗设计是通信终端设计的一个关键环节,是涉及到整机设计各环节的自上而下的设计技术。在IC设计领域,常采用如图1所示的比例关系来表明在不同层面上采用低功耗设计技术对整体设计结果的影响,图1可以同样应用于设备的低功耗设计中(与括号中的级别相对应),即越是在高层采用相关设计,其设计结果对整机性能改善的程度越大。这是因为层次越高表明在设计中进行低功耗考虑得越早越全面,因此在较高层采用的低功耗设计策略效果越明显。

图1 设计的不同层次对功耗的影响

按照自上而下的设计原则,通信产品的低功耗设计可以分为整机级、模块级、电路级和代码级。

2 整机的低功耗设计

卫星通信终端通常由MCU模块、信号处理模块、射频微波模块和电压转换电路等电路模块组成[4]。整机的功耗可以表示为:

式中,α为活跃因子,表示该模块在整机工作过程中的活跃程度;pn为第n个模块全工作状态下功耗;N为整机可划分开的电路单元,整机集成度越高,则N的值越小。

整机的低功耗设计就是采用合理的技术方案,在满足整机各项功能、性能指标的前提下,通过提高设备集成度(减小N)、降低各模块的活跃状态(减小α)和减小模块的工作功耗(pn)来降低整机的功耗[5]。

为了达到上述设计目的,整机级主要采用了如下的方法:

①以嵌入系统/处理器为核心,基于整机工作状态感知的低功耗设计技术。工作状态感知指的是处理器对操作人员使用状态、用户终端工作状态和系统状态等进行识别,根据用户、终端和系统所处的状态,启用不同的节电策略,通过动态地改变式(1)中的活跃因子,达到降低总功耗的目的。例如:10 s工作人员不进行操作,则进入一级节电方式,如果10 min不操作则进入深度休眠;工作时间不到不进行接收尝试,收不到下行导频,则上行数据不发送等。

②优化整机方案,提高集成度电路。实体模块是整机的直接组成单元,按照传统终端设备的设计方法,功能复杂的手持机可能被划分成十几个电路模块,这显然不能满足小体积低功耗的设计要求,因此本级进行低功耗设计的目的之一就是优化整机方案,对功能相同或类似的实体电路进行合并,提高整机集成度。

③合理选择整机供电方案。选择低电压工作芯片是降低设备功耗的直接手段。因此,芯片(模块)的选取均遵循小体积、低电压和低功耗的选择原则,并且每种芯片都具有待机模式(Standby)或睡眠功能(Sleep),都可以执行独立的断电操作。

选择开关电源芯片替代传统的线性DC/DC。减少直流电源电压种类从而减少电源转换芯片,并且仔细分析每种电压的平均功耗,使电池组输出接近于功耗大的电压。

3 单元电路模块的低功耗设计

现在的通信设备通常以数字电路为主,而当前大部分数字电路均采用CMOS电路,该类电路主要消耗4类功率:内部短路功耗、漏电功耗、开关电容功耗和启动功耗。内部功耗是当门电路瞬变时,Vdd与地之间短路连接消耗的内部功率;漏电功耗是CMOS工艺普遍存在的寄生效应引起的;开关功耗则是来自负载电容,是由其充放电造成的;启动功耗是电子设备或电子元件在上电时,由于电容等器件充电而产生的功耗,此类功耗只发生在开机瞬间。

开关功耗与短路功耗合称为动态功耗。对CMOS电路而言,动态功耗基本上确定了总功耗。动态功耗为:

式中,f为开关频率;C为对应的充放电电容;Vdd为电源电压。从式(2)中可以看出,功耗与器件工作电压的平方成正比,并且和工作频率成正比。因此降低电路的动态功耗一方面是选择低电压供电的电路芯片;另一方面在于降低工作时钟的频率。对于嵌入式系统等智能处理器,由于在不同的工作状态下处理的工作量不同,所以根据工作量的不同,采用自主调整供电电压和工作频率的方法可以节省大量的动态功耗。

漏电功耗通常称为静态功耗。产生静态功耗的因素众多,包括处于没有完全关断或接通的状态下的IO以及内部晶体管的工作电流、内部连线的电阻、输入与三态驱动的上拉或下拉电阻等。静态功耗和器件的制作工艺有较大的关系。

在模块和电路的设计中,可以采用以下方法来降低静态功耗:①尽量选择低功耗的CMOS芯片进行电路设计;②尽量少用匹配和衰减电路;③ 由于IO线上的上拉或下拉电阻要消耗一定的电流,因此尽量避免使用这些电阻,在无法避免时,尽量使用大阻值的电阻;④在成熟电路上去掉调试时使用的电源和工作状态指示灯;⑤ 尽量不用双极晶体管,这些器件需维持一个恒定电流,从而增加了静态电流;⑥悬空的时钟输入会大大增加静态电流,因此将不用的时钟引脚连接至低电平;⑦ 提高集成度,减少器件间IO的使用。

4 FPGA的低功耗设计

FPGA是通信产品中最常用的信号处理与逻辑功能实现器件。如何降低FPGA的功耗已经成为一个重要的问题,许多学者从多个层面深入研究了FPGA的低功耗设计技术,在速度和面积方面,许多学者从系统级、开关级和门级等方面进行了深入研究。文献[3]和文献[5]提出了几种复杂的FPGA功耗模型,研究了FPGA的结构参数并估计了不同的结构对功耗的影响。目前,基于SRAM工艺的FPGA应用最为广泛,并且由于本文只涉及到应用中的低功耗设计,因此以ALTERA公司基于SRAM工艺FPGA为例,讨论其低功耗设计技术。

4.1 FPGA的功耗计算

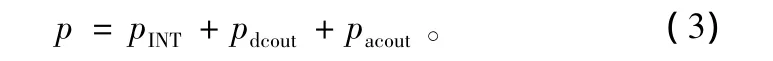

FPGA的功耗可以由表示为:

式中,pINT为无负载情况下的内部功耗,该值可以从相应器件的用户手册中查询得到;pdcout为FPGA的直流功耗:

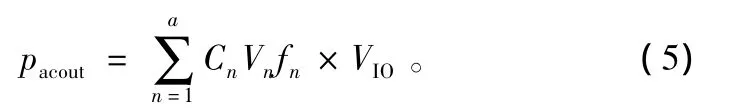

式中,pdcn为第n个管脚上的直流功耗;d为配置管脚总数目;pacout为器件的动态功耗,它决定于器件管脚的工作电压、容性负载和开关频率等。

式中,a为交流输出的管脚数目;Cn为该管脚的容性负载值;fn为输出开关频率;Vn为该输出管脚上开关输出电压值。对于5 V的IO电压,Vn的值取3.8 V,工作电压等于或低于3.3 V时,Vn取值与VIO相同。

4.2 FPGA的低功耗设计

由式(5)可见,在芯片确定的条件下,系统时钟频率对FPGA的总功耗有显著影响,因为时钟信号的开关活动最多,容性负载最大。不过,时钟速度又与处理能力直接有关。下面介绍几种在保持FPGA处理能力不变的前提下,通过改变软件的设计降低电路中时钟处理速度,来达到降低芯片功耗的方法。

4.2.1 并行技术

并行处理是在高速信号处理中经常采用的一种方法,其目的是将一条数据通路的工作分解到N条通路上完成,这样每条数据通路的工作频率都为原来的1/N,以此达到可以处理高速信号的目的。并行处理技术用在低功耗设计中其本质就在保持电路处理能力的基础上通过增加电路的面积来达到降低式(5)中的fn,进而达到降低功耗的目的。

当然,增加的电路面积和连线资源会导致电容Cn的增加,并且输出端口增加的二选一电路也会导致部分功耗,但这部分功耗的增加与并行处理所节省的功耗相比还是很小的,几乎可以忽略不计的[6]。

4.2.2 流水线技术

流水线技术也是一种通过增加面积来提高速度的通用设计技术[7]。在电路中插入寄存器(流水线),既可以理解为提高了系统运行速度,也可以理解为通过采用较低的时钟速率,达到了相同的处理能力。这是因为流水线结构实际上是把一个功能模块分成n个阶段进行流水线作业,每个阶段由一个子模块来完成,在子模块之间插入寄存器,以驱动这些小模块,在低速情况下,每个模块完成了整个处理工作的1/n。尽管增加的寄存器,增加了部分功耗,但与速度的降低带来的功耗的降低相比,这部分功耗几乎可以不计。

4.2.3 异步技术

同步电路是由同步时钟统一驱动的电路,由于同步电路中时钟速率往往高于数据速率,且仅作为驱动的时钟贯穿整个程序,因此造成了很大的功耗浪费。而异步逻辑电路不采用全局时钟,而是用握手信号协调模块间的运作,因此异步电路本质上是数据驱动的电路。因为没有时钟驱动,在没有数据,或者数据不变化,电路不动作,因此电路翻转次数的降低节省了大量功耗[8]。

在实际设计中,异步电路实现起来有一定的难度,特别是在高速电路中,但对于一些低速或对时序要求不严格的设计,异步电路还是有很大优势。

4.2.4 门控时钟设计技术

门控时钟设计技术是指在FPGA设计中,为每一个最小的功能模块设置时钟控制信号,在程序运行过程中,根据需要将不参与运算的模块输入时钟关闭,以节省功耗的设计技术。该技术也是一种用于同步电路中的低功耗设计技术[9,10]。

5 结束语

在卫星移动通信终端的研制中,通过采用上述技术和设计方法,使得正样产品的待机和单收状态功耗分别比初样产品降低了60%和38%以上,特别是实现了低于200 mW的待机功耗。测试结果表明,采用低功耗设计技术对终端的推广应用起到了极大的促进作用。

本文结合卫星移动通信终端的特点,从整机、单元电路、主要元器件及FPGA代码设计等几个方面对低功耗设计进行详细的讨论,并在实际工程项目应用中取得较好的效果。

[1] 罗义军,姚彦通.通信系统中的低功耗设计[J].电信科学,2005(6):13-15.

[2] 田 朋,尹 光.CMOS电路中系统级低功耗设计研究[J].辽宁大学学报自然科学版,2008,35(2):125-128.

[3] 苏志雄,郭慧晶,吴一亮,等.无线传感器网络SOC芯片的低功耗设计[J].微计算机信息,2007,23(2):133-135.

[4] 李 广,班亚明,赵燕飞.新型便携式卫星通信终端设计[J].无线电通信技术,2012,38(3):23-25.

[5] 张 杰.一种低功耗手持终端的基带单元硬件平台的设计[J].数字技术与应用,2012(5):166-167.

[6] 朱卓娅.锂离子电池管理芯片的研究及其低功耗设计[D].南京:东南大学博士学位论文,2005(1):11-32.

[7] 何艳霞,何永泰.FPGA低功耗的设计研究[J].楚雄师范学院学报,2012,27(6):22-25.

[8] 郭宏泓.超低功率异步电路设计研究[D].镇江:江苏大学,2009:2-3.

[9] 胡 靖.集成电路低功耗设计可逆逻辑综合及性能分析[D].哈尔滨:哈尔滨工程大学博士论文,2008(9):18-26.

[10]谢 亮.嵌入式系统低功耗设计[D].上海:上海交通大学硕士论文,2011(9):30-38.