基于FPGA的高速图像处理平台设计

2013-01-05卿粼波何小海

陈 序, 卿粼波, 何小海

(四川大学电子信息学院图像信息研究所,四川成都610064)

0 引言

图像采集是图像处理的基础,随着图像采集的帧频和分辨率越来越高,对高速图像处理及显示的要求也越来越高。大多数高速摄像头采用Camera Link接口,Full型Camera Link摄像机数据传输率可达680MB/s,如何设计并实现一个高速的图像处理平台,具有重要意义。多数针对图像处理的平台是通过PCI或USB接口将采集到的图像发送到PC机再进行图像处理和显示,系统体积较大,且成本偏高,受到PC机处理速度限制,图像显示的实时性会受到影响[1]。少数嵌入式平台,没有对采集到的原始图像进行处理,而直接进行显示,显示的图像质量会受到影响,并采用小容量的SDRAM来缓存数据,不能应用到数据量大的图像处理中[2]。

设计了一种基于FPGA的高速图像采集、图像处理和图像显示平台。FPGA把采集到的图像按帧缓存到大容量存储芯片DDR2 SDRAM中,再从DDR2中读出每帧图像进行预处理,DSP对图像进行复杂算法处理,FPGA最后把图像发送到DVI编码芯片进行显示。图像处理的速度快,显示实时性好。实现了平台体积小,成本低,处理数据量大,处理速度快,应用广泛的目的。

1 系统硬件设计

1.1 硬件架构

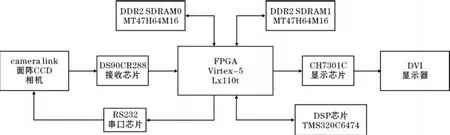

系统硬件架构由Camera Link信号转换芯片DS90CR288、串口配置芯片、一片FPGA芯片、DVI显示芯片CH7301C、8片DDR2 SDRAM芯片MT47H64M16、一块DSP芯片组成。系统的硬件架构框图如图1所示。

图1 系统硬件框图

1.2 主要硬件模块

FPGA选用Xilinx公司virtex5系列中的lx110t,采用65nm工艺,核心电压为1.0V,拥有17280个Slice,BRAM容量为5328KB,16个GTP模块,20个 I/O Bank,最大可用I/O数达680个[3]。DVI发送芯片采用CH7301C,最高显示分辨率可达1600×1200,像素时钟最大为165M,使用低抖动锁相环,I2C端口编程,并为RGB输出提供10-bit高速视频DAC,低电压接口支持图形设备。DDR2 SDRAM 采用MT47H64M16-37E,单片容量为1Gb,构成为:8Meg×16×8bank,数据速率为533Mhz。设计使用4片DDR2组成一个通道,位宽扩展为64bit,8片组成双通道。DSP芯片采用TI公司的TMS320C6474,集成了3个1GHz的TMS320C64x+内核,具有3GHz的数字信号处理性能,数据的处理能力为24000 MMACS(16bit)或48000 MMACS(8bit)。

1.3 FPGA外围接口设计

(1)FPGA和DS90CR288的接口设计。DS90CR288共有1位时钟信号和28位数据信号连接到FPGA,28位数据信号包含24bit图像数据以及传输数据需要的帧信号、行信号和数据有效信号。

(2)FPGA和DDR2 SDRAM的接口设计。MT47H64M16主要有16位数据信号ddr2-dq[15:0],差分数据脉冲信号ddr2-dqs、ddr2-dqs-n,地址总线信号ddr2-address[12:0],行列地址有效信号,片选信号等。

(3)FPGA和DSP的接口设计。通过serial rapidIO接口[4]连接,FPGA用GTP作串并转换,收发各有一对差分信号。

(4)FPGA和CH7301C的接口设计。CH7301C主要信号线包括,I2C信号线,差分时钟信号对,行信号线、帧信号线、数据信号线及使能信号线。

2 Camera Link图像采集系统

Camera Link是一种串行通信协议,设计用于点对点自动视觉应用。是基于国家半导体公司的通道链路接口,经过扩展可支持通用LVDS数据传输。Camera Link接口标准有Base,Medium,Full 3种配置模式。Base配置使用了24位像素数据(以及3位视频同步数据)来实现最大255 Mbps的数据量。Medium配置额外增加了另外24位数据,实现最大510 Mbps的数据量。Full配置使用64位数据,实现最大680 Mbps的数据传输率。

系统前端图像采集采用JAI公司的Base型彩色数字摄像机CV-M71CL,CV-M71CL在全读取模式下采集分辨率为767*576,帧频为60Hz。DS90CR288芯片将接收到的camera link信号转换成28位单端信号发送到FPGA,FPGA将接收到的信号分离成24位RGB信号、像素有效信号DVAL、帧信号FVAL、行信号LVAL[5],并将它们传送到图像处理系统。在图像采集前,系统中的串口通信模块,可以发送串口信号,对摄像机进行配置。

图像采集系统和处理系统之间由于时钟不匹配,需要连接一个前端异步FIFO。在向FIFO中传输每帧图像前,处理系统及显示系统返回的初始化信号init-done需要有效,保证数据位不错乱。

3 FPGA图像处理系统

系统采用FPGA对图像进行预处理,DSP进行协处理。图像存储模块对每帧图像进行缓存,图像处理模块再读出图像进行处理。处理系统包含多种处理方法,可以对图像进行滤波,转换,对比度调节,亮度增强等操作。应用中可以在FPGA中根据实际需求设计相应的处理方法。处理的数据可以发送到DSP作进一步的复杂算法处理,也可以直接发送到图像显示系统进行图像显示。FPGA图像处理系统模块框图如图2所示。

3.1 图像存储模块

图像存储模块对采集到的每帧图像进行缓存。系统使用两片DDR2 SDRAM进行乒乓操作[6]。采集到的第一帧图像写入ddr-controller-0,第二帧图像写入到ddr-controller-1的同时去读取ddr-controller-0中的第一帧图像,下一帧图像写入ddr-controller-0的同时,读取ddr-controller-1中的图像,如此循环下去。FIFO解决采集模块、存储模块、显示模块时钟域不同的问题,FIFO设置empty、full标志位保证在写DDR2芯片数据时前端FIFO不为空状态,读取DDR2芯片数据时后端FIFO不能为满状态。图像存储模块包含两个状态机,一个控制两片SDRAM的交替读,另一个控制SDRAM的交替写。存储模块包含两个DDR2 SDRAM控制器,控制器作为DDR2芯片和乒乓操作之间的接口,为乒乓操作模块提供数据总线、地址总线及控制信号。

图2 图像处理系统模块框图

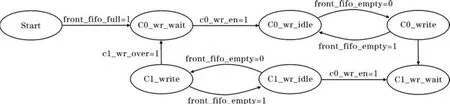

写DDR2状态机如图3所示。在前端FIFO的front-fifo-full标志位为1的时候,进入ddr-controller-0的写操作等待状态c0-wr-wait,ddr-controller-0在c0-wr-en有效时进入c0-wr-idle,前端FIFO的empty标志位不为1,则进入c0-write状态进行数据写,否则进入c0-wr-idle状态等待数据到来,直到一帧图像写满。写满一帧图像后进入ddr-controller-1的写等待状态c1-w r-wait,同时使能ddr-controller-0的读能使标志位c0-rd-en。ddr-controller-1的写操作过程与ddr-controller-0相同。

图3 DDR2乒乓操作写状态机

读DDR2状态机如图4所示。状态机启动时处于c0-rd-wait状态,当ddr-controller-0写满一帧后,进入读空闲状态c0-rd-idle。在后端FIFO的full标志位部位1时,不停的读出数据写入后端FIFO中,直到一帧图像读完,然后进入ddr-controller-1的写操作,同时使能ddr-controller-0的写使能标志位c0-wr-en,告知DDR2写状态机可以对ddr-controller-0写下一帧数据。ddr-controller-1的读操作完成后再进入ddr-controller-0的读操作,如此循环下去。

图4 DDR2乒乓操作读状态机

3.2 图像处理模块

图像在采集、传输过程中,由于成像设备、传输介质、外界环境等影响,信号传输会加入有大量的噪声,得到图像的质量受到影响。对图像进行处理可以得到更好的显示效果和应用。FPGA适合在空间域对图像进行预处理[7],DSP则适合图像压缩、图像识别等复杂算法的图像处理。

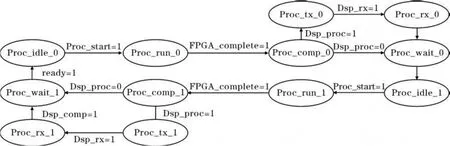

当一帧图像存储完成后,启动FPGA图像处理模块,将process-start信号置1,开始对图像进行预处理,处理过程中和乒乓操作模块配合反复对DDR2-SDRAM进行读写,处理完成后读出图像发送到DVI显示系统中进行显示,最后返回完成信号process-end给乒乓操作模块,接下来对另一块DDR中的图像作处理。处理过程中如果需要对图像作进一步复杂算法的处理,高速串口模块通过Serial RapidIO协议将数据传送到DSP,DSP处理完成后再传回数据。若当前帧图像处理时间过长,乒乓操作模块不能写入下一帧,则丢掉当前帧,保证系统稳定运行。图像处理模块工作的状态机如图5所示。

图5 图像处理模块状态机

4 DVI图像显示系统

DVI是基于最小化传输差分信号(Transition Minimized Differential Signaling,TMDS)的数字信号传输技术。TMDS可以对像素数据进行编码,然后通过串行接口进行传递。图像显示系统产生的数字信号发送到CH7301C,CH7301C对信号按照TMDS协议编码后发送到显示器。

设计采用CH7301C芯片进行TMDS信号的发送,DVI显示模块按照显示的标准生成差分时钟、24位RGB数据及数据有效信号、帧信号、行信号,并发送到CH7301C[8]。

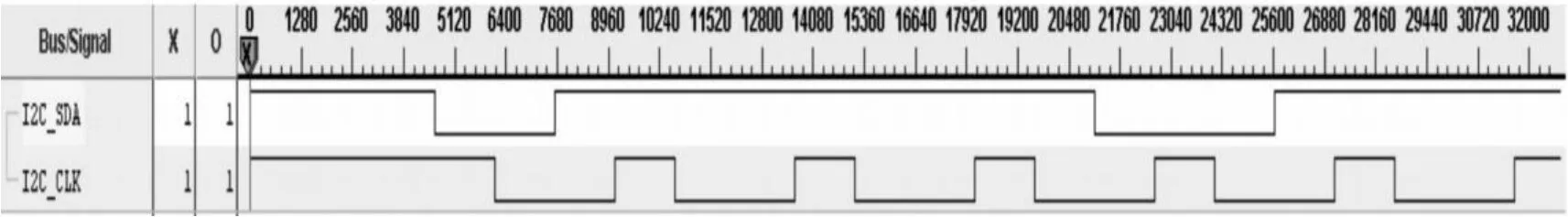

系统需要通过I2C接口对CH7301C的寄存器进行配置,I2C信号波形图如图6所示。DVI显示的实时信号波形如图7所示。

图6 I2C信号采集波形图

图7 DVI显示信号采集波形图

5 平台验证及结论

平台完成了高速图像的采集、发送和显示,能得到稳定的图像。基于FPGA的高速图像的处理平台制作并调试完成,图8是高速图像处理平台的电路板,图9是Camera Link采集和DVI实时显示的效果图。

图8 高速图像处理平台电路板

图9 实时采集和显示的效果图

文中设计的平台相比传统的采集显示平台,采集速度更快,最高能达到680MB/s;显示分辨率更高,达到1600×1200,60帧/s;使用FPGA和高性能DSP进行图像处理,处理速度更快,满足实时处理需求;采用8片大容量的DDR2芯片,缓存图像容量更大。实现了对图像的高速采集、存储、处理和显示,并可替代基于专用采集卡和PC机的数字图像处理系统,到达了成本低,体积小,携带方便,图像清晰,应用广泛的目的。

[1] 李宁,汪骏发.基于Camer a Link的高速数据采集系统[J].红外,2005(7):31-39.

[2] 李飞,刘晶红,李刚,等.基于FPGA的数字摄像机输出视频DVI显示[J].激光与红外,2011(11):1258-1261.

[3] Xilinx,Virtex-5 FPGA User Guide,ug190(v5.3)May 17,2010.

[4] LogiCORE IP Serial RapidIO v5.6 User Guide:Inc.XILINX.UG503 July 29,2011.

[5] 王鸣浩,陈涛,吴小霞.基于Camera Link接口的高帧频数字图像采集显示系统[J].微电子学与计算机,2011(3):149-152.

[6] Xuzhi WANG,Yanru MA,Wanggen WAN.Design of DDR2 SDRAM Controller for Video Post Processing Pipeline[J].Wireless Mobile and Computing,2009:117-120.

[7] Rafael C Gonzalez,Richard E woods.阮秋琦,阮宇智译.数字图像处理digital Image Processing(第二版)[M].北京:电子工业出版社,2010.

[8] 孙志亮,单金山.基于FPGA的DVI显示在红外监视系统中的应用[J].激光与红外,2008(10):1059-1062.