一种基于RS485的SoC产品测试平台的设计

2012-12-30黄世震陈丽红

黄世震,陈丽红

(福州大学福建省微电子集成电路重点实验室,福州350002)

随着集成电路和半导体工艺技术的发展,在单一集成电路芯片上就可以实现一个复杂的电子系统,如智能卡、SD卡等,SoC正是在集成电路向集成系统转变的大方向下产生的。由于SoC产品的功能模块比较多,一般从封装厂里出来后,要对各个功能模块进一步测试,从而剔除不良品,然后根据不同的用途对产品进行初始化,完成测试过程。在产品的批量生产过程中,传统的测试方法采用人工手动测试,存在几个问题:①效率低,无法满足SoC产品对时间的要求;②测试结果容易受人为因素的影响,无法满足SoC产品对可靠性的要求。本文提出一种基于RS485总线的自动化批量测试系统的设计方法,以现有的封装厂测试平台为基础,通过自行研制一些测试板,与现有的测试平台对接,实现SoC产品的自动化批量测试,提高生产效率。文中将以一款TF卡为例,在介绍完测试平台的硬件结构之后,侧重介绍测试平台的软件设计方法。

1 测试平台概述

RS485总线是业界应用最广泛的标准通信接口之一。它采用平衡发送和差分接收方式实现通信:发送端将串行口的TTL电平信号转换成差分信号A、B两路输出,经过线缆传输之后在接收端将差分信号还原成TTL电平信号。由于传输线通常使用双绞线,又是差分传输,所以有极强的抗共模干扰的能力,传输距离在1 000 m以上,可互联多达256个节点,非常适合组成成本低廉的多机通信系统。RS485是一个多引出线接口,这个接口可以有多个驱动器和接收器,采用主从式通信方式,可以实现一台上位机与多台下位机之间的串行通信。这种通信方式特别适合应用于本测试平台中[1]。

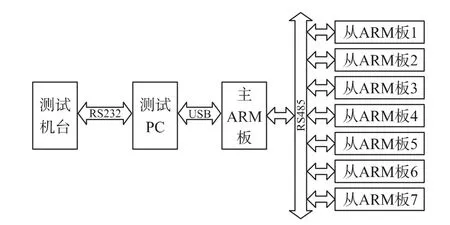

测试平台主要包含3个部分,即测试机台、测试PC和主从ARM测试板。测试机台负责待测产品的安装、测试的启动和按照测试结果进行分类;测试PC负责发送测试机台的启动命令、对主ARM测试板发送命令以及将测试结果反馈给测试机台;主ARM测试板负责接收测试PC的测试命令,并将其分发给多个从ARM测试板以及收集从测试板的测试结果反馈给测试PC。测试平台连接图如图1所示。

图1 测试平台连接图

具体的实施方法为:将测试机台、测试PC、主从ARM测试板连接起来,测试机台将测试样品送入测试接口,然后通知测试PC启动测试,测试PC通过USB接口发送测试命令给主ARM测试板,主ARM测试板通过RS485总线通知所有从ARM测试板启动测试,每块ARM测试板(包括主ARM测试版)按照程序对样品中的模块进行测试,并将测试结果反馈给主测试板,主测试板将结果汇总后反馈给测试PC,测试PC再将结果反馈给测试机台,最后测试机台根据测试结果对各个测试样品进行分类放置,放入新的测试样品,启动下一轮测试。

2 测试平台硬件设计

2.1 测试板硬件设计

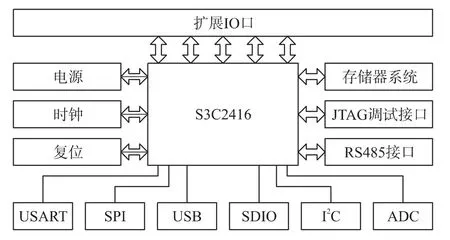

测试板采用32 bit高性能ARM核微处理器S3C2416,根据嵌入式系统的最小系统设计原理,进行接口设计和硬件设计,使测试板满足测试需要[2-4]。测试板的硬件框图如图2所示。

图2 测试板硬件框图

主要电路功能简介如下:

电源电路 为整个系统供电,要求稳定性高。测试板上有多个系统电压,5 V,3.3 V,1.3 V,1.2 V等,能够满足SoC产品的测试需要。

复位电路 完成系统的上电复位和系统在运行时用户的按键复位功能;

系统时钟电路 使用外部晶振起振,提供时钟信号。本测试系统使用12 M晶振时钟;

JTAG电路 测试平台调试与测试接口,控制芯片的运行并获取内部信息;

USART/SPI等接口 用于满足不同SoC产品测试时的时序要求;

RS485接口电路 采用SN65HVD33芯片构成,微处理器的标准串行口通过RXD直接连接SN65HVD33芯片的R引脚,通过TXD直接连接SN65HVD33芯片的 D引脚。微处理器的 GPD3、GPD4引脚分别和SN65HVD33芯片的RE和DE相连,控制SN65HVD33芯片的发送器/接收器使能:SN65HVD33发送器有效时,微处理器可以向RS485总线发送字节;SN65HVD33接收器有效时,微处理器可以接受来自RS485总线的数据字节。任一时刻SN65HVD33芯片中的接收器和发送器只能有1个处于工作状态[1]。

2.2 测试板编码设计

由于RS485总线是采用半双工通信方式,每次只能有一对节点进行通信,故要求每块测试板有自己的地址编号[5]。本测试平台共有4组,每组中都包含8块ARM测试板,设计时在每块ARM测试板上都装上8个拨码开关,其中低4位(4∶1)表示从ARM测试板的编号,高4位(5∶8)表示主ARM测试板编号,有效编号为0~7。由于主ARM测试板在完成通信的同时也需要进行样品测试,其本身也相当于一块从ARM测试板,因此其拨码开关的低四位始终设置为0,其编号为0,其它7块从ARM测试板编号为1~7。这样就保证了地址编号的唯一性,能够满足RS485通讯的要求。例如:若拨码开关的状态为00100001,则表示该测试板为第2组中的第2(编号为1)块测试板,为从测试板;而主测试板的编号默认为0,若拨码开关的状态为00100000,则表示该测试板为第2组中的第1(编号为0)块测试板,为主测试板。

3 测试平台软件设计

3.1 测试PC端软件设计

测试PC端软件采用VC6.0编程实现,串口的通信编程利用了COMM串行通信控件,方便地访问串口,实现数据的接收和发送[6]。测试PC端显示界面主要包括测试PC端与主从ARM测试板的通信状态、测试板的测试结果等。

测试软件通过RS232接收机台命令,并控制测试板进行相应的测试。以一种SoC产品-TF卡为例,其测试界面如图3所示。

其中区①为串口参数设置栏,测试开始前须检查串口号及参数设置与机台端是否一致,然后打开串口;区②为设备状态栏,显示运行时各个测试板的状态,例如上图中在A组(主板编号为1)设备中,只有第1块(主测试板)与第2块测试板连接正常,可以进行测试,其余各测试板不能进行测试。区③为其他功能栏,其中“发送测试”用于手动测试过程,实际机台自动测试过程中不需使用;“量产配置文件”用于针对不同类型的TF卡选择不同的配置信息;“选择平台”用于生产不同类型的TF卡。区④为统计信息栏,显示测试总数、成功的次数、失败的次数。

图3 生产测试工具主页面

测试完成界面如图4所示。

图4 测试完成界面

3.2 主ARM测试板软件设计

主ARM测试板接收测试PC发送的USB命令,根据命令运行相应的测试程序,同时将命令广播给从ARM测试板,启动所有ARM测试板的测试,并将测试结果反馈给测试PC。主ARM测试板控制流程如图5所示。

3.3 从ARM测试板软件设计

从ARM测试板接收串口数据并解析,根据命令运行相应程序,并向主ARM板发送反馈信息。从ARM测试板控制流程如图6所示。

图5 主ARM测试板控制流程图

图6 从ARM测试板控制流程图

3.4 主从ARM测试板通讯协议设计

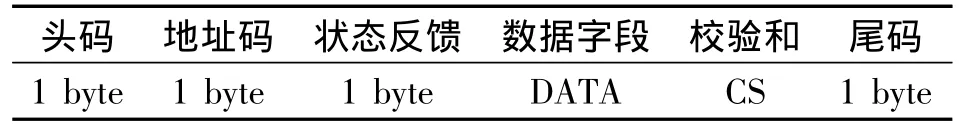

3.4.1 帧格式

RS485总线只制定了物理层电气标准,对上层通信协议没有规定,这给设计者提供了很大的灵活性。一套完整的通讯协议应从多个方面加以考虑,既要求结构简单、功能完备,又要求具有可扩充性与兼容性,并且尽量标准化。本测试平台采用的通讯协议是在充分考虑到平台本身的功能特点,再参考国际标准通信规约的基础上制定的,适用于主ARM测试板与各个从ARM测试板进行点对点的或一主多从的数据交换方式,具体如下:

主ARM测试板命令帧:

头码 地址码 操作命令 数据字段 校验和 尾码1 byte 1 byte 1 byte DATA CS 1 byte

从ARM测试板响应帧:

头码 地址码 状态反馈 数据字段 校验和 尾码1 byte 1 byte 1 byte DATA CS 1 byte

头码 数据帧起始标志,用于触发通信,本协议中规定以“FF”为头码。

地址码 从ARM测试板的地址编码,设定范围:1~7,0为广播通信地址。

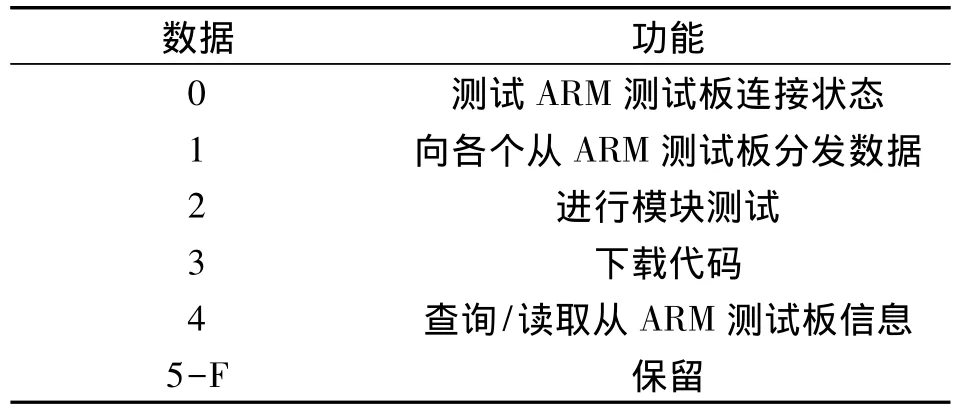

操作命令 操作命令存在于主ARM测试板发送的数据帧中,用于定义发送此次数据帧要完成的任务。根据操作命令的不同,帧长度也有所不同。操作命令为一个字节长度,每一位代表不同的内容对应不同的命令代码,具体内容如下所示。

数据 功能0测试ARM测试板连接状态向各个从ARM测试板分发数据2进行模块测试3下载代码4查询/读取从ARM测试板信息5-F 保留1

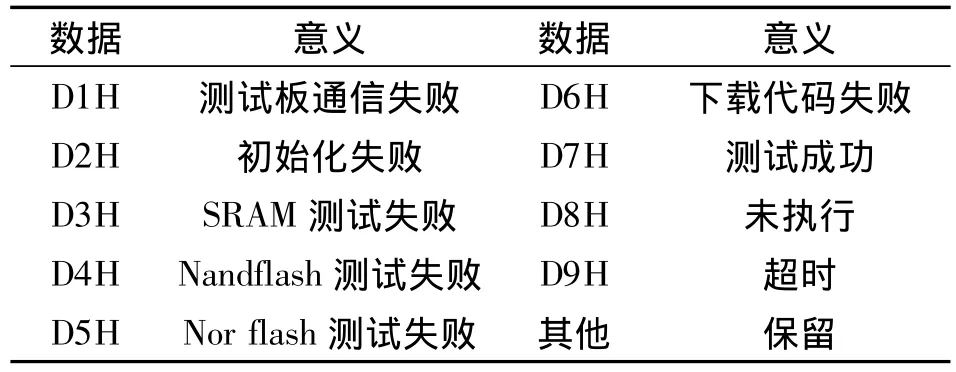

状态反馈 从ARM测试板对主ARM测试板的响应,主要用于回馈从ARM测试板对主ARM测试板命令帧的执行情况。从ARM测试板响应定义如下:

数据 意义 数据 意义D1H 测试板通信失败 D6H 下载代码失败D2H 初始化失败 D7H 测试成功D3H SRAM测试失败 D8H 未执行D4H Nandflash测试失败 D9H 超时D5H Nor flash测试失败 其他 保留

数据字段 本字段分两部分,第1部分为一个字节,表示整个数据字段的字节数,L=0表示无数据域。第2部分则为通信中要传输的数据内容,传输内容的长度随着操作命令而改变。

校验和 从地址码开始到校验和之前的所有字节的模256的和。

尾码 数据帧结束标志,本协议中规定以“DD”为尾码[7-8]。3.4.2 通信过程

主ARM测试板与从ARM测试板构成的多机通信系统采用主从式结构,数据通信总是由主ARM测试板发起。主ARM测试板处于发送状态时,从ARM测试板总是处于接收状态。主ARM测试板定时向从ARM测试板发送地址帧,这时每块从ARM测试板都中断接收并与本机地址比较,若主ARM测试板发送的地址信息与本从ARM测试板的编号相符,则接收该数据,否则继续接收总线上的数据。若从ARM测试板需要发送数据,则必须等到主测试板轮询过该从ARM测试板时,才可提出请求。这种网络模式下,从ARM测试板不会“侦听”其他从ARM测试板对主ARM测试板的响应,这样就不会对其他从ARM测试板产生错误的响应。

当主ARM测试板发出数据帧后,如果在规定的时间内没有收到从机的应答帧,则主机认为帧丢失并重发数据帧;如果发送3次仍没有收到应答帧,则系统认为该次通信失败,报错[5,9]。

4 结论

本文提出了一种基于RS485总线的SoC产品自动化批量测试平台的设计,并以一种TF卡为例介绍了测试平台的硬件设计和软件设计。目前该测试平台已应用于测试厂TF卡的各模块(Nor flash、Nandflash、SRAM)的测试,经批量测试结果表明,使用该测试平台1 h测试TF数量为传统测试方法的32倍,显著地提高了生产和测试的效率。

[1]广州周立功单片机发展有限公司.RS485协议标准[S].周立功公司,2004.

[2]杜春雷.ARM体系结构与编程[M].北京:清华大学出版社,2003.

[3]马忠梅等.ARM嵌入式处理器结构与应用基础[M].北京:航空航天大学出版社,2001.

[4]ARM 公司.ARM Architecture Reference Manual[S].ARM 公司,2000.

[5]范越等.基于RS485总线的自动化检测系统的研制[J].现代电子技术,2008.(05):142-144.

[6]谢春萍,陈铁军.基于RS485的多机串行通信系统的设计[J].玉林师范学院学报,2006.(05):158-161.

[7]李圣明,曹玉强,孙清.基于 RS485总线的分布式测控系统[J].仪表技术与传感器,2004.(11):22-24.

[8]谢军芳.基于RS485的分布式整流桥测试系统[J].硅谷,2008.(19):45-46.

[9]张冰.一种电子产品老化测试系统的设计与实现[J].工业控制计算机,2007.(20):13-14.