CMOS电路主要特性的教学与研究

2012-12-17华东师范大学信息学院何金儿

华东师范大学信息学院 何金儿

上海商学院信息学院 蔡京玫

1.引言

CMOS数字集成电路是目前大规模和超大规模数字集成电路中广泛应用的一种电路结构,与NMOS和PMOS数字电路相比较,CMOS数字电路在功耗、噪声抑制、抗干扰能力等方面具有明显的优势。并且由于CMOS数字电路的集成度可以做的非常高,在总体性能上已经超出了TTL电路,因此得到了迅速而广泛地运用。目前CMOS电路占据了99%的市场份额。特别是CMOS电路的制造工艺已经达到了深亚微米范围后,器件特性的变化带来了一系列需要重视的问题。但是在高校传统的数字电路课程的教材中,对TTL电路的原理和特性讲述的比较详细,对CMOS电路的原理和特性却介绍过于简单。特别是对CMOS电路的关键的几个电气特性讲述的更少。因此揭示CMOS数字电路的构成,研究CMOS电路电气特性以及CMOS电路在设计数字系统中一些注意事项,是数字电路课程的教学和正确设计数字系统的一个需要引起注意的环节。

2.反相器的静态特性

在CMOS数字电路中,反相器是所有数字电路设计的核心。几乎所有的CMOS电路的电气特性都可以从反相器得到的结果中推断出来。

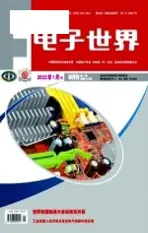

Nmos管的开关特性如图1a所示,UT是Nmos管的开启电压,当电压│UGS│≥│UT│时,Nmos管呈现出导通的状态,导通电阻的阻值与UGS的大小呈非线性变化,如图1a所示,输出电阻的典型值在Kῼ范围内。当电压│UGS│≤│UT│时Nmos管呈现出截止的状态,其电阻非常大。在Pmos管的开关特性中如图1b所示,PMOS管和NMOS管成对偶性

在CMOS电路中,推荐的逻辑高电平为VDD,低电平为VSS。因此从图1C所示的反相器电路图中可以看出:当输入逻辑高电平时,此时│UGS│≥│UT│,因此Nmos管导通,UO=VSS。反之Pmos管导通,UO=VDD。

假设一个反相器的输入变量为In,输出变量为Out,反相器的输出电压与输入电压的关系为:,传输特性曲线如图1.d所示。电压传输特性曲线是对CMOS反相器静态特性的最佳的描述。

从中可以看出反相器的特点:

a.输出电压摆幅等同于电源电压,对干扰信号和噪声有很强的抗干扰能力。

b.因为MOS管内部的栅极是一个完全的绝缘体,所以有着极高的输入阻抗。反相器静态时的输入电流几乎为零。

c.反相器在静态时,Pmos管和Nmos管总有一个是截止的,因此流过VDD和VSS间的电流仅仅反相器内部的漏电流。常温下一个含100万门的芯片,在2.5V电压下工作的功耗通常在0.125mW。

3.反相器的动态特性

3.1 反相器的动态功耗和工作频率的

关系

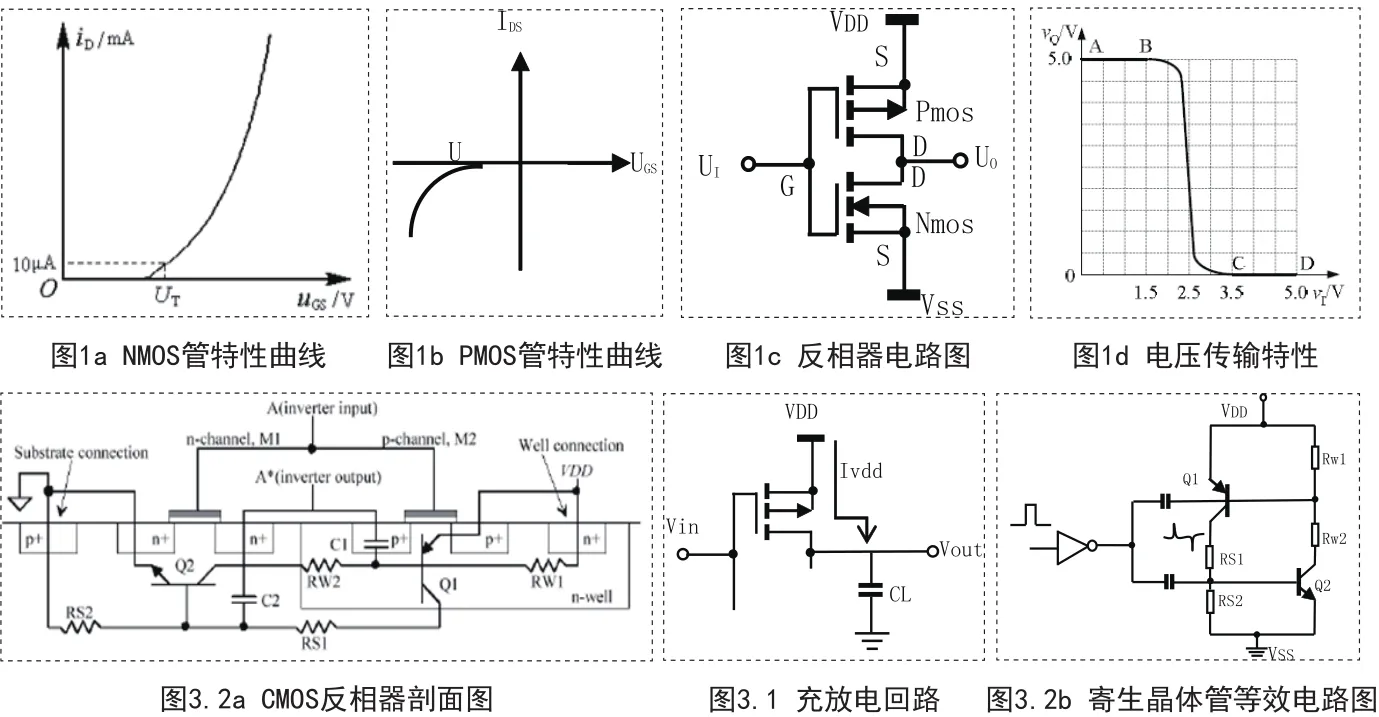

反相器的动态功耗主要是由于负载电容的充放电消耗的。当PMOS管导通时,NMOS管截止时,CL从电源吸取了一定数量的能量,输出电压从0→1。当PMOS管截止,NMOS管导通时,电容CL通过NMOS管释放能量,输出由1→0。如图3.1所示。

假设输入的是一个理想的方波,即上升沿和下降沿为零,为简化计算,不考虑Pmos管和Nmos管在翻转期间二个场效应管同时导通的情况。反相器输出从0→1翻转期间电容从电源中取得的能量为对此翻转区间的积分:

在电容上存储的能量Ec通过通过对其在相应周期上对瞬时功耗积分求得:

由此可以看到,从电源中吸取能量的一半消耗在MOS管中,另一半存储在电容C中,在1到0的翻转时CL上的能量通过PMOS管进行放电。

由此可以推出,如果考虑到反相器工作频率的话,反相器静态时0→1翻转时的功耗为:

反相器的工作频率越高,从电源中吸取的能量也越大。

3.2 电源和输入端信号幅度对CMOS的影响

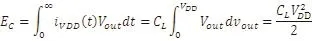

虽然CMOS电路具有很多的优点,但是由于有一些自身固有的工艺结构引发的寄生效应,如果使用不当,很容易引起CMOS电路的闩锁效应,电路发热直至烧毁。在使用时必须引起注意。

闩锁效应就是指CMOS器件所固有的寄生双极晶体管(又称寄生可控硅,简称SCR)被触发导通,而触发和导通常常是由于CMOS器件的工作电压波动,或者是输入端信号幅度波动等因素引起的。触发后会在在CMOS器件的电源VDD与地线VSS之间形成低阻抗大电流通路,导致器件出现逻辑错误,发热甚至烧毁器件的现象。如图3.2a和3.2b所示。

在正常状态下,VDD和VSS间只有很小的电流通过。由于输入端的脉冲产生瞬间的上冲,或者电源波动产生的波动,在电阻Rw2端产生了电流IRS,IRS电流在寄生的PNP管基极产生了压降,如果压降大于0.7V,寄生的PNP管进入了导通状态。同样,寄生的PNP管导通后在电阻Rs处也产生了压降,又促使寄生的NPN管进入导通状态。这样一个闭合的正反馈的过程就形成了。同样,通过C2的下降沿也会产生同样的效果。此时VDD和VSS间会有大电流通过,即便是电源波动消失或者干扰波消失,电路内仍然有电流通过,只有断开电源才能使得CMOS电路内的正反馈消失。

由以上分析可以得出发生闩锁效应的条件为:

a.当输入端或者输出端出现了大于VDD或者小于VSS的信号,满足了寄生晶体管产生正反馈的条件。

b.电源电压产生了波动,当电压波动过大时使得寄生的晶体管为正偏置,因而产生了闩锁效应。

为防止产生闩锁效应,输入端或者输出端要满足以下条件

有上述分析可得出电源和输入信号的注意事项是:

(1)在布线的时候,CMOS的电源必须加上退耦电容。因为过高的电压波动会使得IRS电流增大,寄生的双极晶体管发生正反馈而产生闩锁效应。

(2)电源提供的电流选择一个合适的数值,避免一旦发生闩锁效应的时候,减少因电流过大而烧毁电路的可能.

(3)输入端的信号不能超过CMOS电路的工作电压VDD。过高的输入电压会使电路进入正反馈的状态,从而发生闩锁效应。从CMOS电压传输特性曲线中可以看出在输入信号VIH=VDD,VIL=VSS时,CMOS电路的噪声容限等参数为最佳状态。

(4)输出端或输入端避免跨接大电容。在开机或关机时,对电容的瞬间的充放电同样会改变寄生三极管的偏置电压而使CMOS进入闩锁效应,电容一般不能大于0.01µ。在负载接有大电容时,可以串联电阻,如图3.3所示。

(5)避免信号长线传输,因为信号在长线传输中的分布电容可能会产生振荡引发产生闩锁效应。长线连接的方法如图3.4所示。

4.结束语

理解CMOS电路的电器特性是正确使用CMOS电路的关键。从CMOS电路电压传输特性的曲线中,可以读出电气特性的诸多参数。理解CMOS电路的闩锁效应的触发机制,是正确使用CMOS电路的关键。在CMOS电路飞跃发展的时代,特别是在CMOS电路进入了深亚微米时代,理解和掌握CMOS集成电路的电气特性显得特别重要。

[1]沈雷.CMOS集成电路原理及应用[M].北京:光明日报出版社,1987.

[2]Anantha Chandrakasan.数字集成电路—电路、系统、与设计(第二版)[M].北京:电子工业出版社,2012.