基于FPGA的布撒传感器节点设计

2012-11-24张国义

张国义 ,王 越 ,王 卓 ,韩 琪

(1.西北工业大学 现代设计与集成制造技术教育部重点实验室,陕西 西安 710072;2.61683 部队,北京 100094;3.北京神州数码思特奇信息技术股份有限公司,北京 100085;4.北京航天发射技术研究所,北京 100076)

无线传感器网络 WSN (Wireless Sensor Network)具有快速布置、网络自组织和系统容错的特点,这使它成为C4ISRT所希望的感知技术,也使WSN成为对战场进行监测一个好手段。美国国防部高级规划署(DARPA)多年前就启动了 Sensor IT(Sensor Information Technology)计划,其目的就是将不同类型的传感器、可重编程的通用处理器和低成本无线通信技术组合起来,自主建立一个廉价的大规模高密度的网络系统。本文基于远程火箭布撒的传感器子弹应用要求,研究了基于FPGA的传感器节点。

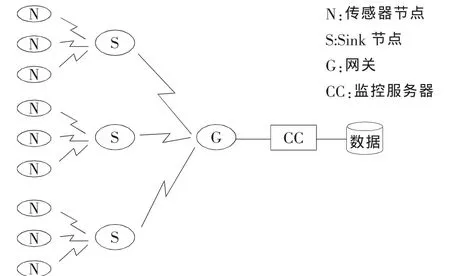

WSN体系结构如图1所示,通常包括传感器节点、汇聚节点、外部网络和用户界面。采集传感器节点部署在感知区域内部或附近,能够通过组织构成网络,传感器节点将采集到的数据经过单跳路由传输到传感器节点,再由传感器节点通过外部网络传送到处理中心进行集中处理[1-5]。

1 传感器节点中频接收机的构成和功能

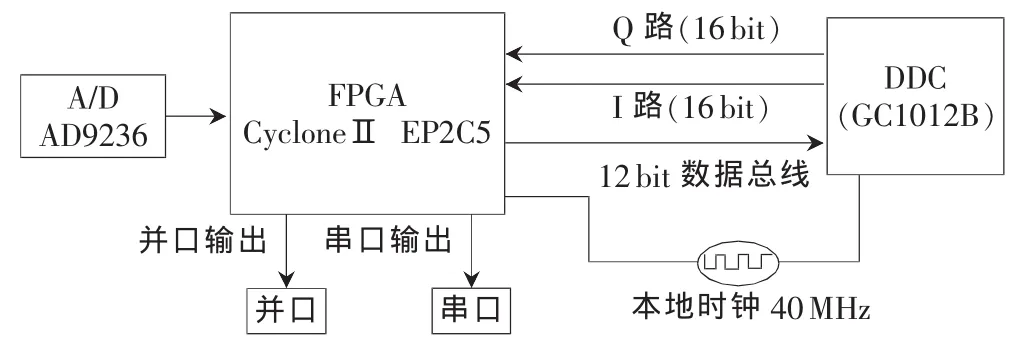

某传感器节点中频接收机以中频70 MHz、带宽10 MHz的BPSK调制信号作为处理对象,实现对中频接收信号的数字化、下变频、解调并输出。其硬件平台是A/D采样模块、数字下变频器模块、数字信号处理模块。首先是对中频信号进行数字化,这个工作由A/D转换模块来完成,方案选择的是ADI公司的A/D芯片AD9236[6-7],本系统采用Gray-Chip公司的宽带数字下变频器GC1012B对中频A/D采样后的数字信号进行下变频[8]处理,FPGA作为数字信号处理模块完成数据解调和A/D采样控制功能。本方案对数字下变频算法的FPGA实现也做了研究,这样就为FPGA单独实现下变频打下基础,使整个方案更加灵活和开放。

图1 WSN体系结构

由于传感器节点接收的信号是WSN采集节点的数据,其带宽远大于一般采集节点接收机,中频载波为70 MHz。

1.1 系统的硬件平台

某传感器节点中频接收机的硬件构成图如图2所示。

图2 传感器节点中频接收机的硬件构成图

根据软件无线电实现思想的不同,硬件平台可以有两种方案选择。

(1)如图2所示,某传感器节点中频数字化接收机分为模拟部分和数字部分。ADC模块在完成A/D变换后以12 bit的二进制补码方式并行输出。A/D采样后的数字信号由硬件实现数字下变频:数据传送到FPGA后直接送至专用芯片GC1012B,由GC1012B实现数字下变频。GC1012B完成数字下变频后的输出为I、Q两路16 bit并行数据,将I、Q路返回FPGA进行解调同步处理,再由串口输出基带信号。在调试中,每个模块输出的信号都可通过FPGA以8 bit并行方式传送数据至主机,再由主机利用MATLAB分析软件进行频谱和信号的分析。整个中频接收机由同一个晶振提供时钟,从而实现采样输出信号和数字下变频输入信号的同步。该方案相对简单实用、采样率高、运行稳定。

(2)在FPGA中用软件实现数字下变频,模拟信号经过A/D变换后的数据传送至FPGA,由FPGA实现数字下变频及解调功能,处理出来的基带信号由串口输出。

方案(2)比方案(1)复杂、采样率更低,但软件化的程度更高,通用性和灵活性更好,具有更好的前景,具有研究的价值。本文将讨论基于FPGA的数字下变频算法。

本方案的A/D模块选用ADI公司的AD9236芯片作为A/D转换模块,其外围电路用AD8138做差分信号放大器。

在DDC模块中,其主要部分是Gray-Chip公司的宽带中频数字下变频器GC1012B,能将输入频率为0~100 MHz、带宽为0~50 MHz的数字信号下变频为零中频的基带信号,在完成数字下变频后还可以通过内部的抽取器降低采样频率。GC1012B工作时由FPGA作为控制器来读写控制字。

本系统的FPGA芯片既作为控制器,又作为数字信号处理器,主机通过JTAG口把程序下载到FPGA芯片上以完成对GC1012B的控制和数据解调的功能。FPGA选用Altera公司的CycloneⅡEP2C5芯片。

1.2 模数转换模块的设计

模数转换模块主要由驱动放大器、A/D转换器和时钟电路三部分组成,此外,还可以加上RAM和抗混叠滤波器。系统选用ADI公司的AD9236转换芯片,AD9236是12 bit的单片式模数转换器,其片内含有采样保持电路。AD9236采样速率可达到105 MHz,其模拟带宽达500 MHz,它在整个工作频率范围内都具有较好的动态性能指标。AD9236模拟输入+5 V电源供电,输出为3.3 V CMOS/TTL电平,片内含基准源。为了满足其采样要求,输入的模拟信号和采样时钟采用差分输入。AD9236输出码为12 bit并行输出的二进制补码形式。

图3为系统的A/D模块的电路图。输入的中频模拟信号经过AD8138放大,在变为差分信号后传输至AD9236的差分输入端,在差分时钟的驱动下,AD9236把输入的模拟量变为数字量,并以12 bit二进制补码的形式输出。为避免互相干扰,分别用两个电源模块为时钟电路和模拟电路供电。

图3 A/D模块电路图

2 传感器节点数字下变频的FPGA实现

随着电子设计自动化(EDA)和芯片技术的发展,设计者可以大规模可编程逻辑器件为设计载体,以硬件描述语言来表达系统设计,以计算机开发系统作为FPGA/DSP系统设计的工具,自动完成数字化集成电路的设计。采用自顶向下的设计方法,即把系统高级抽象的初始功能定义分解成具体的低一级的子功能模块,分解过程一直到设计可以用简单电路实现的功能模块组成为止。

2.1 传感器节点中频接收机数字下变频的数学模型

传感器节点中频接收机中采用专用芯片GC1012B来实现数字下变频的功能,其优点是集成度高,应用方便,但是其不够灵活的缺点并不符合理想的软件无线电系统。因此,研究在FPGA中用软件的方法实现下变频是必要的。FPGA芯片具有大规模的内部逻辑阵列和丰富的连线资源,适合作数字信号处理系统。但是在FPGA中缺乏实现乘加运算的有效结构,而数字下变频算法中的乘加算法需要大量的滤波器。因此FPGA长期以来一直用于系统逻辑或时序控制中,较少有在信号处理方面的应用。

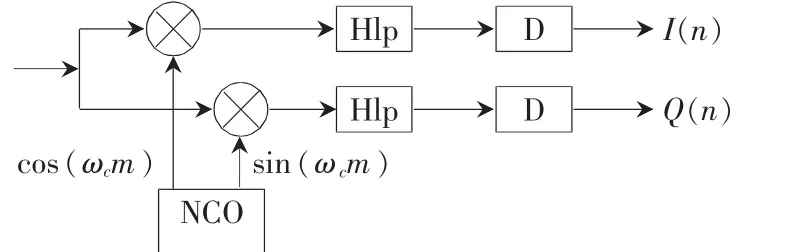

数字下变频原理图如图4所示。系统实现数字下变频的模型和上文介绍过的单通道软件无线电接收机数学模型在原理上其实是一样的,本文讨论了FPGA实现数字下变频具体的组成部分。

图5 数字下变频原理图

从图4可以看出,数字下变频(DDC)可以分为两部分:数控振荡器(NCO)受控产生本振信号 cos(ωcm)、sin(ωcm)在混频器里和输入信号相乘;低通滤波器和抽取器(D),抽取器起到降低码速率作用,可以减轻后续数据处理的压力。此外,由于需要提供本地的载波相位ωc,需要用于载波同步的数字锁相环(DPLL)从输入的信号中提取ωc。

图5 数字下变频的频谱示意图

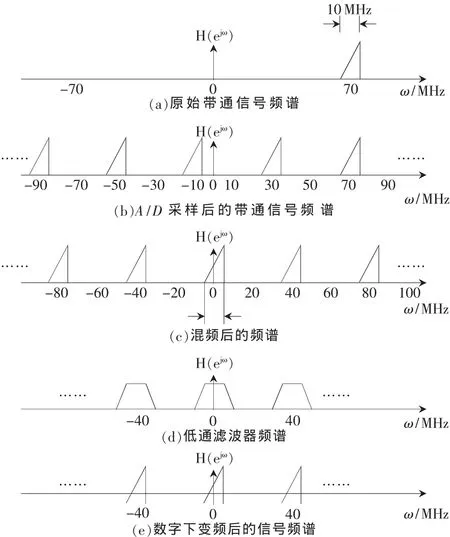

图5为数字下变频过程中信号频谱变化。假设带通信号中频为 70 MHz,带宽为 10 MHz,其频谱如图 5(a)所示,使用带通信号的解析信号即:Z(t)=x(t)+H[x(t)]画频谱,H[x(t)]是 x(t)的 Hilbert变换。通过采样频率为40 MHz的 A/D采样后,带通信号频谱如 5(b)所示,带通信号中心频率分别出现在…,-90 MHz,-70 MHz,…,30 MHz,70 MHz…,频谱以 40 MHz为周期重复出现。混频之后频谱如 5(c)所示,其中,有用的频谱被搬移到 0中频。 图 5(d)中的低通滤波器用来滤除 I(n)、Q(n)频谱分量之外的信号,这样低通滤波器的通带截止频谱应该为 I(n)和 Q(n)频谱分量中对应的最高频率,即 5 MHz,但是滤波器的阻带截止频率应小于信道间隔的一半,所以取10 MHz。在-20 MHz~20 MHz范围之内的数字下变频后的信号在-5 MHz~5 MHz上有谱线,如图5(e)所示,可见整个频谱以40 MHz为周期重复。

2.2 FPGA实现数字下变频

FPGA实现数字下变频原理图如图6所示。采样信号分成两路,一路由锁相环(costas环)提取调制信号的载波相位ωc后,再提供给数控振荡器控制产生本地余弦信号;另一路信号直接传送到乘法器,和本地余弦信号进行混频。混频后的信号经过低通滤波器滤波后,再送到抽取器以降低码速率,最后以二进制码形式输出。其算法流程图如图7所示,A/D采样后输入数据是以二进制补码的形式表示的,在经过二进制和十进制程序转换后变为整数分两路分别进行处理。其中一路在数据转换完成之后(rdyl=1)即进入混频器;另一路信号进入锁相环去提取本地载波,本地载波就是数控振荡器的输入相位。数控振荡器的输入为10 bit二进制无符号数(相位),其输出数据为二进制补码(正弦值)的查找表,即数控振荡器两端都要进行数据的转换,将转换结果送入混频器。两路数据信号rdy1和rdy2都进入判决器,如果rdy1和rdy2同时为1,则表明两路数据都准备好了,这时混频开始。

图6 FPGA数字下变频框图

在混频完成之后是滤波过程,同样,滤波器也带有rdy信号,在滤波完成后将 rdy置1,数据再被送入抽取器中,最终数据转换成8 bit二进制输出。

2.3 数字下变频算法的MATLAB仿真

系统设计中用MATLAB程序产生仿真信号源并仿真数字下变频的算法,根据输出信号的频谱来仿真算法是否能完成数字下变频的功能,系统采用BPSK调制信号来进行信号仿真[6]。

BPSK调制信号:

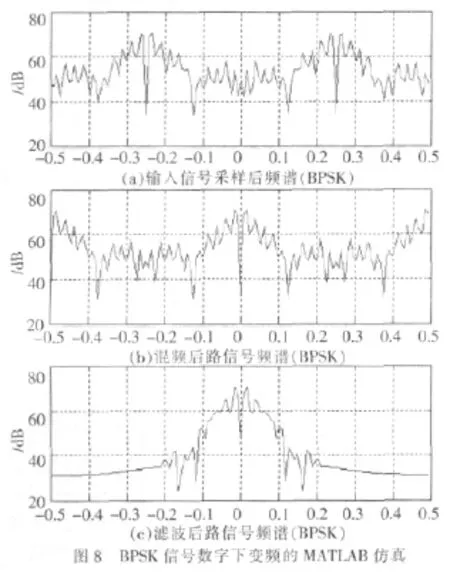

(1)输入带宽为 10 MHz,载频为 70 MHz的 BPSK调制信号,取信号幅度为128并叠加高斯白噪声,在经过采样频率为40 MHz的采样之后,信号频谱的仿真结果如图8所示,其中的横坐标经过采样频率40 MHz的归一化,所以图8中的0.5代表20 MHz,对比图 5(b),可知其中心频率是一样的均在 10 MHz、-10 MHz处。

(2)混频过程之后的信号。将BPSK调制的被采样信号与频率为10 MHz、经过40 MHz采样的余弦波混频之后,其中 I路的信号频谱仿真结果见图 8(b)所示可以看出,其频谱被搬移到了0、20 MHz、-20 MHz位置,与图5(c)相对应。由于载波信号正好是 128×cos70/40·2π·m=128×cosπ/2·m,BPSK 调制信号并与正弦信号混频后总是等于0,即Q路信号频谱为噪声与正弦信号混频后的频谱,图中即可不画了。

(3)滤波过程之后的信号。I路的混频后信号再通过5 MHz通带截止频率,阻带截止频率10 MHz的22阶的低通滤波器滤波后,信号频谱的仿真结果如图 8(c)所示,可以看到,除基带信号外的-20 MHz和20 MHz的信号已经被滤波器滤掉,这样就只剩下带宽为10 MHz基带信号,与图 5(e)相对应。

可以看出,BPSK调制信号数字下变频的信号频谱变化过程都与图5一样,说明数字下变频算法的设计符合前面的数学模型,可以正确完成信号数字下变频的功能。

本文中的传感器节点中频接收机是为了满足区域侦查通信的需要,工作在2.4 GHz自由频段,中频工作在70 MHz,数据采用RS编码和BPSK调制方式。在实验室环境中,对本文设计的传感器节点中频接收机的功能进行验证,结果表明,该接收机能够实现对载波频率的快速跟踪和锁定,对于码速率不大于2 Mb/s,信号强度动态范围在-8 dBm~+16 dBm范围内的信号,可以实现误码率接近理想BER曲线(实际测量曲线偏离理想曲线3 dB以内)的解码。因此,该传感器节点中频接收机满足设计指标。

[1]杨小牛,楼才义,徐建良.软件无线电原理与应用[M].北京:电子工业出版社,2001.

[2]BAESE U M.数字信号处理的 FPGA实现[M].刘凌,胡永生,等译.北京:清华大学出版社,2003.

[3]郑继禹,林基明.同步理论与技术[M].北京:电子工业出版社,2003.

[4]黄英,李景文,刘敏.软件无线电技术在传感器节点中频接收机中的应用[J].无线电,2004,30:18-20.

[5]毕占坤,吴伶锡.FIR数字滤波器分布式算法的原理及FPGA 实现[J].电子技术应用,2004,30(7):61-62,66.

[6]BURACCHINIE.The software radio concept[J].IEEE Communication Magazing,2000,38(9):138-143.

[7]AnalogDevices.AD9236 data, 12-bit, 80 MSPS/105 MSPSanalog A/D Converter[Z].2002.

[8]Texas Instruments.GC1012B data,3.3 V digital turner chip[Z].2002.

[9]陈怀深.MAILAB及其在理工课程中的应用指南 [M].西安:西安电子科技大学出版社,2000.