基于权值调整的FLL 辅助PLL 方法

2012-10-21杨霞玉孙延鹏

李 然,杨霞玉,孙延鹏

(1.西安航天复合材料研究所,西安 710025;2.沈阳航空航天大学 电子信息工程学院,沈阳 110136)

锁相环的发展方向是提高工作频率,采用微处理器件和微电子技术,发展新型序列滤波器,提高抗噪声能力,加快捕捉,减少输出相位抖动[1]。为了保证动态跟踪性能,锁相环必须具有相对宽的带宽,而带宽的增加会导致信噪比降低,因此在锁相环路中动态性能和高信噪比是一对矛盾。如何兼顾动态跟踪性能和高的信噪比,是锁相环设计中的难点。FLL 有较高的动态性能,也就是其捕获带宽范围较大,而PLL 的鉴别精度较高(即高信噪比),将两者结合,可以达到功能互补的作用。在保证PLL 高精度的条件下,可以利用FLL的高动态性能加大整个环路的捕获范围。本文兼顾两者的优点采用了基于权值调整的FLL 辅助PLL 的方法。FLL 辅助PLL 的方法有多种,比如FLL 牵引PLL 的辅助方法(FLL/PLL)、FLL 与PLL(FLL&PLL)的辅助方法,文中对以上两种方法的特点进行了分析得出其优缺点,在此基础上设计了基于权值调整的FLL 辅助PLL(FPLL)的方法,得出基于权值FLL 辅助PLL 方法的优点。

1 PLL(锁相环)与FLL(锁频环)的原理

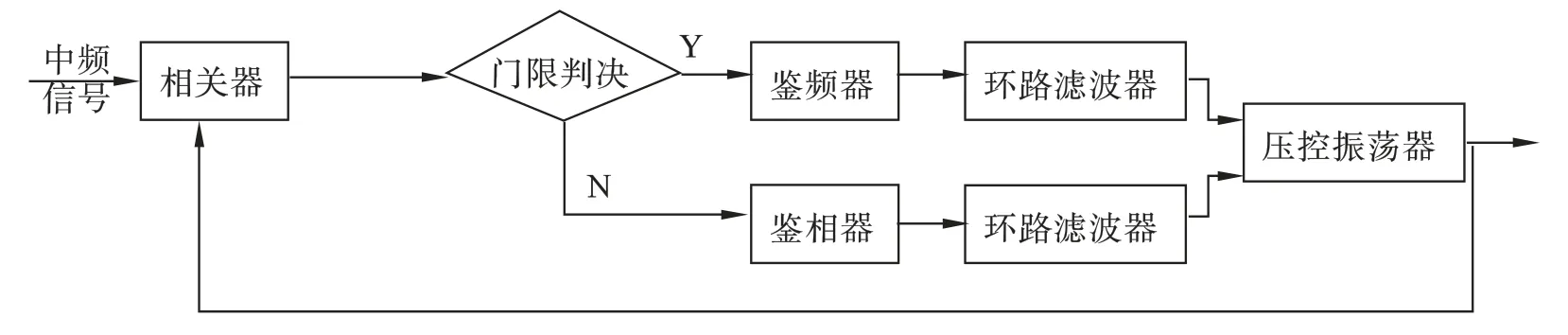

锁相环路是一个闭环的相位负反馈控制系统,主要由三个基本部分组成,如鉴相器(PD)、环路滤波器(LF)和压控振荡器(VCO)。其原理如图1 所示。

图1 锁相环原理框图

当工作时,压控振荡器的输出信号反馈到鉴相器,在鉴相器中输出信号θ2(t)与环路输入信号θ1(t)进行鉴相,在经过环路低通滤波器之后含高频部分的信号被滤除掉,剩的下直流信号进入VCO,通过电压的高低控制其输出信号频率的大小,若θ2(t)变化速率低于θ1(t)的变化速率,说明VCO 输出信号的频率低于环路输入信号的频率,鉴相器将产生一个正压信号,使得VCO 的输出信号频率升高一点。反之,将产生负压信号VCO 输出信号频率降低,经过一段时间后反馈系统最终将达到一个平衡,即VCO 输出信号的相位θ2(t)与环路输入信号的相位θ1(t)变化速率达到相同,即两者的频率也就达到相同,即是环路达到“锁定”的状态[2]。

2 FLL 与PLL 的特点

锁频环跟踪的是载波的频率,高动态环境下,同阶的锁频环与锁相环相比,它的跟踪性能要好一个数量级,因此具有较好的动态性能,但是在稳态时FLL 的跟踪精度却比PLL 跟踪精度低。锁相环跟踪的是载波的相位,在低动态或者稳态的环境下具有比较高的跟踪精度和比较好的噪声性能。但它对环路的动态容忍度比较差,当在高动态环境下时,PLL 基本上很难同时满足跟踪精度与动态性能的要求[3]。可见,FLL 和PLL 在噪声性能与动态性能上具有互补的特性[4]。

3 FLL/PLL 与FLL&PLL 的原理及特点

3.1 FLL 牵引PLL 的辅助(FLL/PLL)方法的原理及其特点

图2 FLL 牵引PLL 辅助方法框图(FLL/PLL)

如图2 所示为FLL/PLL 的载波跟踪原理图。当输入的本地信号与压控振荡器反馈回来的信号进行相关后进行门限判决,若频偏值小于门限值时,则环路进入PLL 工作状态,反之进入FLL 工作状态,但在同一时刻环路只能处于一种工作状态。当处于高动态的状态下时,初始频偏会比较大,环路会切换到FLL 的工作状态下,在此工作状态下环路的误差信号不断的调整压控振荡器输出信号的频率,使得频偏越来越小,当频偏小于门限值时,环路切换到PLL 工作状态。所以FLL/PLL 方法既保证了跟踪环路的动态性能,又保证了跟踪环路的跟踪精度。

尽管FLL/PLL 方法在一定程度上结合了FLL 和PLL 的优点,但是在环路进行切换时,会造成滤波值的不连续,特别当两者在进行频繁的切换时,会使产生的误差会很大,最终导致失锁。

3.2 FLL&PLL 方法的原理及其特点

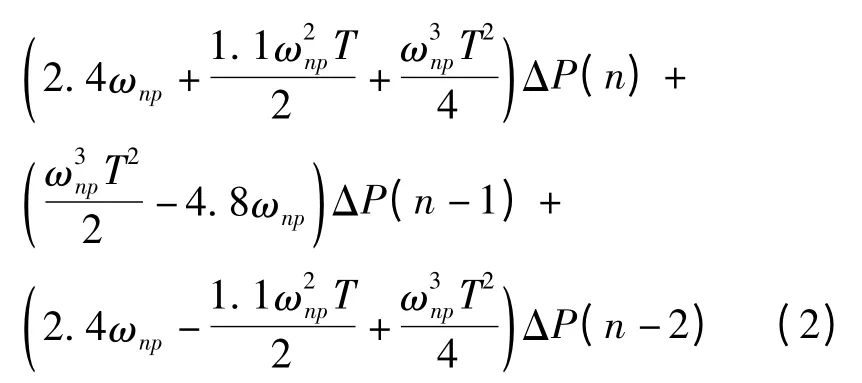

FLL&PLL 的原理图如图3 所示,与图2 FLL/PLL 的设计相比较,在此环路中,以PLL 为主,以FLL 做为辅助:

FLL 辅助项[5]:

则FLL 辅助PLL 跟踪环路的最终输出为:

其中,AFLL为FLL 环路的输出值,yPLL为PLL 环路的输出值,y 为整个环路的输出值,Δf 为鉴频器输出,ΔP 为鉴相器输出,ωnp、ωnf分别为FLL 和PLL环路滤波器参数,T 为计算单元,在本文中为1 ms。

该方法过于生硬,对环境的适应性不强,无法根据信号的动态性进行调整。

图3 FLL&PLL 环路

4 基于权值调整的FLL 辅助PLL 方法的设计

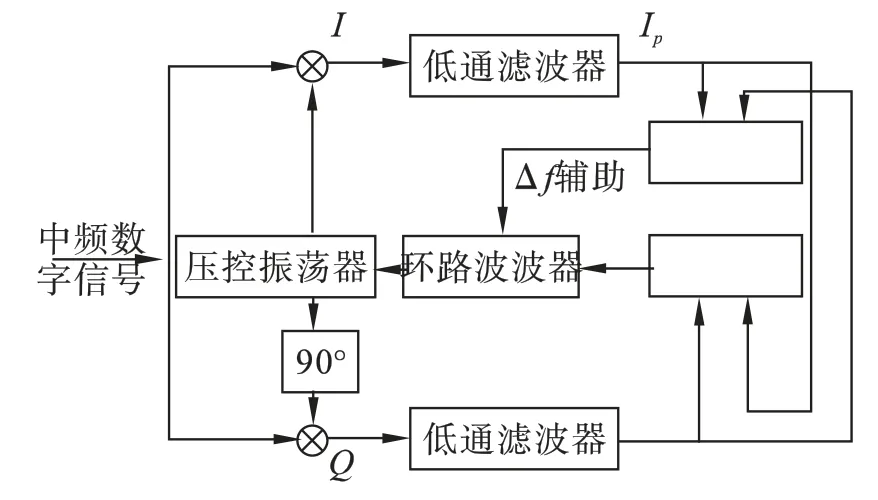

基于以上两种方法的缺陷本文提出一种基于权值调整的FLL 与PLL 相融合的跟踪方法(即FPLL 方法)。FPLL 示意图如图4 所示:

图4 基于权值调整的FLL 融合PLL 方法(FPLL)

4.1 判决因子的选择

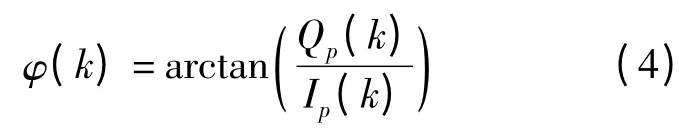

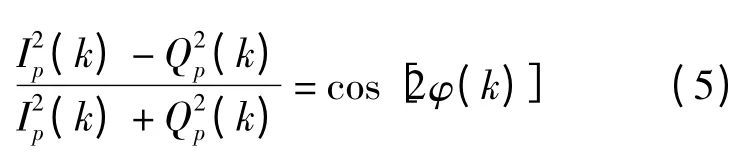

由于PLL 的鉴相器采用的是反正切型,因此[6]

又[6]

当相位锁定时,有φ(k)→0,cos[2φ(k)]→1,可以选取

作为判决因子。以上是式子中:φ(k)相差,Qp(k)为正交输入信号,Ip(k)为同相输入信号。

4.2 具体算法

(1)鉴频器输出[7]

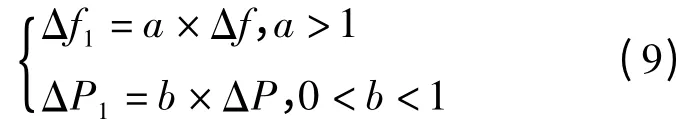

(2)当门限值大于判决因子P(k)时,相位偏差大,载波频率的变化率较高,使FLL 的作用强化,使PLL 的作用弱化

所以赋予权值为[7]:

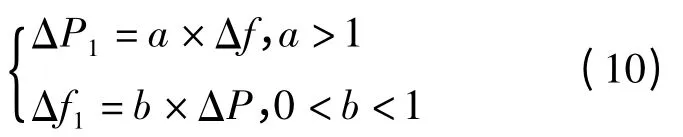

反之当门限值小于判决决因子P(k)时,相位偏差小,载波频率变化率比较低,因此使PLL 的作用强化,使FLL 的作用弱化所以赋予权值为[7]:

式(9)、(10)中a、b 表示相关系数,Δf1表示经过权值调整获得频差,ΔP1表示经过处理权值处理后的相差。

(3)将赋予权值之后的Δf1和ΔP1在同一滤波器中相融合,得到最终的滤波输出。根据滤波器输出值相应地调整DCO 频率,保持对信号的跟踪锁定。在FPLL 算法中,每一个计算单元内,FLL 和PLL 都会进入运算,只是它们的相对作用大小会根据当前的跟踪状态进行调整,这样既能融合FLL 与PLL 的优点,又能有效避免一般的环路切换方法中出现的滤波值不连续的情况[8]。

4.3 部分重点模块的VHDL 关键代码及波形仿真

用VHDL 语言对整个电路进行了设计,部分重点模块的相关代码及生成模块如下。

(1)用于门限判决部分关键代码及生成模块

模块中的a 表示从相关器中输出来的相位差,clk 表示时钟信号,b 表示门限判决中的参考信号可根据实际需要来设置,dout 为输出信号。当信号a 大于参考信号b 时dout 输出的是高电平,否则输出的是低电平。关键代码及相关功能仿真(见图5)如下所示。

关键代码:

门限判决功能仿真图:

图5 门限判决的功能仿真

由门限判决的功能仿真结果可以看出此模块能够很好地进行门限判定。

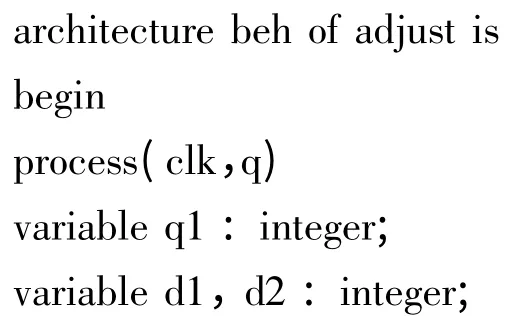

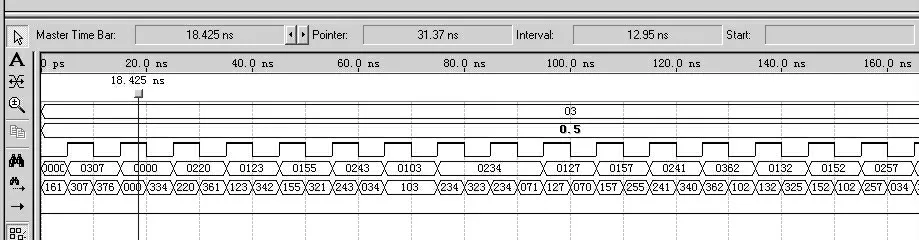

(2)用于权值调整的部分关键代码及生成仿真

clk 为时钟信号,q 为从门限判决传输过来的信号,c1 为大于1 的系数,c2 为小于1 的系数,phase 为相关器传过来的相位差,当q 为高电平时,用c1 乘以phase 起强化作用,反之为c2 乘以phase 起弱化作用。关键代码及相关功能仿真图(见图6)如下所示。

关键代码:

权值调整功能仿真图:

图6 权值调整的功能仿真图

由权值调整的功能仿真结果可以看出此模块能够很好地进行权值调整。

5 仿真结论

在同一动态条件下分别对三种方法进行了相应的实验仿真,实验中的数据来源于SPIRENT8000 系列模拟器所产生的动态信号。以下是FLL 牵引PLL(FLL/PLL),FLL 辅助PLL(FLL&PLL)以及基于权值调整的FLL 融合PLL的方法(FPLL)所进行的试验仿真结果。在加速度为80g,PLL 带宽为10Hz,FLL 带宽为10Hz 的条件下所跟踪的结果如图7 所示。

图7 PLL 与PLL 带宽为10Hz

由图可以看出在此高动态条件下FLL/PLL的失真最为严重,FLL&PLL 次之,PFLL 的效果最好,且在图中可以看见0 到500 ms的时间段内FLL/PLL 跟踪的波值不连续,FLL&PLL 次之,但在跟踪时过于生硬达到不失真跟踪状态的时间较长。

因此,在高动态条件下,FPLL 方法在跟踪时不但能保持波值的连续,不会造成失真,而且在由FLL 切换到PLL 环路的过程中也不生硬,捕获跟踪信号的速度快,能保持性能稳定。所以FPLL方法更能有效地应用于高动态载波信号环境中。

(References):

[1]邹亮.锁相环技术发展的研究及应用[J].科技资讯,2009(35):147.

[2]RolandE.Best.锁相环设计仿真与应用[M].李永明,译.北京:清华大学出版社,2007.

[3]张建斌.锁相与频率合成[M].北京:科学出版社,2011.32.

[4]姜毅.GNSS 接收机高性能跟踪与捕获环路算法研究[D].大连:大连海事大学,2010.

[5]M.Anghileri,An Algorithm for bit synchronization and signal tracking in software GMSS receivers[A].ION-GPS[C].2009.5.

[6]Jun Ma,Mike Li,Mark Marlett.A new measurement and analysis for a third order phase locked loop(PLL)transfer function[C].International Test Conference,2005:l-10.

[7]Sung-Hyuck Im.Comparison of GPS tracking loop performance in high dynamic condition with nonlinear filtering techniques[A].ION-GPS[C].2011.

[8]孔祥晖.高阶窄带锁相环技术研究[D].哈尔滨:哈尔滨工程大学,2008.