基于DSP的微型实验系统

2012-10-18李慧慧范文兵

李慧慧,范文兵

(1.河南广播电视大学;2.郑州大学,河南 郑州 450000)

一、DSP芯片的选型

数字信号处理器(DSP)是电子信息领域的新型高科技产品,已成为传统微控制单元和昂贵的多片MCU设计的一种廉价替代品。TMS320C54x系列是隶属于TMS320家族的定点数字信号处理芯片,具有低功耗、高性能等优点,广泛应用于传真、个人通信和语音编码等无线通信系统中。考虑到系统设计的通用性和性价比,该实验系统选择TMS320VC5410(简称VC5410)作为处理器芯片。本文主要介绍基于VC5410的微型实验系统硬件电路各模块设计方案及在软件调试过程中遇到的若干问题及其解决方案。

二、系统模块

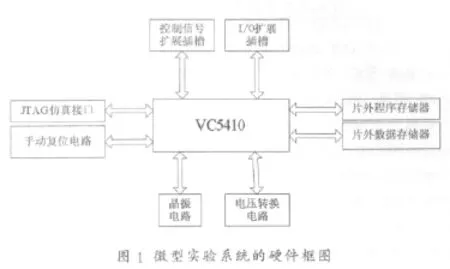

微型实验系统主要为满足DSP教学常规实验而开发的。该系统以VC5410芯片为核心,外围电路由时钟电路、电源电路、复位电路和片外程序/数据存储器等部分构成。实验系统硬件框图如图1所示。在设计中选用了以下芯片:

处理器芯片VC5410:具有3.3VI/O电压和2.5V核电压。

电压转换芯片TPS73HD325:主要为实验系统提供稳定的+3.3V和+2.5V电源。

存储芯片SST39VF400(VF400):系统中的FLASH芯片,用于存放BOOT表和提供外扩的存储空间。

外部 RAM芯片 IDT71V016SA15PH:64K×16bit的高速SRAM,主要用来存储大量数据。

1.时钟电路设计。

DSP系统中,时钟电路占有至关重要的地位,其性能好坏直接影响到系统能否正常运行。时钟电路设计原则如下:

(1)系统中要求多个不同频率的时钟信号时,首选可编程时钟芯片,这样有利于时钟信号的同步。

(2)单一时钟信号时,一般的应用建议选择晶体时钟电路。

(3)多个同频时钟信号时,可选择有源的晶振作为时钟电路。

(4)尽量使用DSP片内的PLL,降低片外时钟频率,提高系统的稳定性。

(5)C6000、C5510、C5409A、C5416、C5420、C5421 和 C5441等DSP片内无振荡电路,不能用晶体时钟电路。

(6)VC5401、VC5402、VC5409 和 F281x 等 DSP 时钟信号的电平为1.8V,建议采用晶体时钟电路。

依据以上设计原则,在笔者设计的微型实验系统中,采用的是晶振电路,它与内部振荡器一起产生参考时钟信号。其电路简单、体积小、频率范围宽(1Hz~400MHz)、驱动能力强,可为多个器件使用。系统中所使用晶振的频率为10MHz,经DSP倍频后工作频率可以达到100MHz。需要注意的是,在使用晶振时,输出信号电平一般为5V或3.3V。VC5410的CPU有三个时钟模式选择引脚CLKMD1、CLKMD2、CLKMD3,为了操作方便,可将这三个引脚的值由DIP开关控制,这样增强了时钟晶振选择的灵活性。

2.电源电路设计。

直流稳压电源供电为标准的5V直流电,而VC5410要求3.3V的I/O电压和2.5V核电压,因此必须进行电压转换。常用的电源解决方案有以下两种:(1)单电源输出;(2)双电源输出。在该系统设计中由于采用的是双电源输出方案,选用TPS73HD325作为电压转换器,典型输入电压为+5V,输出为3.3V和2.5V,设计原理图略。

3.复位电路设计。

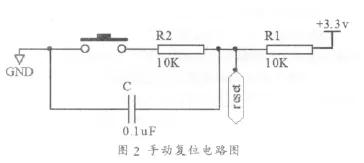

对于TMS320C54x而言,复位是不可屏蔽的外部中断,也是优先级别最高的中断。一般在加电后芯片处于未知状态时对其复位。每次复位后系统重新运行初始化程序。根据对复位源的不同操作,TMS320C54x的复位方式可分为三种,即上电复位、手动复位和软件复位。前两种是通过硬件电路来实现复位,后一种则通过软件编程实现。上电复位即复位引脚RS产生一个低电平脉冲信号,使芯片复位。芯片完成对硬件的初始化并从0000H单元开始执行第一条指令,通常这里是一条分支到系统初始化程序的跳转指令。为使芯片初始化正确,一般应保证复位端(RS)低电平至少持续6个时钟周期,即当时钟为20MHz时为300ns。在该微型实验系统设计中,为了调试电路方便,特意在电路板设置手动复位键(如图2)。手动复位时,SW1按钮按下,以后过程同上电复位过程是一样的。

4.JTAG接口设计。

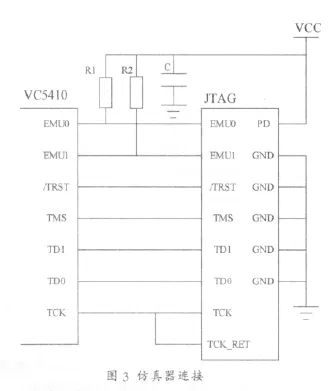

VC5410含有一个专用仿真口来支持由IEEE1149.1标准规范的JTAG仿真,该端口由仿真器直接访问,以实现在线仿真、程序下载等软件调试,它可实时地访问目标板上CPU的存储器、寄存器以及I/O口等内容。当仿真头和JTAG目标芯片之间的距离超过6英寸时,仿真信号需要缓冲,若小于6英寸,不必加缓冲。图3是一个不加缓冲的仿真器连接图,也即是实验系统中的连接方案,其中的EMU0和EMU1信号必须通过上拉电阻连接高电平,提供少于10us的信号上升时间,推荐的上拉电阻为4.7或10。

5.存储器扩展设计。

VC5410片上具有 16KW 的 ROM,8KW 的 DARAM,56KW的SARAM,但在需要大容量存储器时,就需进行片外扩展。片外存储器的扩展有多种方式,程序存储器和数据存储器可以分开设计,也可以混合设计。为了不增加系统设计的复杂度,提高存储器利用率和可扩展性,微型实验系统中,存储器的扩展方式为:FLASH用作程序存储器,SRAM用作数据存储器。

(1)该系统设计中采用VF400作为FLASH,用于存放BOOT表和提供外扩的存储空间;该芯片是一个低功耗FLASH,工作在2.7~3.6V下,存储容量为256KW (1KW=16bit),可重复编程次数达10万次。VF400在读模式时,/CE和/OE是逻辑低电平,并且/WE是逻辑高电平;在编程/擦除模式时,/CE和/WE是逻辑低电平,而/OE是逻辑高电平。

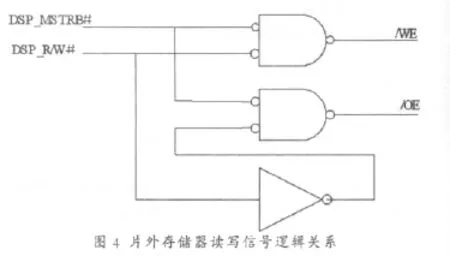

(2)该系统设计中,VC5410工作在100MIPS下,所以外部RAM可以考虑选择15ns的IDT71V016SA15PH。设计中将DSP设置为微机工作方式 (MP/MC=0),8000~0BFFFh映射到外部存储器上,故而SRAM的地址线A15必须逻辑置1。FLASH和SRAM的读写信号逻辑关系如图4所示。

其中,DSP_MSTRB#、DSP_R/W#为 VC5410的/MSTRB和R/W管脚,/WE、/OE同时用作FLASH和 SRAM的/WE、/OE 逻 辑 ,VC5410 的/PS+DSP_MSTRB#、/DS+DSP_MSTRB#逻辑分别用于FLASH和SRAM的/CE、/CS逻辑。

/WE=DSP_MSTRB#+DSP_R/W#;

/OE=DSP_MSTRB#+! DSP_R/W#;

/CE=/PS+DSP_MSTRB#;

/CS=/DS+DSP_MSTRB#。

三、抗干扰设计

1.电源和地的抗干扰设计。

电路板设计中,无论是否有专门的地层和电源层,都必须在电源和地之间加上足够的并且分布合理的电容。一般在电源和地的接入端放一部分多种容值的电容,再将其余的大电容均匀地分布在电源和地的主干线上。可以在电源入口处接一个大容量的电解电容或钽电容,一般10-100uF都可以,滤去低频噪声。另外,还应该并联一些小容量的高频电容,一般在0.01-0.1pF范围内都可以,它们的值可以不同,以分别滤去不同频率的高频噪声。

2.重要信号线设计。

时钟信号频率越高,其布线要求也就越高。本系统设计中采用的是10MHz的晶体振荡器,布线时应该注意如下几点:

(1)时钟源和负载的连线应尽量短,线应较宽。

(2)在时钟芯片的电源入口处放一个容量为10~100uF的钽电容,具体可根据实际情况而定,为了防止高频干扰,还应在大容量电容后并联一个0.1uF的小电容。

(3)不要在时钟芯片的下面布线,以防时钟芯片的输出产生抖动。对于时钟走线而言,最好都从内层走,以减少干扰。

四、系统调试

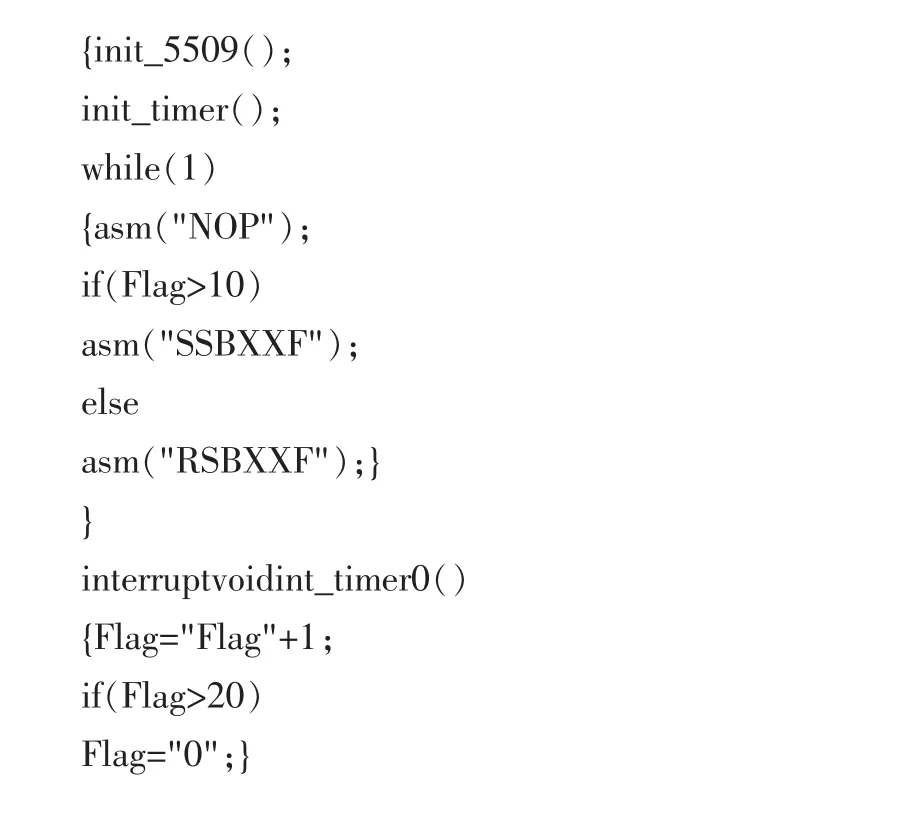

处理器芯片VC5410的四个外部中断引脚READY、/BIO、/NMI、/HOLD需通过4.7的上拉电阻接高电平。在对系统上电前要仔细检查元件是否可靠地焊牢,管脚间、电源和地之间是否短路,元器件、电容的安装方向是否正确。上电后,要先检查10MHz的晶振是否正常工作,能否硬件复位。上电后可用示波器测量DSP的时钟输入和时钟输出波形。通常情况下,DSP内部可以对不满意的时钟进行整形,因此,只要输出时钟CLKOUT波形合格,就说明时钟正常工作。如果仿真器不能启动,原因可能是多方面的,具体可以参阅相应的仿真器说明手册。如果设计成功,接上电源后能够顺利进入系统仿真环境。可编写一段控制XF管脚的测试程序,观察到XF管脚上拉的发光管闪烁,也可以用示波器直接测试波形。部分测试程序代码如下。

五、结束语

基于DSP的微型实验系统充分利用了数字信号处理功能,采用最简洁可靠的硬件电路形式来满足数字信号处理教学的基本要求。本系统具有良好的通用性和开放性,也可以直接作为一个多功能的DSP研发和调试平台,以方便进行功能的扩展和二次开发,具有广阔的前景。

[1]刘佳,张奕黄.TMS320LF2407 的复位问题分析[J].微特电机,2004(7):46-47.

[2]张勇.TMS320C5000系列 DSP汇编语言程序设计[M].西安:西安电子科技大学出版社,2004:80-108.

[3]孙光,赵志敏.数字信号处理器TMS320F206复位问题研究[J].电子技术应用,2002(11):67-69.

[4]王立华,刘志军.DSP 系统中时钟电路的设计[J].电子世界,2005(5):29-30.

[5]王丽娟,赵恒,甄姬娜.McBSP及其在实际中的应用[J].微计算机信息,2007,23(29):146-147.