FM IBOC数字广播系统中交织器的FPGA实现

2012-09-20薛腾万欣倪暄王威

薛腾,万欣,倪暄,王威

(1.中国传媒大学信息工程学院,北京100024;2.中国传媒大学广播电视数字化工程中心,北京100024)

1 引言

带内同频IBOC(In Band On Channel)数字广播标准是美国基于高清晰无线电系统的数字AM、FM广播技术标准[1]。IBOC最大的优点在于无需新的频率分配,允许广播信号由模拟信号向数字信号过渡,它在不影响现有模拟广播的前提下,通过现有模拟广播的频谱提供高清晰度的数字声音广播与数据业务。这样就可以实现在使用数字信号时不需大量更换设备,对原来的模拟信号进行兼容。FM IBOC是在1992年的国际会议上,以IBOC(In Band on Channel-带内同频道)的名称公诸于世的,现在已有多个国家和地区使用[2]。

IBOC系统中的多数模块都容易实现,只是交织器部分比较难,主要原因是,数学公式较多,不易用数字芯片直接实现,其次交织数据量太大,每一帧发射数据量多达368640bit[3],实现这个系统要考虑内存,处理速度,时延[4]等一系列问题。本论文对其中最典型的模块(MP1、MP2、MP3 和 MP11[5]的 PM交织器)进行分析。

由于在FM IBOC(In Band On Channel)数字广播系统的交织器的参数有规律性,利用这些这种规律,不再直接用数字芯片实现系统中的数学公式,而是用数字芯片去实现仿真后的有规律的数据,这样将大大降低设计交织器的难度。

2 FM IBOC系统交织器的参数计算

交织器Ⅰ:

间隔的计算:

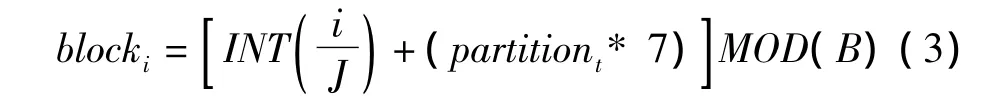

数据块的计算:

如果M=1:

如果M=2或者4:

行和列的计算:

其中

交织器II:

间隔的计算:

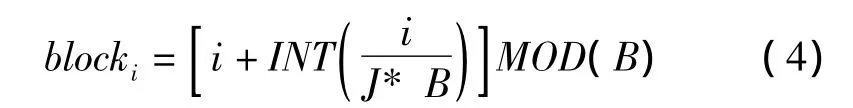

块的计算:

行和列的计算:

3 仿真结果及硬件实现分析

该交织方式使用交织器Ⅰ和交织器Ⅱ[6],利用交织器I对P1G信号交织处理,经过仿真得知:P1G一帧数据365440bit被分配到320个数据块中,每个数据块有1142bit,而每个数据块能存储1152bit,剩余的10个数据由PIDSG进行填充,320个数据块一共剩余了3200个未填单元,恰好被16个每一帧为200bit的PIDSG信号填充。下面是详细交织过程:

对于P1G:

A、20个数据一组分别分配到每一个间隔指定的数据块中的第0行第0列。

B、下一组的20个数据像A一样,分配到每一个间隔的下一个数据块中的第0行第0列(间隔不变、数据块序号加1,行、列不变)。

C、经过16次数据分配,则每一个间隔中的所有数据块都循环一遍,都存储在每一个数据块中的第0行第0列。一共存储了320个数据。随后320个数据存储时:(行+11)%32,(列+11)%36,一共循环了288次,交织处理了92160个数据。

D、经过288次(A、B、C)循环,每一个数据块中都存储288个数据,此时(间隔10、块6,行0、列0)地址循环到了初始值,寻址不加修改,第 2组92160bit将会覆盖前面的92160bit,这是不应该的,由于在每个块中有32行36列,列多4,所以间隔、数据块、行不变,列+1。

E、又经过288次循环,存储92160bit,初始列地址再加1,一共修改了4次,最后一次循环了278次,存储了88960bit,此时,P1G的365 440bit存储完毕,每个数据块中存储了1142bit,但是一个块容量是32*36=1152个数据,剩余的10bit用来存储PIDSG信号。

对于PIDSG:

A、每一帧共有3200bit,20bit一组,先存储在每一个间隔第0块中的指定位置。

B、下一组数据(20个)存储在每一个间隔第0块中的下一个指定位置。一共循环了10次,存储了200bit。

C、像前面320bit数据存储方法一样,只是块地址加1。经过16次循环,一共存储3200bit,每个数据块中都有10bit,不同数据块中的数据存储的行列地址是相同的。这样3200个数据存储完毕。

所有P1G信号存储完毕后,剩余的由PIDSG中的10bit进行填充,依次填充(18,1)、(29,12)、(8,23)、(19,34)、(30,9)、(9,20)、(20,31)、(31,6)、(10,17)、(21,28)。到此,交织完毕,PM 矩阵已被填充满,可以做下一步的子载波映射。

4 应用硬件对FM IBOC系统的交织器进行设计

有了以上的仿真结果,就可以把数学公式的直接硬件实现改为对数学仿真结果的实现,对于实现除法、乘法、求余公式比较难的FPGA芯片[7]来说,这样更容易实现。

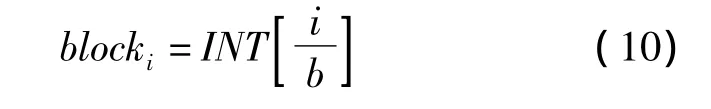

对于硬件实现,采用的是altera公司的CycloneII芯片[8],在系统中主要是对 P1G和 PIDSG信号进行交织,整个系统分为两个部分,一个对P1G信号用交织器Ⅰ进行交织,另一个部分对PIDSG信号用交织器II进行交织,系统的框图如图1:

图1 FM IBOC系统交织器MP1、MP2、MP3和MP11服务模式

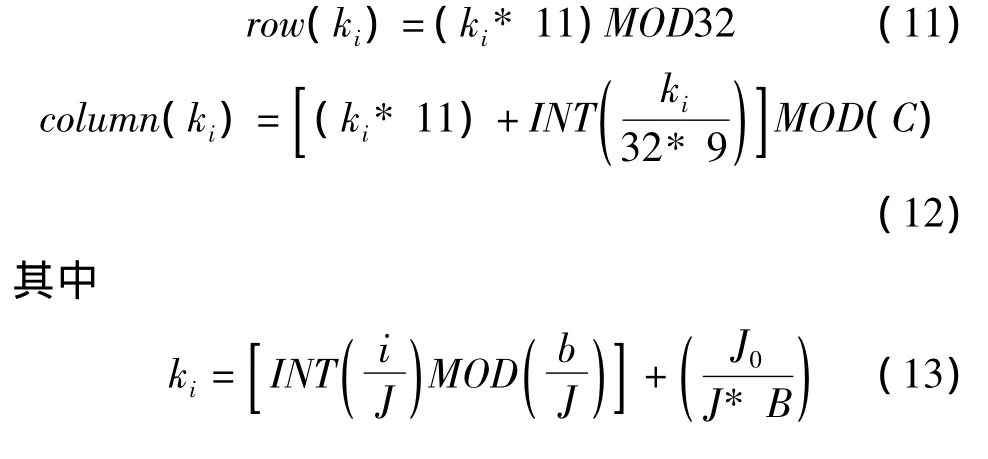

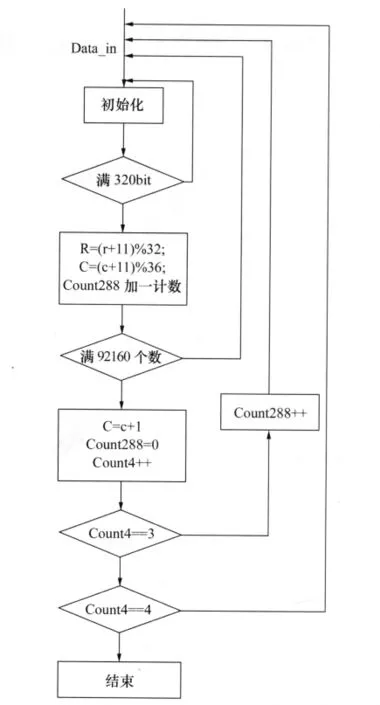

用FPGA芯片实现P1G信号的编码时主要有四个参数:Partition(编码后该bit值所在的间隔数),block(编码后该bit值所在的块数),r(编码后该bit值所在数据块的行数),c(编码后该bit值所在块的列数)。其中有对32和36求余的模块,可以利用数字芯片的方便的求余算法,对32求余,可以直接取该数值的第五位。在该模块中,数据比较多,每一帧有365440个数据,任务比较繁杂,但是经过简化,采用状态机、计数器和查找表的方式。整个过程也很容易实现。在流程图的初始化模块中,初始值为:R=18;C=1;B=0;Partition=10。Count288是计数器,每处理320bit,Count288就加一,Count4也是计数器,每处理92160bit就加一。Partition是间隔矩阵的索引值,B是数据块的索引值。下图中的结束方框是指该帧数据的处理结束,结束后开始进行下一帧数据的交织。

用FPGA芯片对P1G信号进行交织流程图如图2:

图2 P1G信号交织流程图

用FPGA芯片实现PIDSG的编码参数和实现P1G的编码参数基本相同。但是相对于对P1G的编码,对PIDSG的编码更简单,流程更清晰,数据更少,每一帧只有3200bit,处理更加容易。同处理P1G信号一样,在流程图中的结束方框是指该帧数据的交织结束,结束后开始进行下一帧数据的交织。用FPGA芯片对PIDSG信号进行交织的流程图如图3:

5 结论

通过以上的研究可以看到,对于FM IBOC系统中的数学公式,原来用硬件直接实现比较困难,甚至是不可能实现的。现在在仿真数据的规律的基础上,用硬件直接对其结果实现,很容易实现该系统的交织器。在其他的模块中我们也采用同样的方法避开系统中复杂的数学理论公式,可以起到事半功倍的效果。

图3 PIDSG信号交织流程图

[1] 邹峰,蔡干伟,谈黎红.数字音频广播技术现状及发展趋势[J].广播与电视技术,1999,(1):40~49 2001 12 33-44.

[2] 何晶莹.调幅广播的新技术革命与世界数字广播[J].广播与电视技术,2002 4 53-65.

[3] iBiquity Digital Corporation.HD Radio FM Transmission System Specifications,Doc.No.SY_SSS_1026s,Revision E[Z].

[4] iBiquity Digital Corporation.HD Radio Air Interface Design Description-Audio Transport,Doc.No.SY_IDD_1017s,Revision E[Z].

[5] iBiquity Digital Corporation.HD Radio Air Interface Design Description-Layer 1 FM,Doc.No.SY_IDD_1011s,Revision F[Z].

[6] iBiquity Digital Corporation.HD Radio Air Interface Design Description-Station Information Service,Doc.No.SY_IDD_1020s,Revision G[Z].

[7] 王小军.VHDL简明教程[M].北京:清华大学出版社,1997.

[8] Altera.Version2.0.Datasheet:SOPC Builder.2002.