布线约束下的低功耗扫描测试

2012-09-17刘文松

黄 宁 朱 恩 刘文松 林 叶

(东南大学射频与光电集成电路研究所,南京 210096)

布线约束下的低功耗扫描测试

黄 宁 朱 恩 刘文松 林 叶

(东南大学射频与光电集成电路研究所,南京 210096)

分析了扫描测试过程中功耗产生的原因,研究了扫描触发器跳变对内部组合逻辑锥的影响,并对其进行建模,将计算得到的影响函数值作为扫描链重排序的依据.然后,基于扫描链结构的特殊性,分析了布线约束对扫描链重新排序的影响,并将布线约束简化,提出了一种同时兼顾低功耗和布线约束的算法.该算法不需要迭代,通过一次运行即可得到扫描链重排序的结果,在保证后端设计可行性的前提下,尽可能减少了高影响值扫描单元上的跳变次数,实现了对扫描测试功耗的优化.基于电路测试算例以及ISCAS89基准电路集中的电路s298和s5378,进行了仿真实验,结果表明:所提算法可以使扫描测试功耗降低12%,对故障覆盖率以及测试时间没有任何影响,而且不需要任何硬件开销,可应用于芯片的量产测试.

扫描链;逻辑锥;低功耗;布线约束;重排序

如何实现低功耗扫描测试是目前芯片设计领域面临的诸多挑战之一.测试电路的增加、测试向量之间较小的相关性以及并行测试的采用,使芯片在测试模式下的功耗较正常工作模式时高出一倍左右.功耗过高会导致芯片因测试而损坏,芯片良率降低,封装成本随之增加.

基于扫描的测试是目前业内最为常用的DFT(design for test)方法.扫描测试时扫描链上各扫描单元频繁跳变,导致测试功耗较高.介于测试成本的考虑,仅通过减小时钟频率来降低测试功耗变得不再可行.近年来,国内外学者提出了多种方法以实现低功耗扫描测试,例如调整扫描时钟架构[1-2]、设计特殊扫描单元[3-5]以及在RTL(register transfer level)阶段调整代码[6-7]等.然而,这些方法都存在缺陷:调整扫描时钟架构虽能降低功耗,但也会增加测试时间;对特殊扫描单元的设计虽能解决扫描单元频繁跳变的问题,但因每个扫描单元面积增加而引入的硬件开销也是相当可观的;介于电路的性能和知识产权的限制,改变被测电路RTL的方法不易施行和推广.文献[8]给出了一种扫描链重排序的方法,可以在不增加硬件成本及测试时间的前提下降低测试功耗,但是没有兼顾后端实现,且算法相对比较复杂.本文通过研究扫描单元的跳变对电路内部组合逻辑锥的影响并对其进行建模,提出了一种布线约束下的扫描链重排序算法.实验结果显示,本文算法不仅能够有效降低测试功耗,而且对故障覆盖率以及测试时间没有任何影响.

1 扫描测试的基本原理

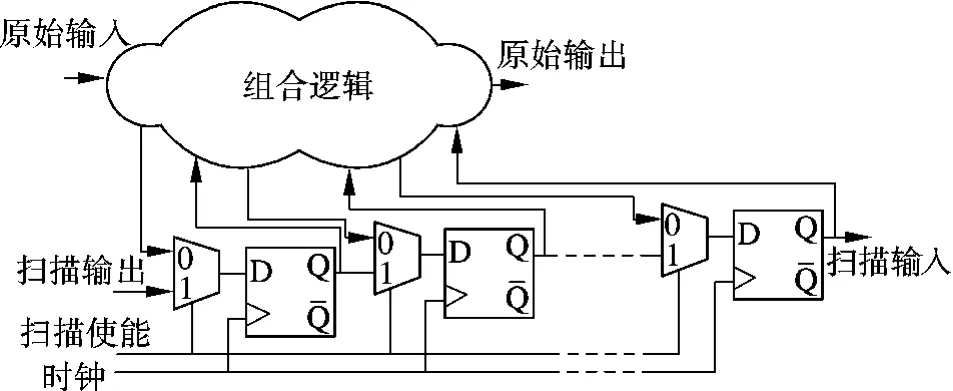

扫描测试是一种应用较广的结构化可测性设计方法.无压缩机制的扫描测试可分为以下2个步骤:①将电路中的普通触发器替换为扫描触发器;②将扫描触发器连接成扫描链,扫描链的数量可以根据扫描触发器的总数以及芯片可复用的引脚数推算得到.在测试过程中,测试激励从ATE通道输入到芯片引脚,串行移入每条扫描链,然后捕获电路状态,并将此电路状态称为测试响应.为了便于观测,测试响应将每条扫描链串行移出至芯片输出引脚.扫描触发器最常用的结构是多路器扫描触发器,它与普通触发器的区别仅在于在输入数据端口加上了一个多路选择器.根据扫描触发器替换量的不同,扫描设计可以分为全扫描和部分扫描.图1为全扫描测试原理图.由图可知,当扫描使能为1时,测试激励由扫描输入串行地移入扫描链,各扫描触发器中保存的电路状态则通过扫描输出串行移出;当扫描使能为0时,扫描触发器捕获组合逻辑的输出.基于扫描的测试之所以得到广泛的应用,是因为它将复杂的时序电路测试问题简化为较易处理的组合电路测试问题,从而有效减少了测试向量的数量及施加时间,提高了故障覆盖率.

图1 全扫描测试原理

2 扫描测试功耗分析及影响函数建模

在测试时,CUT(circuit under test)的动态功耗消耗完全由其上施加的测试向量的跳变数量来决定.当施加到CUT上的原始输入或者扫描触发器中的测试向量发生跳变时,CUT内部节点也会产生大量跳变,通常用跳变数量的总和来近似地表示测试时的动态功耗.扫描测试的功耗分为扫描输入功耗和扫描输出功耗2个部分,它们分别由测试向量和输出响应的跳变产生.

每个扫描触发器跳变的数量不仅与测试向量有关,还与其在扫描链中的位置有关.考虑一个包含n个扫描触发器的CUT,其中,扫描触发器分别为s1,s2,…,sn,扫描输入向量分别为 vn,vn-1,…,v1.需要注意的是,并非所有测试向量都会通过每一个触发器.在扫描输入时,通过s1的测试向量为vn,vn-1,…,v1,通过s2的测试向量为 vn-1,vn-2,…,v1,以此类推,通过每一个触发器的测试向量为通过其前一个触发器的测试向量的子集;在扫描输出时则正好相反.因此,在扫描输入时,每个触发器上产生的跳变数量小于等于其前一个触发器的跳变数量;在扫描输出时,每个触发器上产生的跳变数量大于等于其前一个触发器的跳变数量.

当测试向量串行移入扫描链或测试响应串行移出扫描链时,扫描链中的每个扫描触发器上都会产生频繁的跳变.这些跳变传递到CUT组合逻辑中,又会在内部电路线上引起大量不必要的跳变.不同的扫描触发器跳变对其内部组合逻辑锥的影响是由该逻辑锥的拓扑结构决定的.

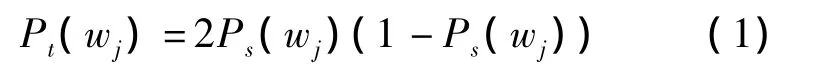

考虑一个包含m个扫描触发器s1,s2,…,sm的CUT,每个触发器的输出线分别用y1,y2,…,ym表示,与yi连接的组合逻辑锥用Ci(1≤i≤m)表示.Ci可视为触发器跳变扇出上逻辑门输出线的集合.将Ci中电路线wj(1≤j≤k,其中k为Ci中的电路线数)的信号线概率Ps(wj)定义成wj等于逻辑1时的概率,信号概率可以通过逻辑门基于简单的概率规则和布尔代数来计算.电路线wj的跳变概率可以定义为信号在任意时间点t由一个逻辑值跳变到另一个逻辑值的概率,用Pt(wj)来表示.假设施加到每个扫描触发器的测试向量逻辑值是相互独立的,则

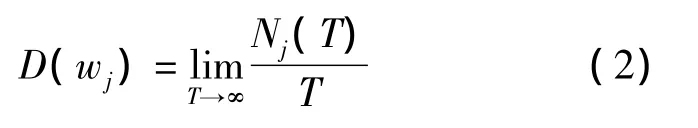

假设Nj(T)表示时间长度T内Ci中电路线wj的跳变数量,并将单位时间内wj上的跳变数量定义为跳变密度D(wj),则

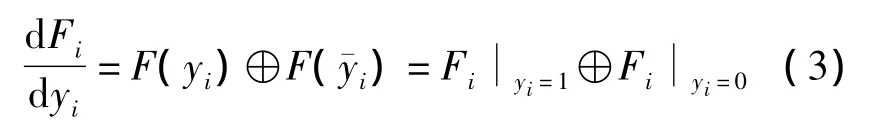

假设Fi为Ci中一条电路线wj的布尔代数,将Fi对于扫描触发器si跳变的敏感程度定义为Fi对于yi的布尔微分,即

式中,⊕表示异或操作.如果装载到扫描触发器si的测试向量的逻辑值是相互独立的,则电路线wj的跳变密度可表示为

在Ci中所有电路线的跳变密度总和为

目前CMOS工艺的动态功耗由电路电容的充电和放电决定,在功耗中占主导地位,因此电路中的功耗主要来自于内部线的负载电容.由于栅电容的并联,扇出多的电路线具有更高的负载电容.为了尽可能简化模型,假设一条电路线的负载电容与该线的扇出成正比.当跳变密度相同时,具有更高扇出的电路线将消耗更多的功耗,因此,在建立影响函数时需要将电路线wj的扇出Oj考虑在内.yi的跳变对于内部组合逻辑锥Ci的影响函数Ei可以表示为

根据此模型,可以有效地评估出每个扫描触发器的输出跳变对内部组合逻辑锥的影响.

3 扫描链重排序算法设计

3.1 基于低功耗的扫描链重排序分析

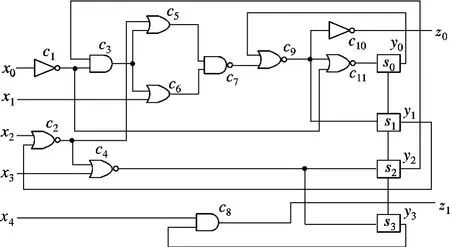

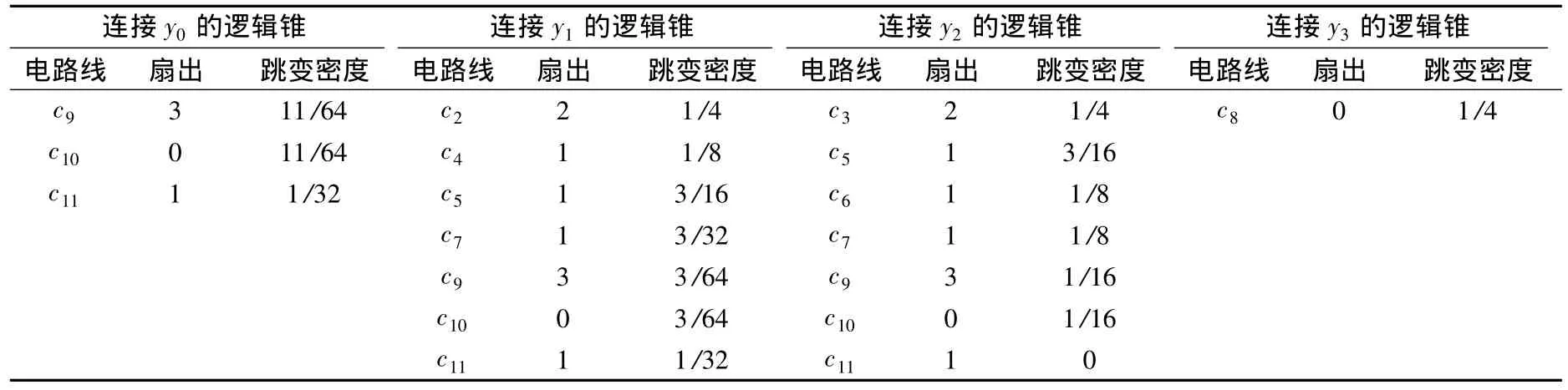

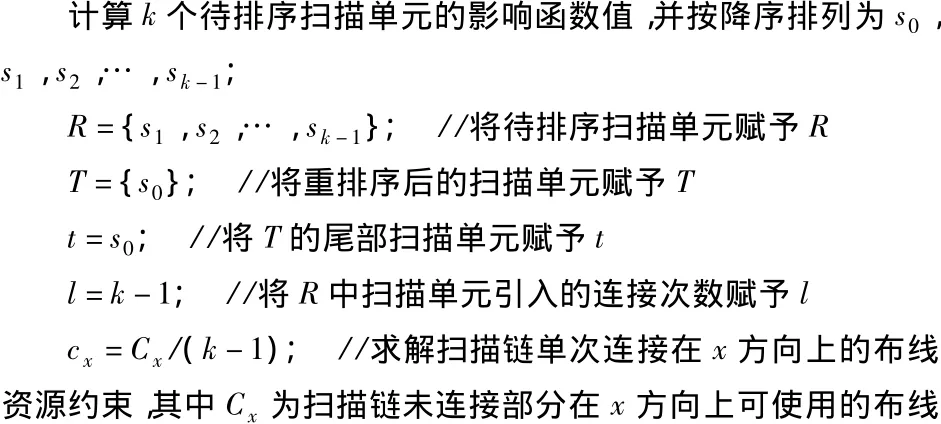

以图2中的电路测试算例为例,计算扫描触发器对于其内部组合逻辑锥的影响函数值.图中,x0~x4为电路的原始输入;s0~s3为扫描触发器;y0~y3为扫描触发器的输出;z0,z1为电路的原始输出.与y0相连的组合逻辑锥中的电路线为c9,c10,c11;与y1相连的组合逻辑锥中的电路线为c2,c4,c5,c7,c9,c10,c11,与y2相连的组合逻辑锥中的电路线为c3,c5,c6,c7,c9,c10,c11,与y3相连的组合逻辑锥中的电路线为c8.假设测试向量中每一位信号的概率均为0.5,由式(1)可得,y0~y3的跳变概率均为0.5,并由式(4)计算得到每个电路线的跳变密度.然后,由式(6)可得,y0~y3对其内部组合逻辑锥的影响函数值分别为 0.546 9,1.078 1,1.125 0,0.表1给出了每个电路线的跳变密度以及扇出.

图2 电路测试算例

表1影响函数值的计算结果

由此可见,影响函数值越大,说明该扫描触发器发生跳变时内部组合逻辑锥的跳变次数越多,功耗也越大.解决办法是将影响函数值大的触发器排在扫描链中跳变次数少的位置.在扫描输入时,每个触发器上产生的跳变数量小于等于前一个触发器的跳变数量;在扫描输出时,每个触发器上产生的跳变数量大于等于前一个触发器的跳变数量.如果扫描链中的触发器按其影响函数值升序排列,便可降低扫描输入时的功耗,但却增加了扫描输出时的功耗;如果扫描链中的触发器按其影响函数值的降序排列,便可增加扫描输入时的功耗,但却降低了扫描输出时的功耗.由ATPG(automatic test pattern generation)产生的未经填充的测试向量包含大量的不定态(既可为逻辑1也可为逻辑0).通常,对于CUT中所有的单固定类型故障,原始测试向量集合只有1%~10%的比特位需要确定的逻辑值,其他比特位均为不定态[9-10].而扫描输出的测试响应是由电路中组合逻辑反馈回来的,不包含不定态.从概率上讲,扫描输入时测试向量的跳变次数明显少于扫描输出时测试响应的跳变次数.因此,本文将扫描链中的扫描触发器按其影响函数值的降序排列,虽然小幅增加了扫描输入时的功耗,但是扫描输出时降低的功耗幅度却更大,整体而言测试总功耗会明显降低.

3.2 布线约束下的扫描链重排序算法

在目前的集成电路设计中,布线决定了芯片的面积、时序以及功耗.因此,扫描链的重排序需要引入布线约束.本文根据扫描链结构的特殊性,分析了布线约束对扫描链重新排序的具体影响,并提出了一种简单有效的算法以同时兼顾低功耗和布线约束.

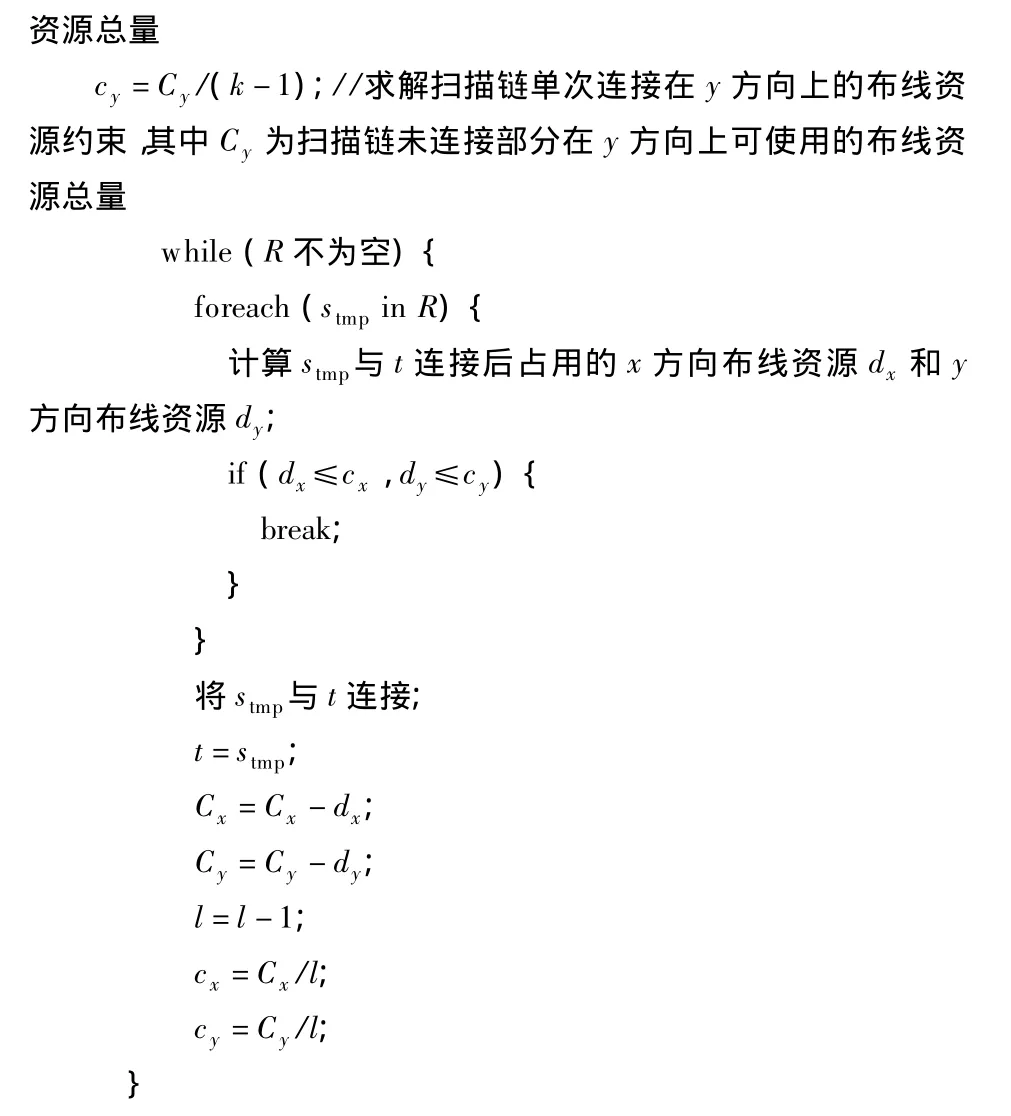

扫描单元之间的长线会导致扫描移位频率降低,扫描链连接对布线资源的过多占用会导致布线拥塞(routing congestion).因此,影响扫描链重排序的布线约束主要包括扫描移位频率的要求和布线资源的限制.其中,扫描移位频率的要求相对比较容易满足,其原因在于:① 随着近年来测试向量压缩技术的不断发展,测试时间的控制并不依赖于扫描移位频率的提高,且过高的扫描移位频率会造成测试功耗过高以及芯片过杀的问题.② 目前业内普遍采用的模块化扫描链设计方法决定了同一条扫描链上的寄存器在版图上距离不会太远,扫描移位的路径上除了布线延迟外仅包含一级选择器的延迟.此外,布线资源的优化在一定程度上也减少了扫描单元间出现长线的概率.由此可知,在设计算法时可以只将布线资源占用作为低功耗扫描链重新排序的影响因子,从而使问题简化.具体算法设计如下:

该算法在实现低功耗优化的同时兼顾了布线约束,不需要额外的硬件开销,进行一次运算后便可完成整条扫描链的重新排序.

4 仿真实验结果

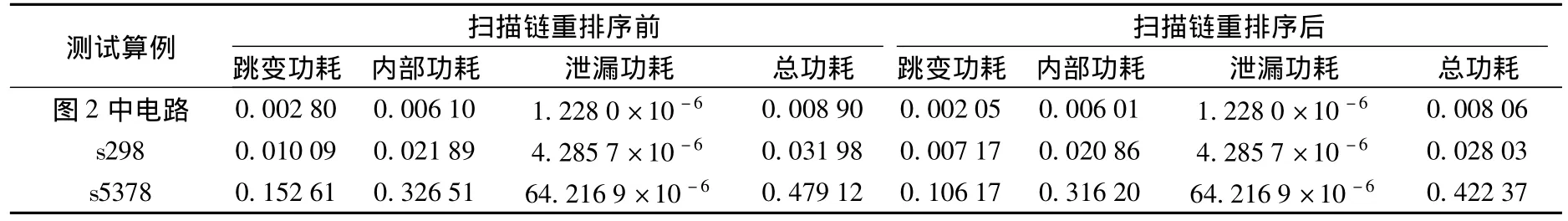

基于图2中的电路测试算例以及ISCAS89基准电路集中的电路s298和s5378,进行仿真实验.电路的扫描综合、ATPG、仿真、功耗分析分别采用EDA 工 具 中 的 DFT Compiler,Testkompress,VCS,Power Compiler模块,综合和仿真库使用TSMC 0.18 μm工艺库.仿真过程如下:首先,采用DFT Compiler模块对电路的门级网表进行扫描综合,并插入扫描链,扫描单元的排列顺序由工具自由决定;然后,通过对扫描链插入的报告进行分析,确定电路中没有违反DRC(design rule check)的部分,采用Testkompress模块对电路进行自动测试向量生成,得到的故障覆盖率为100%,并保存测试向量;以1 MHz作为扫描时钟,仿真产生功耗分析时用到的前标注和后标注文件,根据TSMC 0.18 μm工艺库中提供的功耗模型,利用Power Compiler模块汇报出整个扫描测试过程中的功耗.采用本文算法对DFT Compiler输出的扫描链电路进行重新排序,并使用相同工具重新产生测试向量,所得故障覆盖率仍可达到100%,且测试向量总数并未增加.相同条件下3种不同测试算例在扫描链重排序前后的功耗数据对比见表2.由表可知,本文算法可以明显降低跳变功耗,同时也能使内部功耗得到一定优化,从而使总功耗降低约12%.由扫描链重排序前后的ATPG结果对比可知,故障覆盖率 和测试时间没有受到任何影响.

表2 功耗数据对比 mW

5 结语

本文通过分析扫描测试过程中功耗产生的主要原因,建立了扫描触发器跳变对其内部组合逻辑锥的影响函数模型.在此模型的基础上,设计出一种布线约束下的扫描链重排序算法.实验结果表明,本文算法能够取得较好的功耗优化效果,而且不影响故障覆盖率和测试时间,可应用于芯片批量生产测试.

[1] Zhang Jinyi,Zhang Tianbao,Yun Feng,et al.An adjustable clock scan structure for reducing testing peak power[C]//The8th International Conference on ElectronicMeasurementandInstruments(ICEMI07).Xi'an,China,2007:373-377.

[2]Giri C,Choudhary P K,Chattopadhyay S.Scan power reduction through scan architecture modification and test vector reordering[C]//The16th Asian Test Symposium(ATS07).Beijing,China,2007:419-424.

[3]Tsiatouhas Y,Arapoyanni A,Skias D.A scan flip-flop for low-power scan operation[C]//The14th IEEE International Conference on Electronics,Circuits and Systems(ICECS2007).Marrakech,The Kingdom of Morocco,2007:439-442.

[4] Mishra A,Sinha N.Modified scan flip-flop for low power testing[C]//The19th IEEE Asian Test Symposium.Shanghai,China,2010:367-370.

[5]王伟,韩银和,胡瑜,等.一种有效的低功耗扫描测试结构——PowerCut[J].计算机研究与发展,2007(3):473-478.

Wang Wei,Han Yinhe,Hu Yu,et al.An effective lowpower scan architecture — PowerCut[J].Journal of Computer Research and Development,2007(3):473-478.(in Chinese)

[6]Alpaslan E,Huang Y,Lin X.On reducing scan shift activity at RTL[J].IEEE Trans on Computer-Aided Design of Integrated Circuits and Systems,2010,29(7):1110-1120.

[7]Sabne A,Tiwari R,Shrivastava A.A generic low power scan chain wrapper for designs using scan compression[C]//The28th VLSI Test Symposium.Santa Cruz,CA,USA,2010:135-140.

[8] Baek Chul Ki,Kim Insoo,Kim Jung Tae,et al.A dynamic scan chain reordering for low-power[C]//The2nd International Conference on Information Technology Convergence and Services(ITCS2010).Cebu,Philippines,2010:1-4.

[9] Shi Youhua,Togawa Nozomu,Kimura Shinji.Selective low-care coding:a means for test data compression in circuits with multiple scan chains[J].IEICE Transactions on Fundamentals of Electronics,Communications and Computer Sciences,2006,89(4):996-1004.

[10] Tudu J T,Larssont E,Singh V.On minimization of peak power for scan circuit during test[C]//The14th IEEE European Test Symposium.Sevilla,Spain,2009:25-30.

Routing-constrained low power scan test

Huang Ning Zhu En Liu Wensong Lin Ye

(Institute of RF-and OE-ICs,Southeast University,Nanjing 210096,China)

The causes of the power consumption during the scan test are analyzed.The effects of the scan flip-flop's transitions on the internal combinational logic cone are studied and modeled.The calculated values of the influence function are used as the basis for the scan chain reordering.Then,the effects of the routing constraints on the scan chain reordering are analyzed based on the special scan chain structure.With the simplification of the routing constraints,an algorithm taking both low power consumption and routing constraints into account is presented.This algorithm can get rid of iterations and obtain the result of the scan chain reordering by a single run.The transition times of the scan cells can be reduced with the high impact value under the premise of the feasible back-end design,improving the scan test power consumption.The simulation experiments are performed on the test case and the circuits s298 and s5378 in the ISCAS89 benchmark circuits.The results show that this algorithm can reduce the scan test power by 12%without any effect on fault coverage and test time.Moreover,it does not require any hardware overhead and can be used for silicon production test.

scan chain;logic cone;low power;routing constraint;reordering

TN407

A

1001-0505(2012)02-0239-05

10.3969/j.issn.1001 -0505.2012.02.009

2011-08-16.

黄宁(1983—),男,博士生;朱恩(联系人),男,博士,教授,博士生导师,zhuenpro@seu.edu.cn.

国家高技术研究发展计划(863计划)资助项目(2009AA11Z219).

黄宁,朱恩,刘文松,等.布线约束下的低功耗扫描测试[J].东南大学学报:自然科学版,2012,42(2):239-243.[doi:10.3969/j.issn.1001 -0505.2012.02.009]