SOI双槽隔离结构的耐压特性

2012-09-17朱奎英刘斯扬钱钦松孙伟锋

陈 健 朱奎英 刘斯扬 钱钦松 孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

SOI双槽隔离结构的耐压特性

陈 健 朱奎英 刘斯扬 钱钦松 孙伟锋

(东南大学国家专用集成电路系统工程技术研究中心,南京 210096)

理论推导了绝缘体上硅(SOI)双槽隔离结构的耐压模型.该模型表明,在SOI双槽隔离结构中,因隔离氧化层压降的不均衡,高压侧隔离氧化层提前发生介质击穿,从而导致SOI双槽隔离结构的临界击穿电压小于理论值.增大沟槽纵横比和减小槽间距可以减弱隔离氧化层上压降的不均衡性,提高SOI双槽隔离结构的临界击穿电压.Sentaurus器件仿真软件的模拟结果和华润上华半导体有限公司0.5 μm 200 V SOI工艺平台下的流片测试结果均证明,减小槽间距和增大沟槽纵横比是提高双槽隔离结构临界击穿电压的有效方法,同时也证明了该耐压模型的正确性.

双槽隔离结构;耐压模型;压降不均衡;沟槽纵横比;槽间距;临界击穿电压

功率集成电路是一种高低压兼容的芯片,高低压之间的隔离至关重要.随着芯片集成度的提高,隔离要求也日益提高.最早被使用的PN结隔离技术和局部氧化隔离技术[1-2]已经不能满足需求,深槽隔离技术应运而生.该技术采用SiO2作为绝缘材料,这种深槽结构具有漏电小、耐压高、寄生电容小、耗费面积小等优点[3-4].因此,SOI深槽隔离是SOI功率集成电路的理想隔离结构.

然而,SOI深槽隔离结构存在两大结构弱点:①沟槽顶部拐角处较为陡直,晶格缺陷较多,此处电势线较为集中,导致漏电增大[5];② 在沟槽底部,横向过刻蚀效应和界面应力效应导致隔离氧化层变薄,SOI深槽结构的击穿电压降低.Lerner等[6]在隔离氧化层生长工艺之前采用牺牲氧化工艺,减缓了沟槽底部隔离氧化层变薄的趋势,但击穿电压依然偏小.Zhu等[7]通过刻蚀沟槽下方部分埋氧化层以增厚底部隔离氧化层,但埋氧化层的刻蚀厚度难以控制.文献[8]指出,在不改变工艺条件的情况下采用双槽隔离结构,既可解决整体隔离结构耐压低的问题,又可大幅提高隔离结构的经时介质击穿寿命.然而,SOI双槽隔离结构的耐压机制仍不明确.

本文理论推导了SOI双槽隔离结构的耐压模型.该模型表明双槽隔离结构的临界击穿电压与沟槽纵横比呈正相关,与槽间距呈负相关.然后,采用Sentaurus模拟软件和工艺流片测试对上述结论进行了验证.实验结果表明,双槽隔离结构的临界击穿电压随槽间距减小而增大,随沟槽纵横比增大而增大,从而证明了本文模型的正确性.

1 SOI双槽隔离结构及制备工艺

图1为7 μm深的SOI双槽隔离结构的示意图.图中,A,B,C,D 皆为隔离氧化层;埋氧化层厚度为1 μm,隔离氧化层厚度约为 2.2 μm,双槽隔离结构由2个串联的单槽E和F组成,单槽结构由两侧隔离氧化层和中间的浮空多晶硅区域组成,两槽之间的硅区域处于浮空态.槽两侧的隔离氧化层和埋氧化层分别具有隔离横向和纵向电信号的作用,使隔离结构内部的硅区成为独立的隔离岛[9].填充的多晶硅具有维持沟槽机械稳定的作用[3,7,10].W为沟槽的宽度;H为沟槽的深度;S为槽间距;M,N均为双槽两侧的测试电极;Q0为双槽包围的硅区下方埋氧化层两侧所感应的电荷量;Q1,Q2,Q5,Q6分别为隔离氧化层 A,B,C,D 两侧所感应的电荷量;Q3为槽E内浮空多晶硅区域下方埋氧化层两侧所感应的电荷量;Q4为硅区下方埋氧化层上下两侧所感应的电荷量.

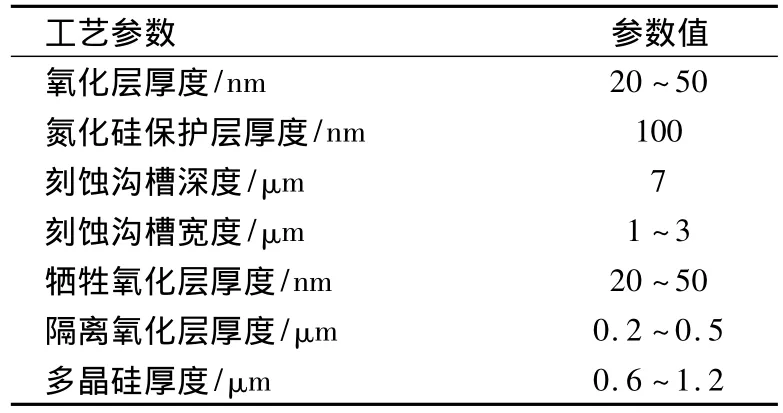

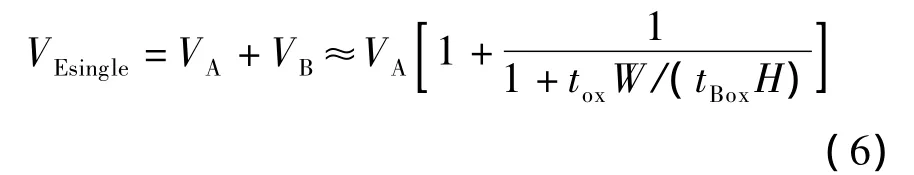

表1列出了0.5 μm 200 V SOI工艺平台下双槽隔离结构的主要工艺参数.工艺流程如下:为了更好地保护硅膜表面,首先淀积缓冲氧化层和氮化硅,用以作为刻蚀顶层硅膜的阻挡层;刻蚀顶层硅膜后,采取牺牲氧化工艺,使侧壁更加平滑,以确保隔离氧化层的厚度保持均匀;然后,生长隔离氧化层,这与生长场氧化层的工艺兼容;最后,在槽中填充多晶硅.

图1 SOI双槽隔离结构的示意图

表1 SOI深槽隔离结构的主要工艺参数

2 SOI双槽隔离结构的耐压模型

对SOI双槽隔离结构中的电极M偏置高压,并将电极N和衬底接地,感应电荷分布如图1所示.

假设双槽内部区域呈正方形,L为槽内正方形区域的边长;S'A,S'B,S'tb分别为隔离氧化层A,B和槽底部埋氧化层的表面积;VA,VB,VC,VD分别为隔离氧化层 A,B,C,D 上的电压;tox,tBox分别为硅槽侧壁两侧的隔离氧化层和浮空多晶硅区域下方埋氧化层的厚度;CA,CB,CBox分别为硅槽侧壁两侧的隔离氧化层A,B和浮空多晶硅区域下方埋氧化层的等效单位面积平板电容;Q为电极M感应的总电荷量.根据电荷守恒定律可以得到

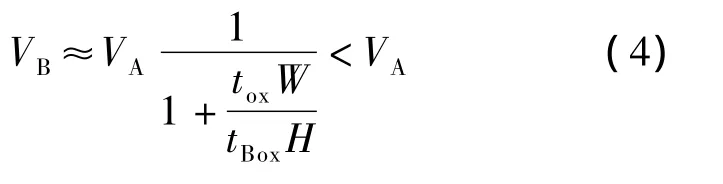

考虑到L≫W,式(3)可以简化为

同理可知,VA,VB,VC,VD满足如下关系式:

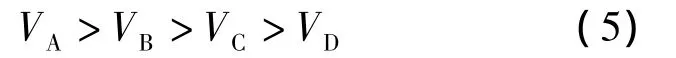

由此可知,槽E所承担的电压VEsingle可以表示为

SOI双槽隔离结构所承担的电压Vdouble可以表示为

式中,t=1+1/1+toxW/(tBoxH(

))为单槽平衡因子.由于槽E和F之间的硅区域处于浮空状态且呈电中性,其内部的正负电荷数目相等,故有

由式(8)可得VC和VB的关系为

式中,Cox2,Cox3,CBS分别为隔离氧化层 B,C 和槽之间埋氧化层的平板电容.

将式(4)和(9)代入式(7),可得SOI双槽隔离结构所承担的电压Vdouble与各参数的关系,即

由式(5)可知,隔离氧化层上的电压沿电势由大到小的方向依次减小,靠近高压侧的隔离氧化层A上承担的电压降最大,即双槽内隔离氧化层上的压降具有不均衡性.随着外加偏压不断增大,隔离氧化层A中的电场强度提前达到临界值,发生介质击穿,并失去分压作用,剩余的隔离氧化层势必会因所承受的电压过大而瞬间发生介质击穿,最终导致整体结构的临界击穿电压小于理论值.由式(4)和(10)可知,SOI双槽隔离结构的临界击穿电压与沟槽平衡因子成正相关,与槽间距成负相关.由于tox与tBox主要由整个芯片的性能参数决定,要使t=1+1/1+toxW/(tBoxH

())→2,则需满足沟槽纵横比H/W→∞.增大沟槽纵横比并减小槽间距时,浮空区域的表面积减少,从而抑制了隔离氧化层中压降不均衡的现象,提高了SOI双槽隔离结构的临界击穿电压.当H/W→∞且S=0同时成立时,SOI双槽结构的临界击穿电压可以达到最大值Vmax=4VA=4Ecriticaltox,其中Ecritical为氧化层的临界电场强度.

3 结果与讨论

为了更好地验证所建立的耐压模型和隔离氧化层中的压降不均衡现象,本文对SOI双槽隔离结构进行模拟仿真及实际流片测试.在模拟仿真和实际测试过程中,将电极N和衬底均接地,对电极M进行电压扫描,记录2个电极之间的电压-电流曲线.

P型和N型区域内均有需要被隔离的器件,因此隔离结构位于P型和N型区域内的情况均存在.本文采用Sentaurus器件仿真软件模拟了槽间距的变化对N型区域内SOI双槽隔离结构的电场分布和电场强度的影响.模拟结果如图2所示.图中,A1,B1,C1,D1表示槽间距为 4 μm 的 SOI双槽隔离结构中的隔离氧化层;A2,B2,C2,D2表示槽间距为8 μm的SOI双槽隔离结构中的隔离氧化层.由图可知,在外加偏置电压相等的前提下,A2内的电场强度峰值较A1内的电场强度峰值高7.07%;C1和C2内的电场强度峰值分别较A1和A2内的电场强度峰值低30.4%和43.3%.由此说明,增大槽间距会加大各隔离氧化层中电场强度的偏差,从而导致SOI双槽隔离结构中高压侧隔离氧化层提前发生介质击穿,使得临界击穿电压值减小.

图2 不同槽间距下SOI双槽隔离结构内电场分布情况

基于 CSMC 0.5 μm 200 V SOI工艺平台对SOI双槽隔离结构进行了流片测试.根据式(4)和(10)可知,SOI双槽隔离结构的临界击穿电压以及隔离氧化层中压降不均衡的特性同时受槽间距大小和沟槽纵横比影响,为此本文对单一变量进行了实验测试.图3为7 μm深的SOI双槽隔离结构的SEM剖面结构图.尽管槽内出现了微小腔体,但其对结构的隔离效果并没有影响.

图3 SOI双槽隔离结构的SEM剖面结构图

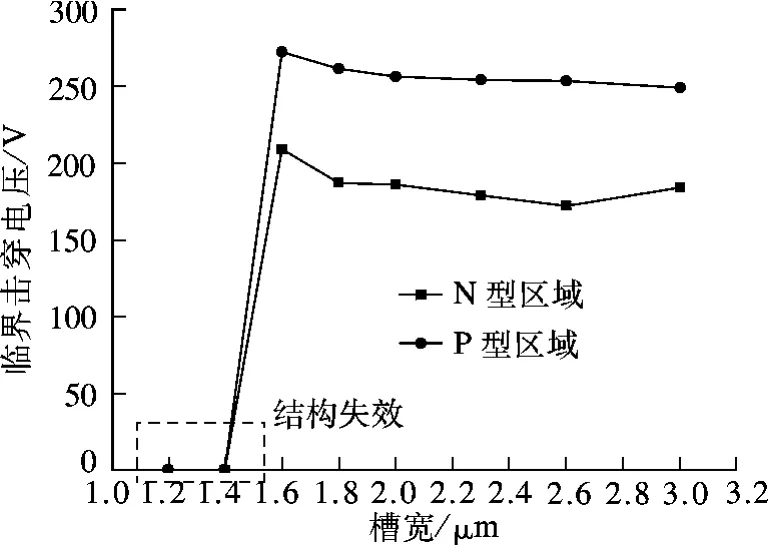

为了避免测试结构因不可恢复的介质击穿而损坏,将SOI双槽结构的漏电流达到1 nA时对应的扫描电压定义为临界击穿电压.对于槽深为7 μm的SOI双槽隔离结构,不同槽间距与其临界击穿电压之间的关系曲线如图4所示.由图可知,当槽间距由5 μm减小到1 μm时,P型和N型区域内SOI双槽隔离结构的临界击穿电压分别增大10.1%和7.4%.槽间距的减小导致两槽之间硅区下方埋氧化层表面的感应电荷数目减少,削弱了隔离氧化层上的压降不均衡性,减小了高压侧隔离氧化层A中的电场强度以及隔离氧化层A和C内电场强度的偏差,最终导致SOI双槽隔离结构的临界击穿电压增大.另外,对临界击穿电压随槽间距S变化的趋势进行实测,所得的结论与式(10)的计算结论一致,证明了式(10)所表达的耐压模型的正确性.同时,当槽间距由5 μm 减小到1μm 时,P型和N型区域内SOI双槽隔离结构的临界击穿电压的模型计算值和实际测试值相差很小,平均相对误差分别为11.5%和5.4%.尽管由于测试精度和工艺偏差的原因,二者存在一定的偏差,但上述结果仍能说明所建立的SOI双槽隔离结构耐压模型是准确的.

SOI硅膜厚度恒定为7 μm,因此可以通过改变槽宽度来实现具有不同纵横比的SOI双槽隔离结构.图5为7 μm深的SOI双槽隔离结构中单槽E的临界击穿电压与槽宽的曲线关系.当槽宽为1.2和1.4 μm 时,沟槽纵横比过大可能导致底部刻蚀不充分,残留有硅通道,槽E的临界击穿电压约为0 V.当槽宽由 3 μm 减小到 1.6 μm 时,P 型和N型区域内单槽E的临界击穿电压值均呈增长趋势,分别增大了9.3%和17.3%.由式(4)可知,随着沟槽纵横比的增大,隔离氧化层上的压降不均衡性不断减弱,高压侧隔离氧化层中的电场峰值不断降低,导致单槽E的临界击穿电压不断增大.由此可知,模拟结果和测试结果与式(5)、(10)所表述的SOI双槽隔离结构的击穿特性是一致的.

图4 不同槽间距与SOI双槽隔离结构临界击穿电压的关系曲线

图5 SOI单槽E的临界击穿电压与槽宽的关系曲线

4 结语

本文理论推导了SOI双槽隔离结构的耐压模型.该模型表明:隔离氧化层的压降不均衡性导致高压侧隔离氧化层提前发生介质击穿,SOI双槽隔离结构的临界击穿电压低于理论最大值.为了更好地验证耐压模型,分别进行了模拟实验和实际工艺流片测试.根据Sentaurus器件仿真软件的模拟结果可知,SOI双槽隔离结构中各隔离氧化层同时承担电压降,但具有随着槽间距增大而增强的压降不均衡性.由 CSMC 0.5 μm 200 V SOI工艺平台下的流片测试结果可知,SOI双槽隔离结构的临界击穿电压随槽间距减小而增大,随沟槽纵横比增大而增大.模拟结果、测试结果与理论推导得到的耐压模型一致.因此,减小槽间距和增大沟槽纵横比可有效减弱SOI双槽隔离结构中隔离氧化层的压降不均衡性、提高临界击穿电压.

[1]陈星弼.功率MOSFET与高压集成电路[M].南京:东南大学出版社,1990:340-342.

[2]杨春.SOI高压集成电路的隔离技术研究[D].成都:电子科技大学微电子学院,2006.

[3] Lee S,Bashir R.Modeling and characterization of deep trench isolation structures[J].Microelectronics Journal,2001,32(4):295-300.

[4] André Lange,Steffen Heinz,Klaus Erler,et al.Modeling the leakage current of dielectric isolation structures in a high-voltage semiconductor technology[C]//Industrial Electronics2007International Symposium.Vigo,Spain,2007:1430-1434.

[5]Louis N H,James D G.Deep trench isolation with surface contact to substrate:United States,4980747[P].1990-12-25.

[6]Lerner R,Eckoldt U,Hoelke A,et al.Optimized deep trench isolation for high voltage smart power process[C]//Proceedings of the17th International Symposium On Power Semiconductor Devices&IC's.Santa Barbara,CA,USA,2005:1-4.

[7] Zhu Kuiying,Qian Qinsong,Zhu Jing,et al.Process optimization of a deep trench isolation structure for high voltage SOI devices [J].Journal of Semiconductors,2010,31(12):1240091-1240094.

[8] Ralf Lerner,Uwe Eckoldt,Klaus Schottmann.Time dependent isolation capabilityofhigh voltage deep trench isolation[C]//Proceedings of the20th International Symposium on Power Semiconductor Devices&IC’s.Orlando,Florida,USA,2008:205-208.

[9] Clavelier L,Charlet B,Giffard B,et al.Deep trench isolation for 600V SOI power devices[C]//European Solid-State Device Research Conference.Estoril,Portugal,2003:497-500.

[10] Dean Jennings,San Ramon.Polysilicon filled trench isolation structure for SOI integrated circuits:United States,6096621[P].2000-08-01.

Breakdown characteristic of SOI trench structure

Chen Jian Zhu Kuiying Liu Siyang Qian Qingsong Sun Weifeng

(National ASIC System Engineering Research Center,Southeast University,Nanjing 210096,China)

The breakdown model of double trench isolation structure on silicon on insulator(SOI)wafer is proposed.This model indicates that the imbalance of the voltage drop at isolation oxide layers of the double trench isolation structure leads the isolation oxide layer near the high voltage region to break down in advance,making the critical breakdown voltage less than the theoretical value.Furthermore,increasing the trench aspect ratio and decreasing the trench spacing can weaken the imbalance of the voltage drop and improve the critical breakdown voltage of the double trench isolation structure on SOI wafer.The simulation results by Sentaurus device simulation software and the experiment results on CSMC 0.5 μm 200 V SOI process platform from Central Semiconductor Manufacturing Technologies Fab1 Co.,Ltd.show that decreasing the trench spacing and increasing the trench aspect ratio are the effective way to improve the critical breakdown voltage of the double trench isolation structure on SOI wafer.The results also prove the validity of the proposed model.

double trench isolation structure;breakdown model;imbalance of voltage drop;trench aspect ratio;trench spacing;critical breakdown voltage

TN386

A

1001-0505(2012)02-0234-05

10.3969/j.issn.1001 -0505.2012.02.008

2011-09-09.

陈健(1965—),男,博士生;孙伟锋(联系人),男,博士,教授,博士生导师,swffrog@seu.edu.cn.

江苏省自然科学基金资助项目(BK2011059).

陈健,朱奎英,刘斯扬,等.SOI双槽隔离结构的耐压特性[J].东南大学学报:自然科学版,2012,42(2):234-238.[doi:10.3969/j.issn.1001 -0505.2012.02.008]