基于DDS的数字IQ调制

2012-09-12彭龙田书林刘科

彭龙, 田书林, 刘科

(电子科技大学自动化工程学院,四川 成都 611731)

0 引言

正交调制通过将同相分量和正交分量与两路正交的载波信号分别调制之后相加来实现已调信号,其实现过程有模拟和数字两种。由于外界噪声干扰等因素的影响,模拟方法实现正交调制难以保证相位的正交性以及正交信号幅度的一致性[1]。随着数字技术,特别是直接数字频率合成(direct digital synthesis, DDS)技术的飞速发展,数字方法实现正交调制由于相位正交性好而得到广泛的采用[2]。文献[3]使用DDS芯片AD9854产生相位正交性好的载波信号,但调制过程通过模拟电路实现,降低了正交信号的幅度一致性和整个系统的抗干扰性。

本文在利用FPGA实现DDS的基础上[4~8],用DDS原理产生两路相位正交性好的数字正交载波信号,设计了用于产生数字同相分量和正交分量的IQ映射模块,最后实现了全数字的IQ调制。这种方法具有精度高、可重复性好和抗干扰能力强的特点。

1 IQ调制基本原理

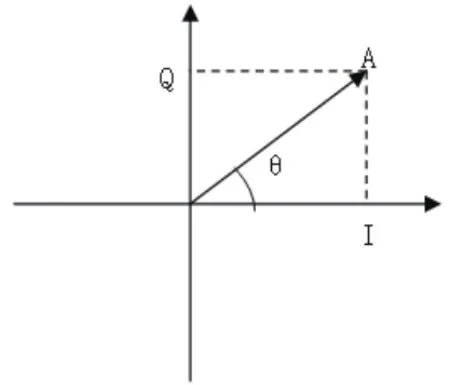

调制是使信号f(t)控制载波的某一个(或几个)参数,使被控制的参数按照f(t)的规律变化的过程。载波信号Acos(wt+θ)可供改变的参数只有振幅、频率和相位3种。由于相位的微分即是频率,所以载波信号的振幅和相位可以说是两个主要的调制变量。极坐标上任意点到原点的距离和相角,正好可以用来表示载波的振幅和相位,所以,我们可以用极坐标上的点来表示载波的调制情况。极坐标方式的调制波表示方法可转化为直角坐标方式,也就是I-Q图。如图1所示,载波振幅A和相位θ可由极坐标上一点表示,这一点决定的向量在横轴和纵轴上的投影分别为I值和Q值,I为同相位(In-phase)分量,Q为90°相移(Quadrate)分量。IQ调制的表达式如下:

图1 载波Acos(wt+θ)的I-Q图

其中,

代表调制波形的同相分量;

代表调制波形90°相移分量;

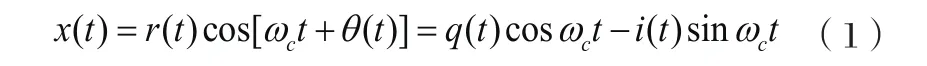

根据公式(1)可见,IQ调制实现的原理图如图2所示。

图2 IQ调制实现原理图

2 IQ数字调制的实现方法

2.1 总体方案

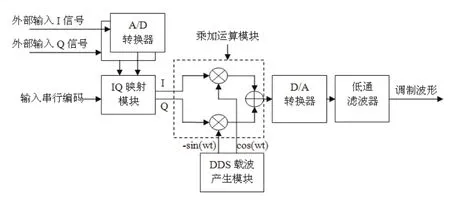

IQ数字调制的实现方法如图3所示,包括3个功能模块,分别是IQ映射模块、DDS载波产生模块和乘加运算模块。本方案的工作流程是:当选择内部IQ源时,将二进制串行编码输入到IQ映射模块中,IQ映射模块根据需要进行的多进制数字调制映射出数字的同向分量和正交分量,产生的同相分量与正交分量与DDS载波产生模块产生的两路数字的正交载波信号在乘加模块中进行乘加运算,再将运算结果经DAC数模转换后通过过低通滤波器后便可得到IQ调制波;当选择外部IQ源时,调制波形的同相分量与正交分量将由外部输入并经过ADC模数转换之后提供给乘加运算模块,其他的操作与内部IQ源的情况一样。

图3 数字IQ调制的整体框图

2.2 IQ映射模块

IQ映射模块如图4所示,用于提供IQ数字调制的同相分量I信号与90°相移分量Q信号。IQ映射模块输出的IQ信号可分为内部源IQ信号和外部源IQ信号。当信号IQ_SRC控制I源选择开关和Q源选择开关选择外部IQ源时,IQ映射模块将外部输入模拟的I信号与Q信号经过A/D转换器转换后送入后面的处理模块,当IQ_SRC选择内部源时,IQ映射模块将根据具体的多进制数字调制映射出与输入的串行二进制编码所对应的数字I信号和Q信号。基本的映射原理是:先将需要进行数字IQ调制的多进制数字调制的星座图上各点的同相分量I与正交方分量Q分别按用户需要的顺序存储在各自的存储器I值RAM和Q值RAM中,然后,将二进制串行编码经过串并转换后,地址映射单元再根据具体的多进制数字调制方式将串并转换后的并行数据转换成I值RAM和Q值RAM的地址,读出该地址对应的I值与Q值。在本方案中,内部源的IQ映射是通过串并转换器,地址映射单元,地址更新计数器,I值RAM和Q值RAM来实现。串并转换器是一个串行输入,并行输出的移位寄存器,其宽度是根据需要实现的最多状态的多进制数字调制状态数量Mmax来确定的。地址映射单元根据需要实现的多进制数字调制方式在计数值为NM的地址更新计数器提供的时钟clkupdate的驱动下读入CP,然后将CP的低NM作为I值RAM和Q值RAM的地址AI,AQ输出。

图4 IQ映射模块

地址更新计数器的模NM及clkupdate的频率fupdate的计算方法如下:其中,M为多进制数字调制需要实现的状态数量。

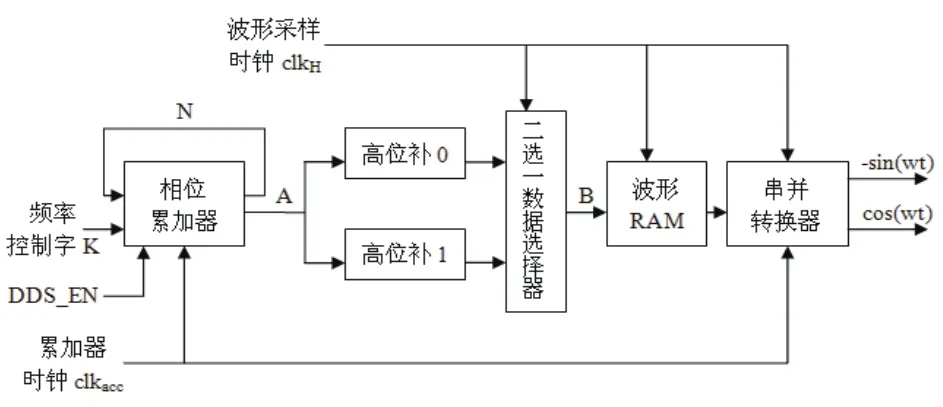

2.3 DDS载波产生模块

DDS载波产生模块如图5,用于产生数字IQ调制的同相载波和90°相移载波。在本方案中,由于需要两路具有较好正交性的数字载波信号,所以,将两路正交的载波波形存储在DDS的波形RAM中,波形RAM的前半部分存同相载波,后半部分存90°相移载波;将相位累加器产生的地址的高A位分为两路,一路在高位补0作为波形RAM前半部分的读地址,另一路在高位补1作为波形RAM后半部分的读地址,然后将这两路地址经过并串转换后得到了一路(A+1)位宽的前后部分地址交替的RAM读地址B;波形RAM输出地址B所对应的波形样点,波形样点再经过串并转换后输出两路正交的载波信号。由于两路载波数据是由同一个DDS模块产生,所以可以保证同时输出的两路正交载波的两个样点的相位偏移严格相等,从而保证了两路正交载波具有非常好的相位正交性。

图5 DDS载波产生模块

3 实验验证与分析

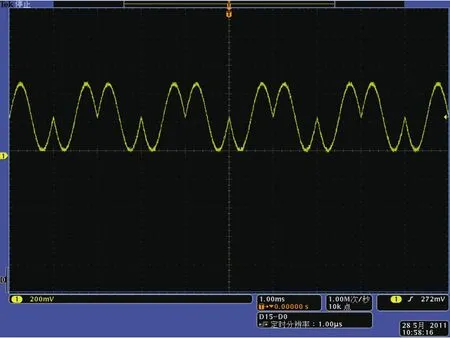

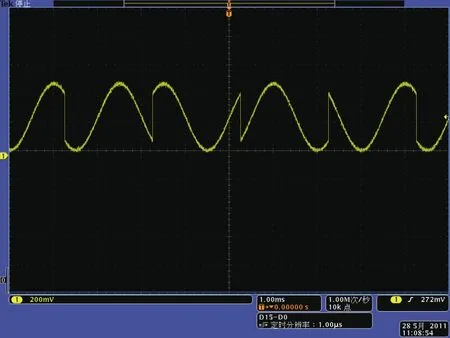

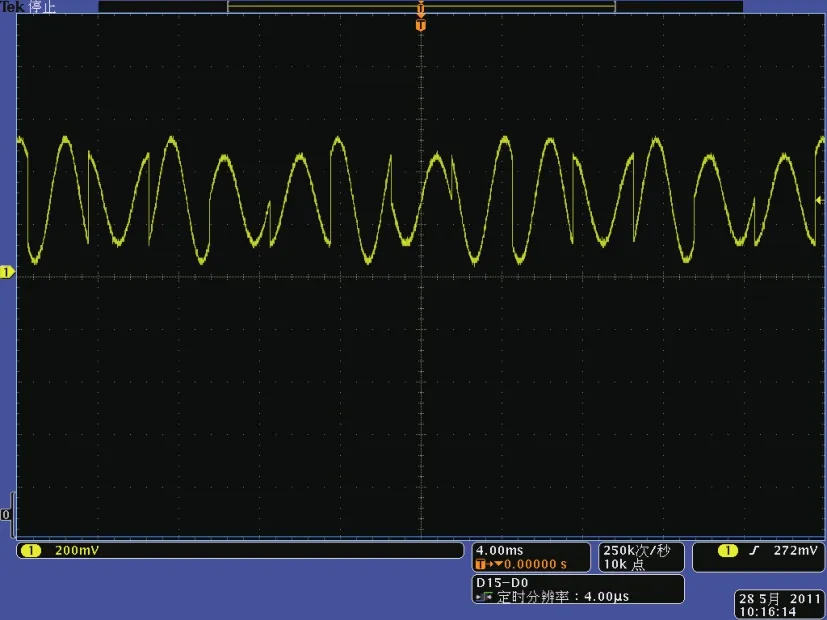

为了验证上述方案的可行性,本文采用“FPGA+RAM+DAC”的方案构建了200MSPS基于DDS的验证模块。该模块中,波形RAM的采样率是200MSPS,因此,经过串并转换后,每路载波的采样率是100MSPS。串行二进制编码的最高码率是1Mbps。图6、图7和图8是该方案分别实现的码率为1Kbps的BPSK调制、QPSK调制和8QAM调制。

由图6,图7,图8完成的BPSK、QPSK及8QAM调制效果可以看出,基于DDS的数字IQ调制能够可靠的实现BPSK和MPSK等多进制数字调制。

图6 用本方案实现的BPSK波形

图7 用本方案实现的BPSK波形

图8 用本方案实现的8QAM波形

4 结论

目前,正交调制实现的过程主要有数字和模拟两种。模拟电路在实现IQ调制过程中,不可避免的会引入干扰,正交信号幅度的一致性以及相位的正交性很难保证。而基于DDS的数字IQ调制,由DDS模块产生数字的正交载波信号,用IQ映射模块产生数字的同相分量和90°相移分量,调制过程也是用数字的乘加运算模块来完成,因此有效的保证了IQ调制的幅度一致性和相位的正交性。

在实验中,采用“FPGA+RAM+DAC”的结构构建的200MSPS基于DDS的验证模块,可实现MPSK和MQAM等多进制调制。但在数字系统中,载波及调制分量都是由有限位数的数字信号表示的,而且由于DAC的分辨率有限,在调制过程中进行乘加运算后的数据位数为了与DAC的位数一致,需要截掉低位数据。由于载波和调制分量用数字量表示时位数的有限性和运算结果数据的低位截断而引起的误差还需要定量分析。同时,提高DDS波形RAM和DAC的采样率以实现对更高频率基带信号的IQ调制也是数字IQ调制需要继续研究的问题。

[1]刘泽华,王华.正交调制过程的误差分析[J].微电子技术,2004,187(20):78-80.

[2]辛勤,龚享铱.多制式调制模块的原理与设计[J].国防科技大学学报,2000,22(5):55-59.

[3]王利众,费元春,郭德淳.DDS在正交调制技术中的应用[J].电子技术应用,2002,28(3):48-49.

[4]Eric D,Adler.Edward A,Viveiros,Tuan Ton.Direct Digital Synthesis Applications for Radar Development[C].IEEE International Radar Conference,1995:224-225.

[5]GYLES C.800Ms/s arbitrary function generator[J].IEEE Transctions on instrumentation and Measurement.1990(39):96-100.

[6]刘科,田书林,肖寅东.基于多路DAC伪插值的任意波形合成技术研究[J].仪器仪表学报,2009,30(12):2474-2479.

[7]田书林,刘科,周鹏.基于双DDS的高速任意波形发生器实现技术[J].仪器仪表学报,2004,25(4):557-560.

[8]古天祥,王厚军,习友宝,詹惠琴.电子测量原理[M].北京:机械工业出版社,2004.