基于A结E构S 共享和多级流水线的加密算法的研究

2012-08-22王群

王 群

(青岛科技大学信息学院 山东 青岛 266061)

2000年10月,美国国家标准技术局(NIST)选择了两位比利时研究者Daemen和Rijmen提出的Rijndael算法,即AES(高级加密标准)。它具有128bits的分组长度,三种可选的密钥长度,即128bits、196bits和 256bits。

AES可以抵抗所有设计中已知的攻击方法,具有较高的安全强度。文中阐述了AES算法的原理,并对其加解密模块进行优化,提出了一种基于结构共享和多级流水线的AES算法实现方案,并重点阐述了实现过程。

1 AES算法介绍

AES算法是一种迭代分组算法,采用128bits的分组长度,三种可选密钥长度128bits,192bits和256bits。对于不同的密钥长度,所需的加解密轮数不同。本文主要讨论分组长度和密钥长度128bits的情况。

整个加密过程包括11轮迭代。其中Round0只有Add Round Key操作。Round1-Round9具有完全相同的操作, 依次经过 SubBytes、Shift Rows、Mix Columns和Add Round Key四种操作。Round10只包括 SubBytes、Shift Rows和 Add Round Key 三种操作。解密过程是加密过程的逆过程。关于AES算法的详细描述见参考文献[1]。

2 加解密模块的结构共享

2.1 字节变换(SubBytes)

当前实现字节变化的方法有两种:一是有限域运算的方法;一是查找表的方法。前者运算复杂,后者容易实现,并且运行速度更快,但是硬件开销较大。考虑到可以利用FPGA自带的Block RAM资源,在设计中采用了查找表的实现方式。

如果将用于加密的Sbox表和用于解密的Inverse Sbox表同时存放在FPGA的Block RAM中,会造成RAM资源的大量消耗。为降低硬件资源的消耗,设计中采用重新配置的方法。加密时一次性加载16个Sbox表,而在解密时,对存放这些Sbox表的RAM重新写入Inverse Sbox表的数据。

2.2 行移位(Shift Rows)

本文采用128bits并行算法,行移位变换可按照移位的方向和字节数连线,几乎不占用硬件资源和产生延时,然后通过选通器选择正向或逆向行移位变换。

2.3 列混合(Mix Columns)/逆列混合(InvMix Columns)

根据算法原理,列混合变换就是输入状态矩阵与一个系数矩阵相乘。

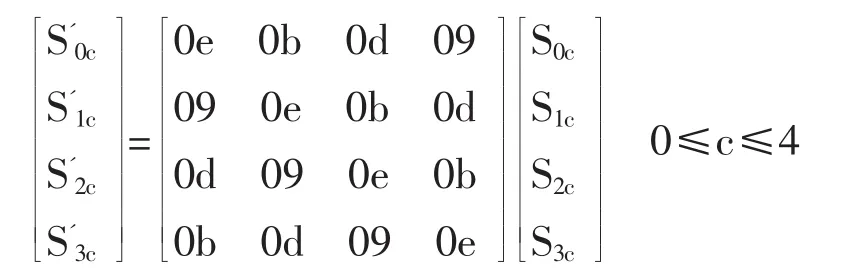

列混合变换表示为:

逆列混合变换表示为:

逆列混合变换的系数矩阵与列混合变换的系数矩阵存在如下关系:

因此,在实现逆列混合变换时,只需在列混合变换之前先执行个逻辑电路。将列混合变换和逆列混合变换进行整合,使得列混合电路可以复用于解密过程中,并由选择器来实现加密/解密操作,实现了硬件资源的共享。

3 流水线结构的设计

3.1 AES算法实现流水线的可行性

第一,AES算法加解密过程的核心是10次轮操作,前一轮操作的输出即为下一轮操作的输入。第二,AES算法每次对一个128bits的数据块进行编码,当采用ECB工作模式时,前后进行编码的数据块间不存在相关性。由于上述特点,AES算法完全能够以流水线的形式实现。

3.2 两类典型的流水线结构

AES算法的流水线结构分为轮内流水线结构和轮间流水线结构两种。轮内流水线结构就是把在一个时钟周期内欲完成的运算划分为若干子运算,采用寄存器输出模式。轮间流水线结构就是在相邻的两轮加解密模块之间加入寄存器,每个时钟周期各加解密模块都有一次输出,从而实现轮间流水线设计。

轮内流水线结构被很多人讨论并使用,这种结构既可缩短延时路径,提高时钟频率,又可使各子运算同时进行。但是这种结构增加了控制的复杂度同时占用大量的存储单元,对于FPGA实现来说将是很大的负担。另一方面,这种结构虽然能提高仿真频率,但是系统吞吐量并没有明显的提高。因此,本设计采用轮间流水线结构。

3.3 AES算法的5级流水线设计

传统的AES算法流水线为10级流水线结构或2级流水线结构。这两种设计结构都存在弊端。10级流水线结构能够最大限度的利用流水线技术,提高系统的运行速度,但是要耗用大量FPGA的逻辑单元和存储单元;而2级流水线结构设计,虽然占用FPGA资源较少,但是没有有效的利用好流水线技术。本文提出的5级流水线结构是上述两种设计结构的折中方案,能够最大限度的利用FPGA资源来实现流水线设计,从而提高系统运行速度。

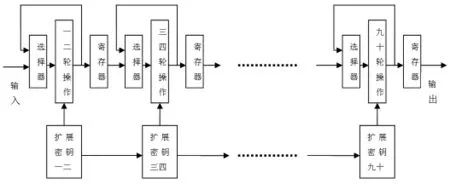

具体实现为将原来的0-10轮循环迭代结构进行分解。第0轮只是实现了Add Round Key操作,可以使用单独的“异或电路”加以实现。将剩下的1-10轮通过2轮一组,组内循环的方式设计为5级流水线结构。如图1所示。

图1 AES算法5级流水线结构

由于1-9轮的运算模式与第10轮存在不同,因此将第9轮和第10轮作为一组在控制上要使用不同的控制信号。通过状态机来对两轮的控制信号赋不同的值。而1-8轮的的运算模式是相同的,即其控制信号也是相同的。因此前4组流水线可以使用一组固定的控制值。

本设计是组内循环与轮间流水相结合的模式,必须要解决好输入的问题,即要协调好来自上一级流水线的输入数据与本级流水线循环反馈的数据,使系统正常工作。这里通过设计一个2选1(MUX2_1)选择器来实现。选择器的使能信号也是由状态机来实现。

轮密钥的匹配输入问题。由于每级流水线包括两次加/解密的运算,而每次加/解密运算所需的轮密钥各不相同。要实现此操作就必须为每级流水线设置一个寄存器堆。寄存器堆中存放两次加/解密运算所需的不同轮密钥。对轮密钥的选择也是由状态机来实现。

4 结束语

本文提出了一种基于结构共享和多级流水线的AES算法实现方案。字节变换采用可重构设计,用同一组RAM资源在加解密时,分别加载Sbox表数据和Inverse Sbox表数据,节约了RAM资源。通过在列混合变换之前执行个逻辑电路(PreInvmix),来实现逆列混合变换。从而实现了逆列混合变换与列混合变换的结构共享。采用5级流水线结构设计,实现了芯片面积的节省和系统工作频率的提高。

[1]Federal Information Processing Standard (FIPS)for the Advanced Encryption Standard[J].FIPS-197.November 26,2001.

[2]武玉华,李艳俊,周玉坤.基于FPGA的AES_128密码算法实现研究[J].微计算机信息,2007(2).

[3]李雪梅,路而红,欧海文.AES算法的快速硬件设计与实现[J].电子技术应用,2006(5).

[4]吴晓成,高琳.AES IP Core的一种高速流水线实现方法[C].西安电子科技大学学术年会,2007.