基于FPGA的高精度数字移相信号发生器的设计

2012-08-15余水宝黄相平

黄 俊,余水宝,黄相平

(浙江师范大学 数理与信息工程学院,浙江 金华321004)

移相信号在电子、通信等科学研究领域有着广泛的应用,两个同频的移相信号又是电子行业继电保护领域中模拟、分析事故的一个重要手段,因此移相信号发生器是实验室和科研单位经常使用到的一个重要仪器设备。近年来,一种新的频率合成技术——直接数字频率合成(DDS)技术得到飞速发展。DDS技术是一种从相位概念出发直接合成所需波形的频率合成技术。它与传统的频率合成技术相比,具有频率分辨率高、频率转换速度快、输出波形灵活、相位变化连续等优点。随着微电子技术的发展,现场可编程门阵列(FPGA)器件也得到了飞速发展。由于该器件具有集成度高、可靠性强和现场可编程等特点,因此在数字信号处理中得到了广泛的应用,越来越受到硬件电路设计工程师的青睐。

本文介绍了一种基于FPGA的数字移相信号发生器的设计方案,频率范围1 Hz~10 MHz,相位差范围0°~359.5°,频率分辨率为 1 Hz,相位差分辨率为 0.5°,可输出方波、三角波和正弦波。该系统具有输出波形灵活、稳定性好等优点。

1 DDS原理

DDS主要由相位累加器、波形查找表ROM、D/A转化器和低通滤波器等部件组成,其原理框图如图1所示。图中,相位累加器在系统时钟的控制下以步长K作线性累加,其输出端可对波形查找表ROM寻址,波形查找表输出相应的波形数据,然后波形数据依次经过数模转换器和低通滤波器,最后输出平滑连续的波形。

设相位累加器的字长为N,频率控制字为K,系统的时钟频率为fc,则DDS系统输出波形的频率fout为:

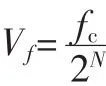

频率分辨率Vf为:

当系统时钟频率fc固定不变时,DDS的频率分辨率Vf完全由相位累加器的字长N决定。本系统中,fc=160 MHz,N=32,则频率分辨率 Vf≈0.372 5 Hz,因此 DDS的频率分辨率极高。

从原理框图可以看出DDS是一个开环系统,没有任何反馈环节,这种结构大大缩短了DDS的频率转换时间。

2 系统总体设计

本系统主要包括人机交互模块、单片机模块、基于FPGA的DDS模块、高速D/A模块和低通滤波器模块,系统整体框图如图2所示。其中人机交互模块包括液晶12864显示和键盘输入两部分,分别用于显示波形参数和实现用户对波形的调节功能。单片机模块一方面用于控制液晶显示和键盘输入,另一方面负责与FPGA进行通信。限于篇幅,本文主要介绍基于FPGA的DDS模块和高速D/A转换模块。

图2 系统整体框图

2.1 基于FPGA的DDS模块

基于FPGA的DDS模块是本系统设计的核心。首先值得说明的是,实现两路移相信号的直接数字频率合成有两种方案可供选择。方案一:使用同一相位累加器、同一起始地址,当移相角度发生变化时,发送不同波形数据到两个存储器,使输出信号产生相位差。方案二:在储存器中存放相同的数据,根据移相角度改变两个相位累加器扫描的起始地址。前者利用FPGA设计硬件电路简单,但偏重于软件,算法技巧性较强;后者对相位累加器的设计要求较高,考虑到FPGA内部的丰富资源,本系统采用方案二[1-2]。

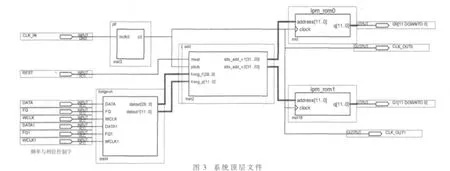

本系统采用Cyclone II系列的FPGA芯片EP2C8Q208C8为主控芯片,其内部最高处理速度达几百兆,内含两个锁相环倍频器(PLL)和 4 MB的 ROM,内部资源相当丰富。利用FPGA芯片设计的顶层文件Symbol File图如图3所示。其中pll为锁相环倍频模块,tongxun为FPGA与单片机通信接口模块,add为相位累加器模块,lpm_rom0、lpm_rom1为存储器ROM模块。

本系统输出信号的最高频率拟达到10 MHz,如果在一个周期内至少采样16个点,则扫描时钟频率至少要达到160 MHz。由于系统的有源晶振频率为 50 MHz,因此本系统充分利用FPGA内部的锁相环,输出160 MHz的高频信号作为系统时钟[3-4]。

2.1.1 与单片机通信接口模块

为了将频率控制字与相位控制字输入给FPGA,本系统利用单片机对其进行送数。首先考虑到单片机与FPGA电平匹配的问题,本系统选用STC12LE5A60S2单片机,其工作电压范围为2.2 V~3.6 V。

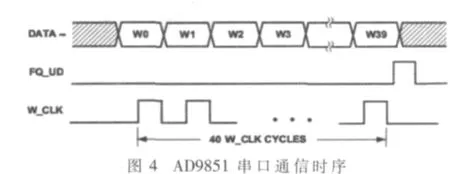

为了使FPGA与单片机正常通信,本系统仿照AD9851的串口通信模式,其时序如图4所示。在写时钟W_CLK的控制下,40 bit控制字依次从低位到高位被读入,最后FQ_UD端产生一个上升沿,表示将40 bit控制字加载到AD9851内部寄存器。

本系统设计了两组串口通信接口,一组用于接收30 bit的频率控制字,另一组用于接收12 bit的相移控制字。通过设计硬件描述语言,创建Symbol File。

2.1.2 相位累加器模块

通过设计硬件描述语言,创建相位累加器Symbol File。该累加器的字长为32,当复位信号reset为1时,在时钟pllclk控制下每来一个脉冲累加器以步长K(kong_f)累加,高 12位(31 downto 20)累加结果输出作为ROM地址,当K发生变化时输出频率也相应改变。累加器的初值为K1(kong_p),当K1改变时累加器输出结果也相应改变,从而使两个存储器的地址不同而形成相位差。

2.1.3存储器ROM模块

本系统考虑到输出信号的光滑度和FPGA的资源,设计4 096个点为一个周期,因此设计了两个12 bit(4 096 B)的 ROM。本系统创建的存储器 ROM Symbol File,clock为基准时钟,address[11..0]为地址输入端,q[11..0]为波形数据输出端。

2.2 高速D/A转换模块

由于本系统输出两路频率相同而相位不同的移相信号,因此需设计两组高速D/A转换电路。该电路采用转换速率为 165 MS/s,分辨率为12 bit的高速 D/A转换芯片,其具有转换速度快、控制方便、输出波形误差小等优点。考虑到DAC902为差分电流输出型,差分电流最大值是20 mA,输出端接 100 Ω电阻,所以通过电压反馈型高速运算放大器OPA690得到差分电压。

3 系统测试

系统上电后通过Gwinstek GDS-2102数字存储示波器测试并记录实验结果。

图5所示为信号源输出频率为1 kHz,两路信号相移分别为 45°、90°、180°、270°时, 使用示波器观察并用U盘拷贝的输出波形。

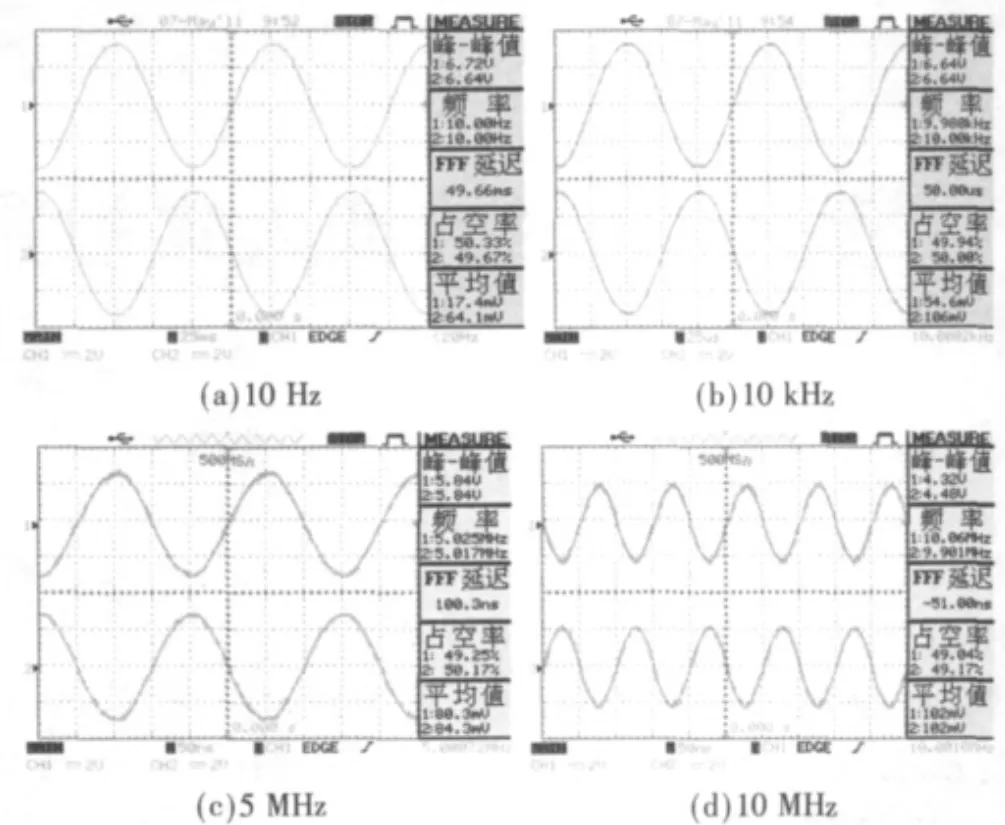

图6所示为信号源输出相移 180°、频率为 1 MHz,频率相移分别为 10 Hz、10 kHz、5 MHz、10 MHz 时, 使用示波器观察并用U盘拷贝的输出波形。

表1为同相移下根据不同频率值测得的实际频率值。

本系统通过选用Cyclone II系列的FPGA芯片EP2C8Q208C8和STC12LE5A60S2单片机实现了数字移相信号发生器的设计。可产生频率范围为1 Hz~10 MHz,且频率、相位均可调的方波、三角波和正弦波。由于本系统采用DDS算法,因此能在频率、相位上实现高精度的控制。实验结果表明,本系统具有频率分辨率高、频率转换速度快、输出信号噪声低和系统稳定性好等优点。

表1 频率测试数据(相移 180°,空载)

[1]李辉,朱林生.基于FPGA的三相函数信号发生器设计[J].电子科技,2010,23(7):87-91.

[2]舒俊,陈希,余水宝.零误差低频程控三相相移信号发生器[J].仪器仪表学报,2009,30(6):796-797.

[3]周绍军.基于DDS技术的高精度双路可移相波形信号发生器设计[J].西南民族大学学报,2010,36(5):822-826.

[4]赵茂泰.电子测量仪器设计[M].武汉:华中科技大学出版社,2010:148-153.