基于FPGA的高性能视频信号采集系统设计与实现

2012-08-15徐国强

徐国强,张 萌

(江苏自动化研究所,江苏 连云港222006)

近年来,伴随着计算机技术、图像处理技术、网络技术和多媒体技术的发展普及,兴起了数字化视频处理的浪潮。随着数字图像处理技术和数字电路技术的发展,利用高性能处理器实现数字视频信号采集与显示系统已成为现实[1]。数字视频信号采集与处理系统符合信息产业的未来发展趋势,蕴含着巨大的商机和经济效益。

由于FPGA本身功能强大,使模块具备良好的可扩展性,可以在不修改硬件设计的情况下通过修改FPGA逻辑,提供更加丰富的功能[2]。

本文采用Xilinx公司的FPGA与一些外围器件实现一种数字视频信号采集模块。介绍了FPGA逻辑的实现、驱动程序开发的过程以及模块的调试记录与经验。

1 设计原理

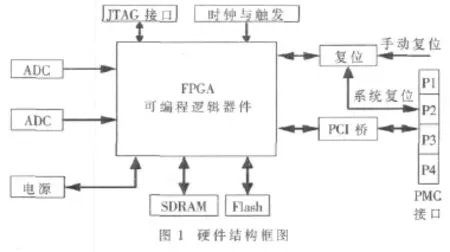

系统主要由ADC模块、时钟电路模块、存储模块、接口模块以及可编程逻辑控制模块组成,系统总体框图如图1所示。

系统由PMC连接器供电,完成64 bit、66 MHz或者32 bit、33 MHz PCI数据通信;系统由两路A/D采集器、时钟电路、SDRAM存储器、Flash存储器和PMC接口电路实现。FPGA是整个模块的核心,所有信号围绕FPGA输入输出。来自系统的复位信号和手动复位一起作为FPGA的复位源。电源经过转换模块转换以后,提供给FPGA使用。FPGA时钟信号本板产生。模块上设置了JTAG接口和E2PROM接口。PCI接口采用PMC规范接口。

2 实现方法

2.1 器件选型

设计通信接口模块时,为了提高设计的集成度以及灵活性,采用FPGA来实现。FPGA实现功能包括:PMC接口、中断以及控制寄存器、2路模数转换接口、外部存储器接口。因此要选用资源丰富、速度较快、RAM容量较大的FPGA。Xilinx公司Virtex-4系列完全可以胜任上述工作,在Virtex-4器件中,含有特定的硬件知识产权(IP),支持多种主要协议,包括 PCI,其内嵌的RAM可以作为FIFO或者双口RAM使用,此外还具备丰富的资源。综合考虑,FPGA采用Xilinx公司的XC4VSX35。

2.2 PCI接口电路

本系统中采用PCI9656作为PCI接口芯片,此芯片为PLX公司生产的比较新的产品。PCI9656支持64 bit、66 MHz的 PCI总线和 32 bit、66 MHz的 Local总线接口,兼容PCI R2.2规范,支持PICMG 2.1 R2.0热交换功能,支持三种局部总线类型:M模式、C模式和J模式,支持异步的PCI和Local总线时钟,支持三种数据传输方式:Direct Master、Direct Slave和DMA,寄存器向下兼容PCI9054、PCI9056、PCI9060和 PCI9080 等。

2.3 模数转换器电路设计

A/D的选择既要考虑A/D自身的性能又要满足系统所要求的动态范围和性能指标。评价A/D转换器的性能指标主要有:A/D转换位数、无寄生动态范围(SFDR)、信噪比(SNR)、转换速率、量化灵敏度等。一般来说,A/D的转换位数越高越好,转换位数越多其动态范围就越高。

AD6645芯片是美国ADI公司生产的高速、高性能单片模数转换器,是一种性能优良、具有14 bit分辨率、105 MS/s抽样率的模数转换器,是继AD9042、AD6640、AD6644之后的第四代宽带ADC产品[3]。其原理框图如图2所示,主要特点有:

(1)中频采样率可达 105 MS/s;

(2)多音无杂散动态范围(SFDR)为100 dB;

(3)采样抖动 0.1 ps;

(4)芯片功耗 1.5 W;

(5)差分模拟输入。

2.4 复位电路

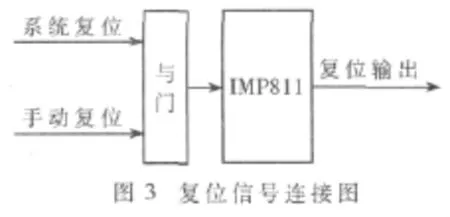

模块复位电路原理如图3所示。

模块电路中有两种复位情况:手动复位和系统复位。系统复位信号与手动复位输入相遇,作为复位器件的输入,其输出作为FPGA复位输入信号,保证在主机侧出现冷复位和要求本板单独复位的情况下,所有的器件都处于复位状态。

2.5 时钟电路

FPGA有2路输入时钟,分别是66 MHz和100 MHz由外部晶振提供的PCI总线时钟和FPGA系统内部工作频率。

2.6 电源电路

由于模块中存在对噪声敏感的ADC采样电路等模拟电路,故数字电路部分可以采用DC-DC电路来完成供电,选取 Linear公司的 LTC3545作为 1.2 V、1.5 V、1.8 V电压转换芯片,其具有95%以上的转换效率、2.5%以下的纹波电压等特点[4];而模拟电路部分的ADC电路需要特别对噪声等干扰做滤化处理,故选取德州仪器(TI)的UCC284作为-5 V的电压转换芯片[5],将PMC接口的-12 V电压作为UCC284的输入,UCC284具有非常好的性能,线性调整为5 mV,负载调整率在0.1%。

3 FPGA设计

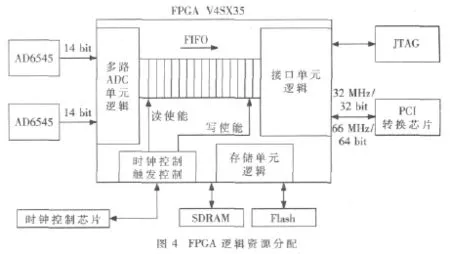

Xilinx公司的XC4VSX35可编程控制器逻辑代码是整个系统的核心,系统逻辑结构如图4所示。

FPGA代码设计主要分为时钟模块、模数转换通道1、模数转换通道2和PCI接口四个模块。

在顶层模块,主要进行各模块的端口映射以及相关信号的赋值和取值工作。时钟模块将几路时钟的输出校正到预定的频率上,模数转换时钟 100 MHz,FPGA工作时钟100 MHz等。模数转换通道1、模数转换通道2在电源和时钟正常的情况下不断向FPGA提供采样数据,同时FPGA对两路ADC及其相关的FIFO进行设置,包括FIFO的深度以及读写的阈值都对DMA传输具有重要的作用。PCI接口模块主要由FPGA与PCI9656的接口代码组成,包括总线的数据命令操作,PCI9656接受上位机PC驱动对它的设置后工作于J模式(LAD地址数据复合使用),通过上位机对PCI9656寄存器的设置,可使其工作于DMA模式,相关的寄存器在下节介绍。根据Local Bus的时序描述,FPGA作为Local Bus的从设备一直工作在命令等待状态,并对接收到的命令数据进行解析后做出相关的动作。

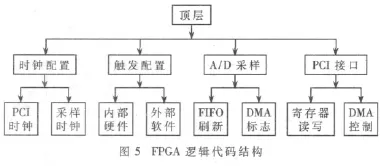

系统FPGA逻辑代码的整体结构如图5所示,A/D系统在上电后首先校正时钟,保证PCI9656和ADC采样能够正常运行,然后通过PCI9656的局部总线查询其内部寄存器,确定系统采用的触发方式是采用内部硬件触发还是外部软件触发,若采用内部硬件中断,则将内部硬件100 MHz时钟进行8分频,即生成12.5 MHz时钟以供ADC后端的锁存器时钟输入端使用;与此同时本板上的ADC采样工作在一直进行着,同时刷新FPGA内部生成的FIFO,鉴于ADC采样的 14 bit数据和Local总线的 32 bit宽度,生成 32 768×32 bit(Local端)和 65 536×16 bit(ADC锁存器端)即128 KB大小的FIFO缓冲区,逻辑上将14 bit采样数据扩充为16 bit数据以便数据处理和传输,通过空和满的信号量控制PCI总线上的DMA工作。另外系统中的PCI9656逻辑控制单元负责完成Local总线端的读写,包括寄存器的读写和DMA操作的执行。

4 采样数据分析与验证

系统工作过程中产生一个数据文件用于保存视频采集的数据,将数据通过Matlab工具绘出采样到的数据波形,如图6所示。从图中可以看到,系统采样的16 bit数据,采样值在-32 768~32 767之间,横坐标表示采样的点数共 5×105, 而硬件时钟为 100 MHz,AD6645采样电路输出的数据通过锁存器送给FPGA处理,锁存器的使能信号为8分频的时钟信号,可以得出12.5 MHz的采样频率,一次采样2 B数据,波形中一个点表示1 B的数据,故可知5×105点表示采样时间为40 ms,正好是两行 PAL信号的时间,符合 PAL的标准[6],验证信号采集结果正确。

将图6中两行波形放大,可以看到此图中显示的是一行信号完整波形的部分图形,需要5个前均衡脉冲、5个同步高脉冲、5个后均衡脉冲和17个色同步消隐脉冲,然后是285.5行,同时在试验中发现,若一次 DMA数据包长太小,将导致采集的数据不完整,无法正常显示;若一次DMA数据包长太大,每次传输之间的间隔时间比一次DMA传输数据的显示时间长得多,图像显示会有间隔,导致无法正常显示。因此,系统设计中每次DMA数据包长要视DMA的传输时间和显示时间而定。

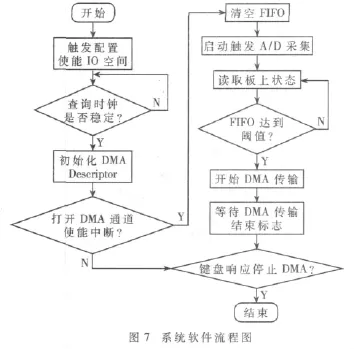

5 软件设计

上位机先初始化PCI9656芯片,查询状态寄存器(StatusReg)中时钟是否稳定,即时钟稳定状态位是否为1,当AD时钟稳定后,查询 FIFO是否采集满,如果状态寄存器中通道1状态位为1,则表示通道1的FIFO数据已满,然后初始化一个Descriptor用于进行DMA传输,然后发起Scatter/Gather模式DMA[7]。系统软件运行流程如图7所示。

以读取通道1数据为例,具体的初始化流程如下:

(1)对PCI9656使能IO空间读写;

(2)读取时钟稳定状态位,如果ADC时钟工作稳定,继续进行下一步的工作;

(3)初始化一个Descriptor的结构体设置,用于进行DMA传输;

(4)打开DMA通道,设置DMA传输结束中断使能DMA Scatter/Gather模式;

(5)清空模数转换通道1的FIFO;

(6)触发AD通道1数据采集启动;

(7)读取状态寄存器以确定板上状态;

(8)如果FIFO已满,则设置DMA相关寄存器,开始DMA传输;

(9)等待中断,查询DMA结束标志位有效,确定一次DMA传输完成;

(10)重新初始化Descriptor,以进行下一个DMA操作,重复步骤(4)以后的过程。

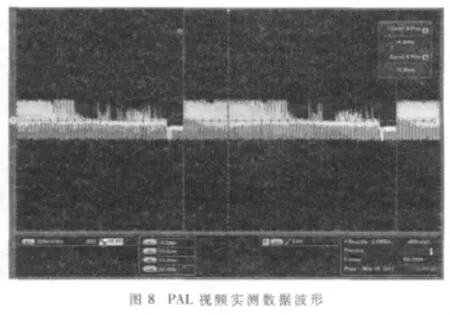

6 模块的调试及性能

模块设计完成后,在基于PMC接口的CompactPCI总线架构的工控机箱内对其进行测试。利用外部设备和通讯接口模块进行通讯,然后实测视频数据波形,如图8所示。

分析结果显示模块工作正常,与采样的数据波形一致,达到了设计要求。

本设计充分体现高性能视频信号采集与显示系统的工作特点,整个设计结构紧凑,性能稳定,抗干扰能力强,并且适用于各种工业控制场合。本设计已经在工业控制环境下多次应用,在不同主机环境下运行测试程序,经长时间考核,A/D采样数据传输速率稳定,模块运行稳定可靠。

[1]钱敏,李富华,黄秋萍,等.基于HDL的PAL制数字视频图像采集控制器设计[J].微电子学与计算机,2007,24(12):191-194.

[2]孟宪元,钱伟康.FPGA嵌入式系统设计[M].北京:电子工业出版社,2007.

[3]Analog devices.AD6645 datasheet[EB/OL].[2003-02-20].//http:www.Analog devices.com.

[4]Linear technology.LTC3545 datasheet[EB/OL].[2008-01-30].www.Linear technology.com.

[5]Texas Instruments.UCC284 datasheet[EB/OL].[2000-01-30].//http:www.Texas Instruments.com.

[6]赵坚勇.电视原理与接收技术[M].北京:国防工业出版社,2007.

[7]PLX Tech.PCI9656 datasheet[EB/OL].[2009-01-28].//http:www.PLX Technology.com.