音频信号数字化光纤传输实验仪信道的设计与实现

2012-08-14尹华山陈保林

钱 皓, 成 龙, 孙 立 , 尹华山, 陈保林

(1.南京航空航天大学 自动化学院,江苏 南京 211100;2.南京航空航天大学 理学院,江苏 南京211100;3.南京航空航天大学 机电学院,江苏 南京21110)

随着光纤技术的不断发展,光纤的应用越来越广泛。光纤以其频带宽、容量大、衰减小等优点给通信领域带来的改革和创新,形成了一个新兴产业。数字通信对比传统的模拟通信有精度高、灵活性高、可靠性强、易大规模集成、时分复用、功能稳定等优点而被广泛的应用在工业、医疗、军事等诸多领域[1]。数字光纤通信兼有两者的优点,必将成为通信领域的发展方向。

音频信号的光纤传输有快速、准确、信息量大、质量高的优点。在实验领域,可以快速准确的传递声音信号,给实验者更可靠的信息。在应用领域,可以实时、长距离传递声音,即节约成本,又有高的传输质量。因此,音频信号的光纤传输的研究与实现,将方便人们的学习、工作和生活[2]。

文中是针对普通高等工科类学校中非通信与信息等专业学科的普及性实验教学科目所研制的《音频信号的数字光纤通信实验仪》创新实践项目。教学科目及实验仪器的推出,有利于帮助高等学校基础性学科实验课程的提升,丰富与完善实验课内容,使学生了解现代技术的发展与相关知识的掌握。

1 系统的硬件结构

信号通道由两大部分组成:光接收器和光发射器。两者之间以光纤连接。光发射和光接收器的工作原理相互关联,一个是另一个的逆过程;光发射器是将音频的电信号转变成光信号,光接收器是将光信号转变成音频的电信号[3]。

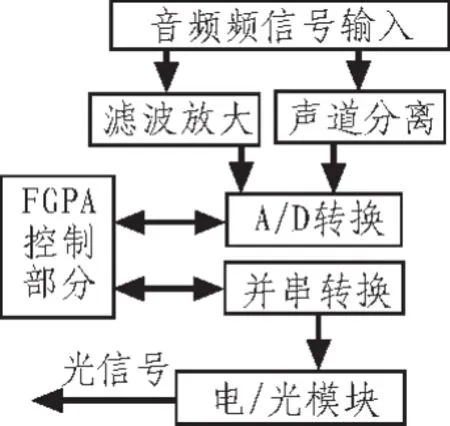

光发射器由以下几个电路模块组成:滤波放大、A/D转换、控制部分、并/串转换、电/光模块部分[4]。

图1 发射器原理框图Fig.1 Optical emitter functional block diagram

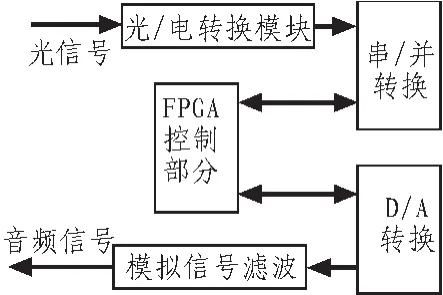

光接收器由光/电转换部分、串/并转换、控制部分、D/A转换、模拟信号放大部分组成[4],如图2所示。

图2 光接收器原理框图Fig.2 Optical receiver functional block diagram

2 系统电路设计

2.1 电 源

整套电路仅以12 V直流电源供电,内部集成电路需用到5 V、3.3 V、1.5 V的电源。5 V电源由L7805三态稳压电源提供,3.3 V和1.5 V分别由ASM117-3.3和ASM117-1.5提供。

2.2 FPGA的数据处理及实时控制部分

电路采用型号为EP1C3T100C8的FPGA为主控芯片,直接由18.432 MHz的晶振提供工作时钟。芯片共有两个时钟输入端,选其一输入晶振时钟。由于FPGA各个模块都用到,所以各个模块都需要供电和接地。

FPGA内部有一个锁相环,可以进行分频和倍频,以得到不同的频率。发射器中模数转换芯片和并/串转换芯片的时钟由FPGA提供。由于模数转换后输出串行的二进制数据,而并/串转换器的数据输入为10位,所以需要在FPGA中进行编码。编码应尽量避免多个“0”和“1”连续出现,采用8B10B编码方式。FPGA内部先将串行二进制数据分解为8位并行数据,再经过8B10B编码输出。接收器中FPGA提供数模转换器工作时钟和串并转换器的参考时钟,并将串并转换器输出的十位数据解码,还原为八位数据传输给数模转换器。FPGA的功能由Verilog编程实现,程序采用AS(主动)配置方式下载到FPGA[5-6]。

2.3 音频信号的处理及采集

音频信号经声道分离、滤波、放大,由模数转换集成芯片采集转换成数字信号。

2.3.1 滤波放大部分

在对音频信号进行采样时,当信号中含有大于二分之一的采样频率,如果采样频率不够高,就会产生混叠信号。混叠信号不能用数字滤波方法除去,需要用硬件滤波。A/D转换的采样频率需要高于音频信号最高频率的2~10倍。根据所需音频信号的带宽以及抗混叠滤波所需要的特性,设计一个二阶的低通有源滤波器,截止频率大于或等于20 kHz,设计电路如图3所示。

同时,该电路具有隔离放大作用,集成运放采用的是单电源供电的LM324。这是一款四运放集成、功耗低、电压工作范围宽的放大器。它具有内部补偿的能力和较低的输入偏置电流。工作于5 V电源时具有1.2 MHz的带宽[7]。由于音频信号是两路输入 (或多声道),且人耳能够分辨的声音带宽为20Hz~20 kHZ,所以LM324足以满足要求。电路如图3所示,此为单侧声道,另一声道与其相同。

图3 音频滤波放大电路图Fig.3 Audio filter circui

图中LM324采用5 V电源供电,一级放大。信号输入时要加入一定的电压偏置。

2.3.2 A/D转换部分

模数转换电路采用了Cirrus Logic公司出品的专业音频处理集成芯片CS5342,其工作时钟频率设定为18.432 MHz,由FPGA提供。信号由AINL和AINR管脚输入,SDOUT输出转换后的串行二进制数据,LRCK和SCLK输出采样频率。M0和M1脚分别接高、低电平,以保证芯片工作在双倍速主动模式上,分频产生采样频率96 MHz。另外,RST脚置高电平,各类参考电压引脚加入适当的滤波电容,使芯片稳定且正确地工作。其电路如图4所示。

图4 A/D转换电路图Fig.4 A/D converter circuit

2.4 信号发送部分

由FPGA处理后的数据要通过光纤发送,需先将并行数据转换为串行数据,再将串行数据转换为光信号。

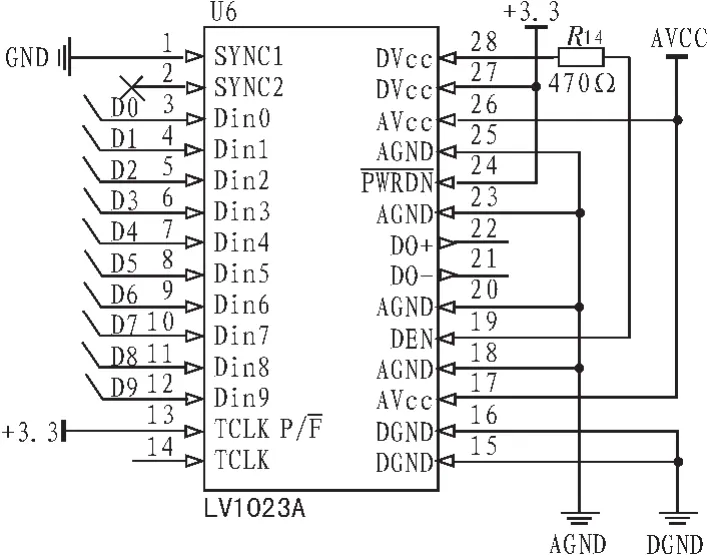

2.4.1 并/串转换

电路采用串化器SN65LV1023A集成芯片实现,电路如图5所示,其对应接收端由解串器SN65LV1224A集成芯片完成。SN65LV1023A可以将10位并行数据转换为串行差分数据流,该差分数据流可以由SN65LV1224A还原为10位的并行数据。这一组芯片内部有锁相环,可以为数据输出自己匹配时钟。串化器SN65LV1023A参考时钟选为18.432 MHz与,数据在该时钟频率下输入,其芯片内部匹配产生数据输出时钟,每一个10位并行数据转换为12位串行数据,其中多出一个起始位和一个终止位,所以有效频率为184.32 MHz。解串器的参考时钟也定为18.432 MHz,以满足数据传输需求。

由于音频信号是实时不断的,所产生的数据流连续进行,所以电路不能设置进入高阻态或省电模式,因此LV1023的DEN和PWRDN都置高电位。

串行数据的准确传输需要串化器和解串器同步,该组芯片采用的是随机同步方式。串化器的SYNC1和SYNC2悬空。解串器的LOCK输入到FPGA以对数据传输进行实施控制。

图5 并/串转换电路图Fig.5 Parallel/series converter circuit

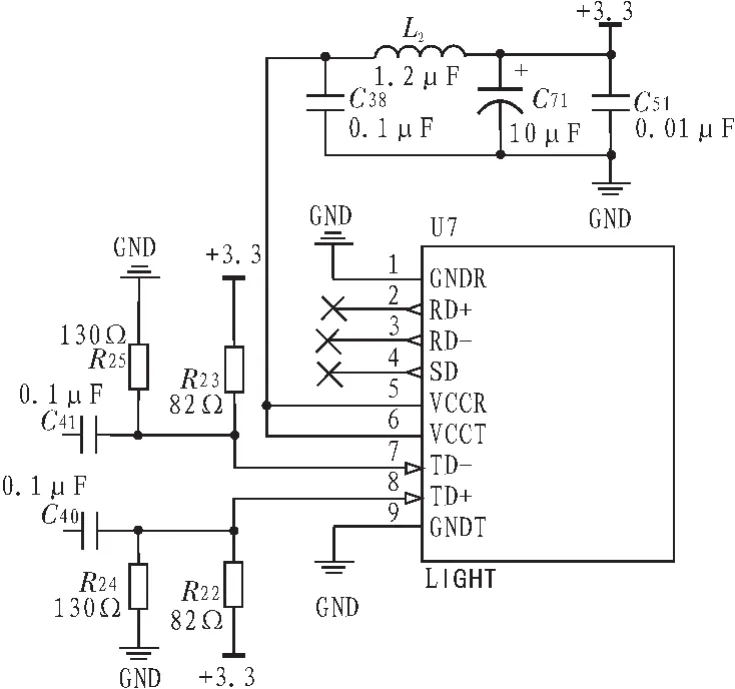

2.4.2 电/光模块

采用型号为HNMS-XEMC41XSC20,工作波长在T1310nm/R1550 nm的单纤双向一体化收发模块,将电信号差分数据流转成光数据信号流[8-9],电路如图6所示。

图6 光发射模块电路图Fig.6 Optical emitter circuit

2.5 信号的接收及处理

2.5.1 光/电转换模块

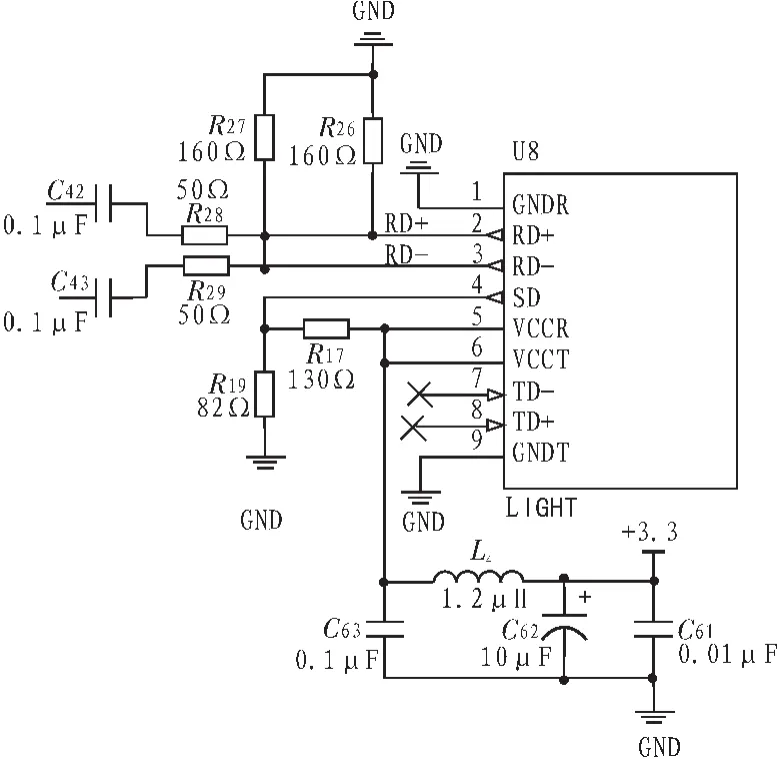

该实验装置以单纤进行信号传输,光信号传输到接收装置后,需要还原为电信号,即差分电压数据流。采用型号为HNMS-XEMC41XSC20,工作波长在T1310nm/R1550nm的单纤双向一体化收发模块,将光信号转换为电信号[8]。转换后的差分信号由RD+和RD-输出,电路如图7所示。

2.5.2 串并转换

串并转化装置采用与发送器中的串化器SN65LV1023A相匹配的解串器SN65LV1224A。发送器中的串化器将10位的并行数据转换为串行的差分数据流,因此在接收器中需用相应的解串器将串行差分数据流还原为并行数据。

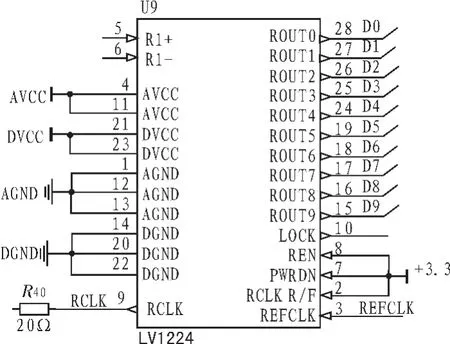

图7 光电转换电路图Fig.7 photoelectric converter circuit

SN65LV1224A内部有锁相环,在接收数据流时可以根据数据的频率自行匹配接收时钟,外界只需为其提供参考时钟。此处参考时钟选为18.432 MHz,由FPGA控制部分提供。芯片还匹配了与解串后的数据同步的时钟,以助于转换后的并行数据输出。为了保证音频信号的连续性和实时性,需避免芯片处于省电模式或高阻模式。因此PWRDN和REN需接高电平。RCLK-R/F接高电平,即选择时钟上升沿输出数据。电路如图8所示。

图8 串/并转换电路Fig.8 Series/parallel converter circuit

该组芯片有两种同步方式:快速同步和随机同步。快速同步是由串化器发送一组由连续的6个“1”和“0”组成的同步信号,解串器收到信号后锁定数据时钟,锁定完成之前LOCK保持高电平,同步完成后跳变为低电平。同步信号的发送是由串化器的SYNC1和SYNC2控制的,只要两者之一置高电平持续时间超过6个时钟周期,串化器就开始连续发送同步信号。快速同步具有快速准确的优点,但在长距离的信号传输中,光纤只传递数据,无法很好的传递串化器和解串器的SYNC和LOCK信号。因此采用随机同步方式。

随机同步方式串化器不需发送同步信号,解串器直接对数据流进行锁定,实现同步,锁定丢失后,解串器会重新锁定时钟。将LOCK接到FPGA以进行实时控制。

2.6 D/A转换及视频信号输出

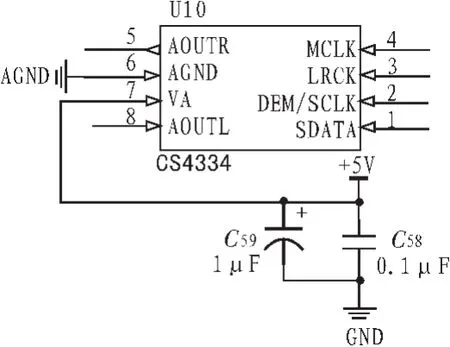

D/A转化部分采用Cirrus Logic公司出品的专业音频信号处理芯片CS4334。其具有完善的立体声DAC系统,抗干扰能力强,失真噪声小,采用单电压+5 V电源,电路如图9所示。

图9 D/A转换电路图Fig.9 D/A converter circuit

芯片具有两种时钟模式,即外部串行时钟模式和内部串行时钟模式。当芯片工作在外部串行时钟模式下时,去加重滤波器不能被访问,且外部串行时钟易被干扰,故本装置设计时采用了内部串行时钟模式。串行时钟SCLK在内部产生,并与主时钟 MCLK(18.432 MHz)、采样时钟 RLCK(96 KHz,由FPGA分频产生)同步。信号经数模转化后,分别由AOUTL和AOUTR输出左右声道模拟信号,经低通滤波后输出,由于满量程时信号最大输出可达3.5 V,且装置可通过外接放大器进行声音信号的放大,故在本设计中未进行音频信号的放大处理。

3 软件设计及仿真介绍

系统采用VerilogHDL语言进行程序编写,在QuartusⅡ环境下编辑仿真。FPGA内部时钟由18.432 MHz的有源晶振提供。FPGA的工作是:

1)提供D/A转换芯片CS4334,A/D转换芯片CS5342,并串转换芯片LV1023的工作时钟和串并转换芯片LV1224的参考时钟,其值均为18.432 MHz。

2)发送端对数据进行8B10B编码,并将转换后的数据传送给串化器;接收端获取串并转换后的十位数据,进行解码,还原为编码前的八位数据,并将解码后的数据传送给数模转换芯片。

3.1 8B10B编解码

8B10B编码是目前高速串行通讯普遍采用的编码方式,8B10B编码的目的是将八位数据转换成10位的数据,并使转换后的数据流中“0”和“1”的数量平衡,避免发送过程中因过多重复的出现“0”或“1”而发生的错误,提高线路传输的性能,有利于接收器更准确的捕捉同步时钟,而且采用特定的码元可以使接受端更准确地对准码元。8B10B编码可以看成是5B6B和3B4B编码的组合,组合过后有些编码可能有两个值,“1”和“0”的差值称为平衡度,用RD-表示平衡度为+2或0,RD+表示平衡度-2或0。将转换后的数据按平衡度分为RD-和RD+两列。设变量DISPIN表示正在转换的数的平衡度,DISPOUT表示下一个转换的数的平衡度。初始时设DISPIN与DISPOUT相等,先从RD-中开始转换,如果转换后的数“0”和“1”的数量相等,继续在RD-列中转换下一个数,如果“0”和“1”的数不等,则转到RD+列中转换。同理在RD+列中,如果“0”、“1”个数相等则继续在 RD+中,否则换到 RD-中。

图10 8B10B编码流程Fig.10 8B10B coded flow path

解码部分将10位数据的前六位和后四位分别按照5B6B和3B4B的列表解码即可。

3.2 仿 真

设计程序经QuartusⅡ综合器编译综合成功后,可以对输入数据、中间产生的数据、输出数据进行仿真。装置采用的8B10B编码方式,分为3B4B和5B6B进行编码。解码部分依照编码时相同的分发将十位数据分为4B和6B分别解码。解码后再按顺序组合成8位数据。程序以4B3B、6B5B分别查表的方式实现。程序仿真图中,adin是编码之前的八位数据,设为逐次加一的计数数据,为了方便比较,图中用十进制表示。编码后的十位数据为data10b,adout是解码后的数据。可以看到虽有延迟,解码后数据仍为计数数据,因此程序可以准确地实现解码功能。

图11 8B10B程序仿真图Fig.11 8B10B software simulation diagram

4 结束语

综合以上设计的电路模块,其基本功能实现了音频信号的采集与数字化处理,并用光纤完成音频数字信号的传输过程,其信号通道研制完成,为整套实验装置的设计研制奠定了基础保证,它是系统的核心关键部分。

作为大学基础实验领域研发的新型实验仪器,不管是设计研制者,还是通过其实验教学的应用者都在其工作与实验的实践中,学习掌握和了解多方面的专业理论与技术知识:1)认识模拟电路、数字电路、模数和数模转换等电子电路知识,了解印刷电路板设计方法;2)了解可编程逻辑器件的基本原理、硬件设计、软件编程、仿真调试与使用工作方法;3)了解模拟信号与数字信号的区别与特点,掌握二者之间对应关系及转换原理;4)了解音频信号构成、处理及传输过程,以及并/串、串/并转换的原理及同步工作方法;5)了解光/电和光/电转换专业知识与当代应用技术;6)学习和了解模拟信号与数字信号光纤传输过程等现代电子专业理论与应用技术。

[1]彭妙颜,周锡韬.数字音频设备与系统工程[M].北京:国防工业出版社,2006.

[2]李亮,胡一梁,韩瑞珍.基于FPGA的数字光端机的设计[J].中国有线电视,2008(9):955-957.LI Liang,HU Yi-liang,HAN Rui-zhen.Based on FPGA digital lightendmachinedesign[J].ChinaCableTV,2008(9):955-957.

[3]邱昆,王晟,邱琪.光纤通信系统[M].成都:电子科技大学出版社,2005.

[4]顾生华.光纤通信技术[M].2版.北京:北京邮电大学出版社,2008.

[5]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天出版社,2003.

[6]周润景,苏良碧.基于QuartusⅡ的数字系统VerilogHDL设计实例详解[J].EDA应用技术,2010:20-22.ZHOU Run-jing,SU Liang-bi.Based on QuartusⅡthe number system VerilogHDL design example explains in detail the[J].EDA Application Technology,2010:20-22.

[7]兰吉昌.运算放大器集成电路手册[M].北京:化学工业出版社,2006.

[8]方志豪,朱秋萍.光纤通信原理、设备和网络应用[M].武汉:武汉大学出版社,2004.