嵌入式机器视觉系统图像处理和传输接口设计

2012-08-14邱永华

邱永华

(广东女子职业技术学院,广东 广州 510450)

0 引言

随着自动化程度的不断提高,机器视觉的应用在制造业的生产过程中日益广泛。例如:在产品的质量控制中,可以对机械零件的外观、产品包装的正误、电路板焊接的好坏和IC字符印刷的质量等进行检测。应用机器视觉来代替人工检测,可以大大提高生产效率和检测的可靠性,减轻工作人员的劳动强度。机器视觉还可以完成人工检测难以快速完成的工作,获得准确的检测数据,比如零件的宽度、圆孔的直径以及基准点的坐标等。

机器视觉系统根据硬件平台的不同大致分为:基于PC的机器视觉系统和嵌入式机器视觉系统。前者开发周期短,开发成本较低,但局限于PC机的应用;后者则具有高度的灵活性,使机器视觉技术的应用领域大大扩展。所以,进行嵌入式视觉系统的研究具有实际意义和广阔的应用前景。

1 系统总体设计

1.1 系统设计目标

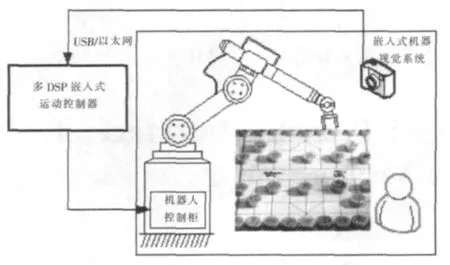

本文研究的嵌入式机器视觉系统是人机对弈智能化机器人系统的子部分。机器人系统包括3个部分:机器视觉系统、多DSP嵌入式控制器和6自由度机器人。机器视觉系统采集棋盘信息,进行识别并将识别结果发送到多DSP控制器系统,再用控制器系统来控制机器人落子下棋。系统结构如图1所示。

图1 人机对弈智能化机器人系统

机器视觉系统包括图像采集部分、图像缓存部分(包括CPLD:复杂可编辑器件总线接口)和图像处理部分。图像采集部分要求CMOS图像传感器接收到采集命令后能够以视频和快照两种模式采集图像数据,并配合行、场同步信号输出数字数据。CPLD构成的总线传输接口对前一个部分输出的数据进行时序和位数的处理,能准确地采集一行或一帧数据并以直接内存存取 (DMA)的方式将其保存到指定的RAM中。当保存完完整的一帧数据后,图像处理部分能从缓存中读取数据并进行处理,结果由USB或以太网口输出。本文重点介绍前面两个部分。

1.2 系统硬件布局

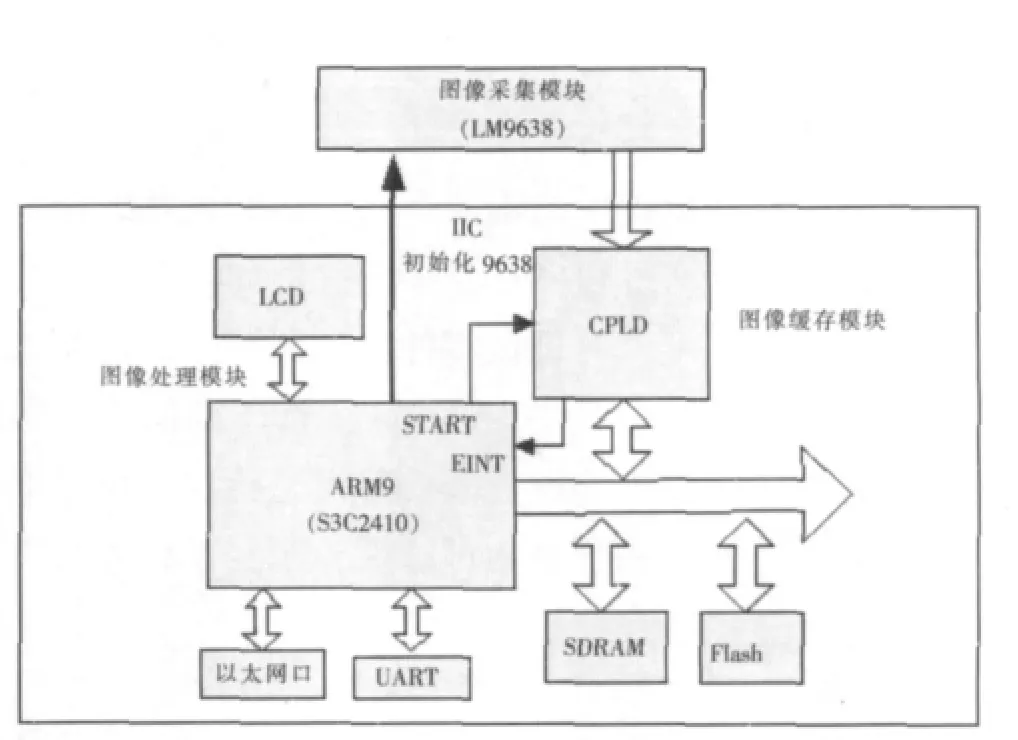

机器视觉系统硬件结构包括两个模块:CMOS模块和嵌入式处理器(ARM9)模块。CMOS模块主要包括LM629芯片及其外部电路,ARM9模块除了包括核心芯片SC2410和CPLD以外,还包括FLASH、RAM存储器,USB、串口和以太网口输出电路,以及电源和显示电路。ARM9模块上有CMOS模块的接线插槽,为CMOS模块提供时钟、电源和其它控制信号。CMOS模块能够根据不同的应用要求 (如不同的分辨率)而进行任意更换。系统的硬件布局如图2所示。

1.3 系统总体框图

ARM9通过I2C总线编程初始化和控制CMOS模块,对LM629的内部寄存器设定缺省参数,例如:对增益、对比度、亮度、清晰度、系数、曝光、时钟、水平窗口和垂直窗口的设置等。同时还控制CMOS模块图像采集的开始、暂停、结束等操作。CMOS模块在ARM9的控制下主要完成图像的采集,其采集的图像数据随着像素时钟、行场同步信号输出到CPLD构成的总路线接口。CPLD通过内部编程实现一行或一帧数据的准确采集以及16位数据到32位的转换处理。当采集到一定量的数据后发出DMA请求,ARM9交出总线控制权给DMA,CPLD和SRAM之间按设好的数据量和地址进行数据传输;当数据传输完毕,DMA将总线控制权交还给ARM9;完成图像数据的存储。ARM9将采集的图像数据与预存数据进行比较,通过相关的算法处理,找出二者的区别,获得当前所需的数据信息,通过USB或以太网口输出。系统总体设计如图3所示。

图3 系统总体设计框图

2 系统硬件设计

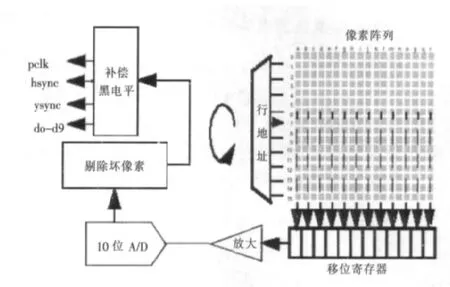

图4 LM9638图像数据输出示意图

2.1 图像采集模块的设计

图像采集模块即CMOS模块,它包括图像采集芯片LM9638及其外围电路和与ARM9模块接口的部分,主要功能是完成图像数据的采集,并将各种信号输出到相关的接口。接口信号包括:图像数据信号D0-D9、行场同步信号hsync和vsync、像元时钟信号pclk、I2C控制接口sda和sclk、主时钟输入信号mclk、复位信号resetb、下电信号PWD、使能快照信号Snapshort、外部事件同步信号extsync以及数字电VDD和数字地GND信号。

2.1.1 LM9638简介

LM9638是高性能、低功耗,0.84cmVGA CMOS有源像元传感器。用于获取静止或运动灰度图像并转换成数字数据流。具有视频和快照两种工作模式,有源像元阵列提供片内10位A/D转换器、固定图形噪声消除单元、视频增益。另外,内部集成了灵活的时序和控制单元使用户可以最大限度地调整积分时间、有效窗口尺寸、增益和帧频,还提供了多种控制、时序和电源模式。

2.1.2 LM9638图像数据输出硬件结构

LM9638输出为滚筒式曝光,即指以行为单位,对像素阵列进行信号采样、处理、输出。一行内所有像素的处理是并行的,各行间像素的处理是串行的。其处理一行像素的工作原理如下:开始积分时间时片内时序和控制电路将在一行时间内复位阵列中一行的每个像素,开始曝光,曝光时间到,时序和控制电路将给每行提供地址,同时传输像素积分值到相关的双采样电路,然后到移位寄存器。一但相关的双采样数据被装入移位寄存器,时序和控制电路将开始移出它们。像元数据进入模拟视频放大器。之后,通过增益来调整转换每个像素的模拟量为10位数字数据,最后经过剔除坏像素和补偿黑电平处理输出。如图4所示。

2.1.3 LM9638模块与ARM9模块的接口

LM9638模块与ARM9模块的接口如图5所示。

LM9638模块与ARM9模块除了有数据输出接口、I2C控制接口以外,还包括其它的信号:

a)mclk

传感器主时钟,由ARM9模块提供。

b)PWD

强制为逻辑1时传感器置输入电源下电模式。LM9638带有片内电源管理系统通过数字和模拟电路打开(Power up)和关闭电源(Power down)。 它可以用小于千分之一秒的时间使所有的电路上电。

c)resetb

强制为逻辑0时传感器复位至其缺省电源上电状态。

d)Snapshort

使能快照模式,实现LM9638采集单帧图像的功能,自动快照模式在收到Snapshort触发信号后,内部时序和控制电路将产生内部触发信号,在一行周期内复位阵列。当复位周期结束后控制电路将通过extsync脚产生外部事件同步信号。

e)extsync

外部事件同步信号,用于快照模式时同步外部事件。

LM9638模块3 V数字电和地输入。

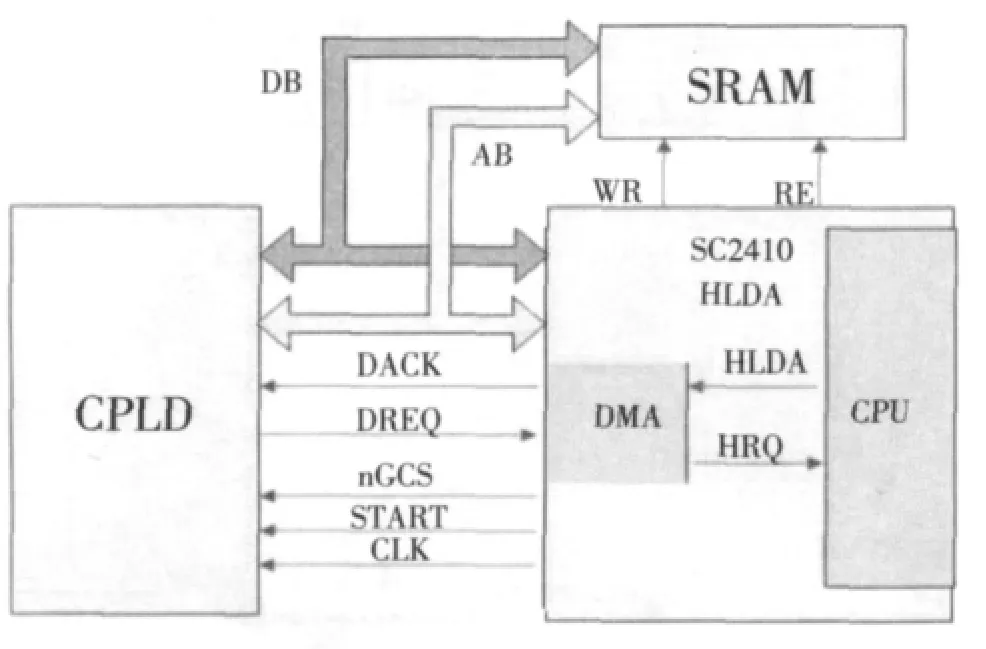

2.2 图像缓存模块的硬件设计

图像缓存模块把CPLD传输接口中的图像数据存储到SRAM中,数据在CPLD中进行位数转换完毕后发出DMA请求,ARM9响应DMA并将图像数据保存到SRAM,完成图像缓存。

图像缓存模块的硬件结构如图6所示。

图6 图像缓存模块的硬件图

DMA的特点决定了其适合图像缓存的功能。数据在不同的存储空间所转移的任务交给DMA来完成,而ARM只专注于数据的处理。虽然对图像数据进行的传输也可由软件实现,但将消耗掉大量的CPU时钟周期,使ARM的高速性能难以发挥。而由DMA来进行同样的工作几乎不占用CPU的时钟周期。下面是DMA进行图像数据存储的过程:

1)当CPLD将16位的图像数据转换成32位数据后,经过处理后的行同步信号或桢同步信号就向DMA控制器发出请求信号DREQ,且此信号在DMA释放总线权后才有效;

2)当DMA控制器采样到有效的DMA请求信号DREQ后,就向CPU发出总线请求信号HRQ;

3)DMA控制器向CPU发出总线请求信号HRQ后,至少再过一个时钟周期,CPU才能发总线响应信号HLDA,然后DMA控制器便可获得总线控制权;

4)DMA控制器获得总线控制权,向CPLD发出DMA的响应信号DACK;

刘铁头走后,我就去了李老黑家。李老黑刚吃过晚饭,正翘腿歪在沙发上剔牙。李老黑的老婆则木着脸坐在一旁的凳子上,看见我进门,只是翻了一下眼皮,没有答理我。

5)DMA控制器获得总线控制权后,控制数据在CPLD与SRAM之间传送,直到传送完预定的数据(一行或一桢);

6)DMA控制器的请求信号 (向CPU的)变为无效,CPU恢复对系统总线的控制权。

经过上述过程,图像数据便由CPLD存储到SRAM中,完成图像缓存。

2.3 图像处理模块的设计

图像处理部分主要是从SRAM中读取数据与预存模板进行比较处理,结果由USB或以太网口输出。其中还包括Linux系统移植,驱动程序的编写与移植和ARM图像算法处理等。

3 系统软件设计

系统的软件主要是CPLD编程,把16位的图像信号转换成32位,在数据进行转换之前,首先必需了解从CMOS模块中输出到CPLD的数据时序。

3.1 LM9638 数据输出时序

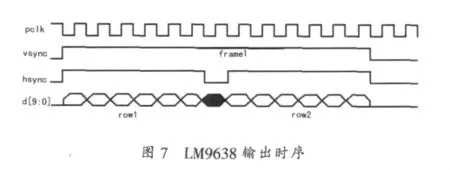

LM9638输出的数字数据包括:10位的图像数字信号d[9:0]、行同步信号hsync、帧同步信号vsync和像素时钟信号pclk。pclk总是固定周期,数字图像输出总线d[9:0]上像素数据和pclk的有效沿是同步的。行同步输出hsync用于选定行数据,在电平模式hsync被确定为一电平(低或高)从每行开始保持到该行最后一像素被读出到数字图像输出总线d[9:0]上。hsync电平总是与像素时钟pclk有效沿同步。帧同步信号vsync,被用作帧内象素数据的指示器。每帧开始时vsync输出脚为一特定标准(高或低)并保持该状态直到该帧结束,hsync也总是与pclk的边沿同步。如图7所示。

3.2 CPLD 的程序设计

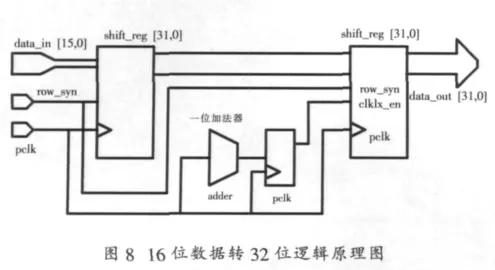

ARM9的数据总路线是32位,而从LM9638输出的图像数据仅仅只有10位,如果将这10位数据放在总线上进行传输,必将造成极大的资源浪费,如果能将这10位数据转换成32位进行传输,不仅节约了资源,而且还提高了传输速率。系统中将这10位数据当成16位进行处理,高6位用0来填充。于是就要求CPLD能把16位数据转换成32位。由于后级的处理位宽是前级的2倍,因此后级处理的时钟频率也将下降为前级的1/2。如果把前级的时钟进行2分频来作为后级的时钟,这种方法引入了新的时钟域,处理上需要采取多时钟域的处理方式,因而在设计复杂度提高的同时系统的可靠性也将降低,为了避免以上问题,这里采用了时钟使能的方法以减少设计的复杂度。其原理图如图8所示。

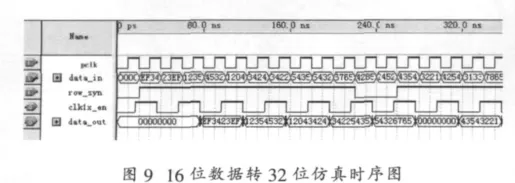

在像素时钟触发和行同步信号有效的情况下,第一个移位寄存器将在第一个pclk下降沿时把16位数据放入移位寄存器的高位,在第二个pclk下降沿时把移位寄存器的高位放入低位,又把输入的16位数据放到移位寄存器的高位,这样以两个pclk周期反复循环,把输入的16位数据转换成32位,第一个移位寄存器的输出直接输入到第二个移位寄存器,第二个移位寄存器在时钟使能信号有效时才把输入转为输出。因为控制输出的时钟使能信号是通过pclk计数触发后形成,相当于pclk的二分频,故能在两个pclk周期内使能一次,在正确的时间内输入输出。下面是软件仿真得到的时序图,如图9所示。

pck即为像素时钟,date_in是16位数据输入,row_syn是行同步信号,clk1x_en是时钟使能信号,date_out是32位数据输出。从图中可以看到,输出有一定的时延,在传输存储的时候不能以行同步或帧同步信号直接作为DMA触发信号,应将其经过延迟处理再作触发信号,保证处理后的信号与输出信号同步,以此能够正确地传输。

3.3 CPLD程序的其它功能

CPLD在图像采集到图像存储的过程中起到桥梁的关键作用,其功能除了将采集的10图像数据转换成32位和与ARM的DMA控制传输,还包括其它功能:

1)CCD模块所需的外部时钟,复位等其它控制信号;

2)EXTBUS信号控制,该信号对存储器的操作有效;

3)提供系统的复位信号,CPLD负责对按键复位信号,电源的reset信号,网卡的复位信号进行判断,从而控制系统复位。

5 结束语

CMOS图像传感器采集的数据经过CPLD转换,通过DMA访问的方式满足了机器智能视觉识别系统的实时采集和处理需求,可以运用于环境比较稳定的识别系统。但对于一些光线亮度偏高或者偏低的环境,图像的亮度往往会影响数据的准确性,进而影响到识别精度,所以对于光线偏暗的环境,可以在拍摄的时候加上闪光灯,对于光线偏亮的环境增加亮度调节功能,尽量将实时拍摄的图像保持与模板一致,或者通过相关算法保证能够不会因为亮度的改变影响识别效果,这也是今后重点研究的方向。

[1]孔德林.基于嵌入式的机器人目标识别视觉系统设计[D].西安:西安电子科技大学,2007.

[2]王建华.基于嵌入式系统的机器人视觉及其在机器人控制中的应用[D].重庆:重庆大学,2003.

[3]符意德,陆阳.嵌入式系统原理及接口技术[M].北京:清华大学出版社,2007.

[4]ARM9基础实验教程[R].深圳:深圳市英蓓特信息技术有限公司,2005.

[5]ARM9 Linux[R].深圳:深圳市英蓓特信息技术有限公司,2005.

[6]吴明晖.基于ARM的嵌入式系统开发与应用[M].北京:人民邮电出版社,2006.

[7]邱永华,贺文健.开放式运动控制器人机界面的研究与设计[J].计算机系统应用,2011,(4):45-49.

[8]邱永华.智能跷跷板小车控制系统的设计[J].电子产品可靠性与环境试验,2011,29(1):32-38.