一种片上系统复位电路的设计

2012-08-13孙国志

孙国志 ,宁 宁 ,张 弛

(1.电子科技大学 电子薄膜与集成器件国家重点实验室,四川 成都 610054;2.深圳贝特莱电子科技有限公司,广东 深圳 518057)

随着集成电路技术的发展,嵌入微控制器MCU(Micro Control Unit)的片上系统 SoC(System on Chip)已经成为芯片设计的主要方向[1]。作为存储程序使用的嵌入式Flash已被广泛应用于其中,以减小芯片的面积和功耗。MCU和嵌入式Flash的存在使得SoC的复位较一般专用集成电路 ASIC(Application Specific Integration Circuit)更加复杂。

一般而言,SoC中的复位通常包括上电复位、外部复位、软件复位和看门狗(WatchDog)复位,合理分配这些复位所作用的模块和范围非常重要。同时,由于SoC在系统复位后需要将程序从Flash搬移至SRAM,此段时间内MCU及相关模块必须保持复位状态,以防止错误执行未准备好的程序,因此复位顺序需要特别留意。此外,对于异步复位的释放需要考虑亚稳态带来的影响。随着测试的重要性越来越突出,可测性设计DFT(Design For Test)在可控性和可观测性等方面对复位网络的设计也提出了要求。

本文设计的电路综合考虑了上述各种因素,能够妥善处理各种复位信号之间的关系及释放顺序,产生正确合理的复位信号,并对DFT设计加以支持。如图1所示。

图2 SoC复位电路图

1 复位电路设计

图1所示的SoC中复位电路的结构框图,由上电复位处理电路、外部复位处理电路、软件复位与看门狗(WatchDog)复位处理电路和复位信号产生等几部分组成。

图2所示为SoC复位电路设计实现的实际门级电路图。

1.1 上电复位处理电路

SoC通常会在芯片上电时进行系统复位。该复位信号(如图1中POR)一般来自于 SoC的模拟部分,与时钟信号的相位关系是不确定的,相对于数字部分而言是一个异步复位信号,故在复位释放时容易引起亚稳态的问题。上电复位处理电路用于实现对POR的同步化处理,以减少亚稳态对电路带来的影响[2-3]。如图3所示,使用两组同步器在CLK域和CLK_32K域分别对POR进行同步化处理。经同步处理后的por_32k和por_clk大大减小了POR释放时可能引起的亚稳态影响,能够提供稳定有效的异步复位。

1.2 外部复位处理电路

SoC中另一个常用的复位信号来源于芯片的外部复位管脚(图1中 external_reset)。外部复位信号容易受到外界环境的干扰,如果该复位信号使用外部按键,还容易引发抖动,造成复位电平的波动,引起系统的不稳定,因此在设计中需要使用去抖电路进行滤波。

图4 外部复位处理电路

图4所示为外部复位处理电路的实际电路图。该电路首先对外部复位信号external_reset进行滤波,再将滤波后得到的复位信号经CLK域同步化处理得到最终的复位信号ext_porn,然后送至复位信号产生电路。

经实验测定,在本设计环境下需要滤除宽度为90 μs以下的毛刺。由于设计中使用了频率为32 kHz的时钟CLK_32K,为了简化电路,使用5级D触发器DFF(D Flip-Flop)级联来完成滤波功能。其中D1、D2为同步器,对 external_reset在 CLK_32K域做同步化处理[4];之后经过 D3、D4、D5分别得到 external_reset的延迟信号。由于CLK_32K的一个周期大约为 30 μs,并且 external_reset为低电平有效,故将各延迟信号经过一个“或”门输出即可得到滤波后的复位信号;该信号经 D6、D7、D8后,得到最终的经过CLK域同步化处理的复位信号ext_porn,送至复位信号产生电路。其中,D6的作用是将滤波后的复位信号寄存,为D7、D8组成的同步器提供稳定的寄存器输出,以避免由于布线及“或”门对信号造成不对称延迟所引起的毛刺被同步器捕获,从而进一步降低亚稳态的影响。

图5所示为 Xilinx自带工具 ChipScope获得的 65 μs低电平信号输入到外部复位管脚时的波形图。从图中可以看到,在此输入下系统没有复位发生。

图6所示为ChipScope获得的124 μs低电平信号输入到外部复位管脚时的波形图。从图中可以看到,在此输入下系统所有模块均被复位。

由图5和图6所显示的结果可以看出,本设计的外部复位处理电路可以将90 μs以下的毛刺滤除。

图5 65 μs外部复位

图6 124 μs外部复位

1.3 软件复位与WatchDog复位处理电路

软件复位在软硬件协同工作的SoC中不可或缺。在某些特定的情况下,需要在软件的控制下对系统或者其中某些特定模块进行复位。此外,SoC中通常使用WatchDog在程序 “跑飞”的情况下使系统复位至初始化状态。图7所示为软件与WatchDog复位电路,其中soft_reset是软件复位信号,WDT是WatchDog复位信号,二者均为高电平有效。由D9、I1和A1所组成的电路用来检测soft_reset或 WDT的上升沿;由 D10、D11、D12和O3组成的电路将信号展宽后,经过反相器I2输出,送给复位信号产生电路。

1.4 复位信号产生

SoC中的复位信号来源繁多,不同的复位信号作用的模块也有所不同,需要对各复位信号进行处理,以得到系统中每个模块所需的复位信号。复位信号产生电路将经过滤波和同步化处理后得到的各个复位信号进行收集,再根据系统需求,经过相应的处理,产生符合要求的各种复位信号,最终分配至系统中各模块,连接至各寄存器复位端。

体表面积是根据身高和体重计算得到的,药品说明书记载的表观分布容积(V d)为(0.61±0.11) L·kg-1,患者的体重对异烟肼的分布是有影响的。体重轻、体表面积小者,药物会较少地分布到组织中,从而清除得更快。亚组分析也显示,不同体表面积的患者其体内异烟肼浓度是有明显差异的。

1.4.1 DMA模块复位电路

SoC在系统上电后,由DMA模块将存储于Flash中的程序读出,然后写入SRAM中供MCU执行。在此过程中,芯片中除DMA之外的其他模块(尤其是 MCU)仍然处于复位状态。因此,DMA模块的复位电路需要独立于SoC的复位网络单独设计。

图2中包括中DMA模块复位信号(dma_rstn)的产生电路。图中,flash_program来自于Flash控制模块,用来指示Flash当前的状态。Flash在芯片外部控制下被烧录时,flash_program信号一直保持高电平,dma_rstn输出为低电平,此时DMA处于复位状态,不进行程序搬移的操作;当Flash完成烧录后,flash_program信号变为低电平,DMA进入正常工作状态时,开始从Flash搬移数据。同样,在外部复位或上电复位之后,DMA开始从Flash中搬移数据。

1.4.2 CGU模块复位信号的产生

SoC中通常包含时钟产生单元CGU(Clock Generate Unit),主要完成对系统时钟分频、时钟切换等工作。为保证系统的稳定性,该模块中的寄存器仅在上电复位信号和外部复位信号的作用下才进行复位,因此仅需将经处理后的ext_porn直接送至该模块。

1.4.3 MCU复位信号的产生

1.4.4 其他模块复位信号的产生

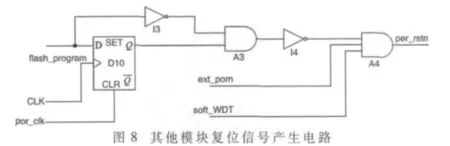

系统中其他模块包括接口电路和Flash控制电路,在上电和Flash烧录结束时都需要将其复位。因此,这些模块的复位电路也需要独立设计。

图8所示为系统中其他模块复位信号产生电路。D10、I3、A3组成的电路用来检测flash_program的下降沿,经过反相器 I4之后,与 ext_porn、soft_WDT一起经过与门A4送出。

1.5 DFT设计相关电路

芯片测试的原则之一是要求被测电路具备良好的可控性。由于SoC中各寄存器的复位端信号全部来自于复位网络的寄存器输出端,在ATPG(Auto Test Pattern Generation)测试模式下,这些寄存器输出会迫使位于扫描链中后级的寄存器输出值被强制清零,从而覆盖正确的测试采样值,违背了可控性的原则。因此,需要在电路中使用选择器,将所有寄存器的复位端旁路至外部复位管脚,以满足可控性的要求,这样就避免了芯片测试过程中前级寄存器的输出端对后级寄存器清零的问题,保证了测试的有效进行。Mux的选择端信号(如图2所示M1~M7的S端)使用测试使能信号scan_en,当退出测试模式回到正常工作模式时,SoC中各寄存器复位端从外部可控复位管脚切换至正常复位网络,功能不受影响。

2 设计结果与分析

本设计采用Verilog语言编写代码,使用NC-Verilog工具进行电路仿真。此外,将整个系统设计适配至Xilinx Spartan-6 FPGA上进行了验证,并通过Xilinx自带工具ChipScope观察设计结果。

由于软件复位和WDT复位信号的处理方式一致,故只给出软件复位测试结果。图9所示为软件复位时系统复位信号产生情况,除了cgu_rstn之外,其余复位信号均将进入复位状态。

图9 软件复位

图10所示为flash_program结束时的验证结果。此时,dma_rstn撤离复位状态;per_rstn有一个系统时钟周期的复位;而MCU一直处于复位状态,直到DMA完成了程序的搬移 (dma_over为高电平),MCU才撤离复位状态;cgu_rstn一直为高电平,即cgu模块没有被复位。

本文设计了一种片上系统复位电路,针对SoC的特点,可以正确稳定地产生各模块所需要的复位信号,同时可以满足DFT设计的要求。Xilinx Spartan-6 FPGA验证结果表明,该电路能够满足系统的应用需求,可以有效正确地复位系统中的各模块,同时可以滤除90 μs以下的外部干扰信号。该设计已成功应用于电容式触控芯片中。

[1]谢平.基于龙芯IP核SoC芯片的FPGA验证技术研究[J].电子技术应用,2010,36(10):128-131.

[2]CUMMINGS C E,MILLS D.Synchronous resets?Asynchronous resets?I am so confused! How will I ever know which to use?[M/OL].(2002-04-xx)[2012-07-31].http://www.sunburst-design.com.

[3]KLEEMAN L,CANTONI A.Metastable behavior in digital systems[J].IEEE Design&Test of Computers,1987,4(6):4-19.

[4]黄良,韩诚山,文明.星载FPGA混合时钟域设计[J].电子技术应用,2010,36(12):42-47.