基于DSN-3500A-119+的雷达锁相环设计

2012-08-10柴晋飞

严 龙,柴晋飞,赵 婷

(1.空军驻784厂军事代表室,成都610051;2.成都锦江电子系统工程有限公司,成都610051)

0 引 言

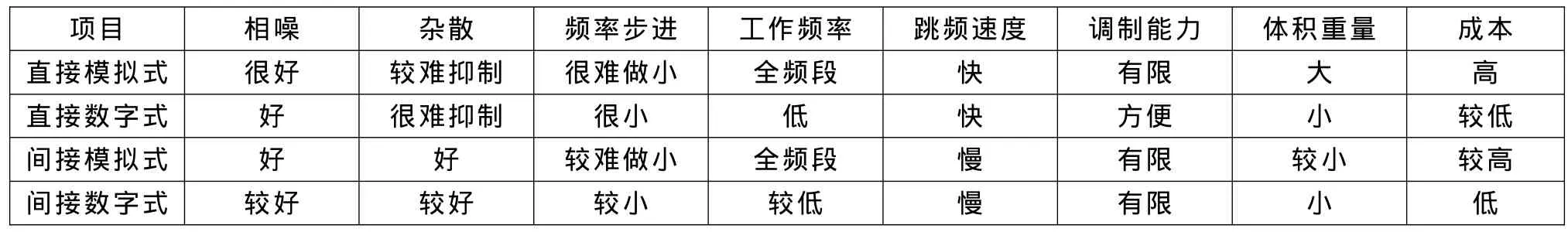

频率源技术是一项技术难度大的先进电路技术,它的好坏直接影响雷达、导航、通讯、空间电子技术及仪器、仪表等的性能指标。频率源可分为两大类:自激振荡源和合成频率源。常见的自激振荡源有晶体振荡器、腔体振荡器、介质振荡器、压控振荡器、钇铁石榴石(YIG)振荡器和波形产生器等。合成频率源是新型频率源,技术含量高,目前被广泛应用于现代电子系统中。合成频率源的主要优点是频率稳定度高、相位噪声低、使用灵活、控制方便、性能优越,缺点是造价高、技术难度大。合成频率源一般可分为直接模拟式频综、直接数字式频综、间接模拟式频综和间接数字式频综,它们的优缺点如表1所示。

表1 合成频率源性能比较表

从表1可以看到间接数字式频率综合器的工作频率不高、跳频速度慢、调制能力有限,但是在体积、重量和成本上优势明显。特别是最近几年集成度的提高,使体积变小的同时设计难度大幅减小。间接数字式频率源是由数字锁相环构成的。本文主要针对雷达频率源对频点保密、体积小、成本低、快速可靠等需求,提出了一种雷达锁相环的快速简单实现方法,能够满足一般场合对锁相环的要求,适合对指标要求不高、但时间紧迫的产品的设计。

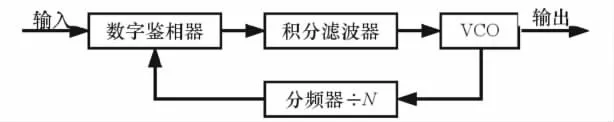

1 数字锁相环的基本结构和工作原理

数字锁相环路的基本结构如图1所示,压控振荡器(VCO)频率除以N,目的是把VCO频率降到鉴相器基准频率左右,送到数字鉴相器进行鉴频鉴相,鉴相器输出通过积分滤波器电路变成模拟电压控制VCO频率,使VCO锁定。VCO误差相位被除了N倍,经鉴相器后等效把VCO相位不稳定度放大了N倍,所以N的大小直接影响输出相位稳定度[1-4]。

图1 数字锁相环路的基本结构

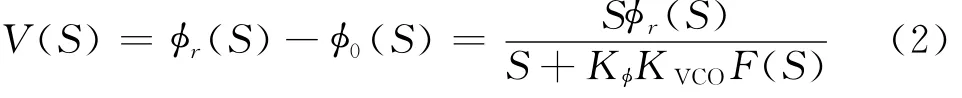

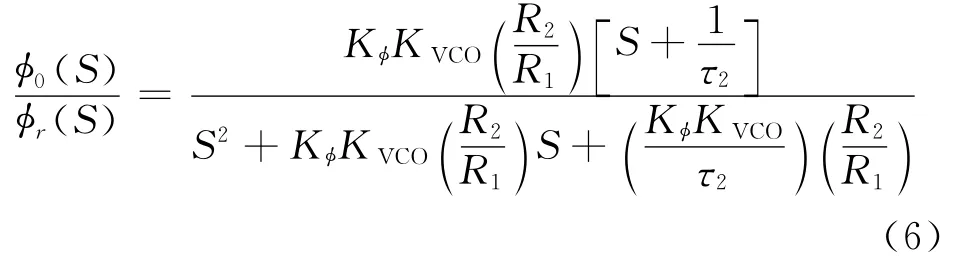

锁相环线性化框图如图2所示,可以推导出环路的传递函数为:

式中:φr(S)为初始相位函数;φ0(S)为输出相位函数;Kφ为鉴相器的增益系数;F(S)为环路滤波器的传递函数的拉普拉斯变换式;KVCO为VCO的增益系数。

图2 锁相环线性化框图

从1 点到输出端的传递函数为:;从2点到输出端的传递函数为:;从3点到输出端的传递函数为:;相位误差函数为:

(1)一阶锁相环

没有环路滤波器的锁相环,即F(S)=1时叫一阶锁相环,是1型反馈系统。锁相环跟踪相位阶跃无净差;跟踪频率阶跃有一定的相位误差,跟踪频率斜升将失锁,所以产生了二阶锁相环。

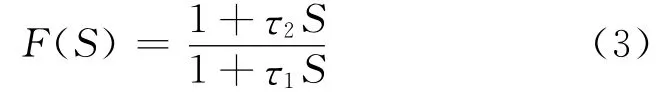

(2)二阶锁相环

在鉴相器输出端有一个低通滤波器,一般选择相位滞后无源滤波器,其传递函数为:

式中:τ1,τ2为阻容滤波器的时间常数。

式通常用环路阻尼系数ξ和自然谐振频率ωn表示:

二阶环的暂态,特征与环路参数有关,也就是与自然谐振频率ωn和阻尼系数ξ有关,在高增益环中,即KφKVCO≫ω的条件下,有关资料给出了各种阻尼系数条件下,随时间变化的暂态误差曲线。工程设计ξ一般都取1,特殊要求可取0.7。

(3)理想积分器的二阶锁相环

按上述分析,导出传递函数为:

噪声带宽

用自然谐振频率ωn和阻尼系数ξ表示:

噪声带宽:

由相位和频率阶跃引起的稳态误差为零。由频率斜升引起的稳态误差为:

VCO最大频率扫描速率为:

2 DSN-3500A-119+芯片介绍

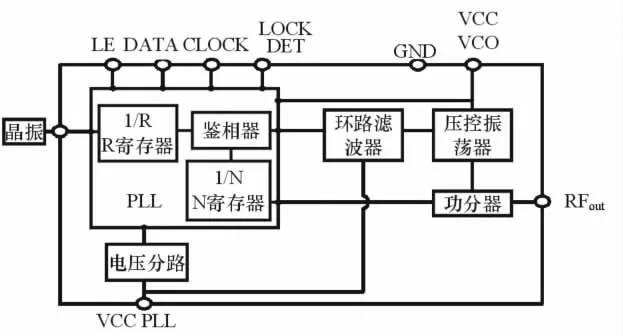

图3是DSN-3500A-119+的功能框图。此款芯片是由Mini-circuits公司生产的集成VCO的频率综合器,输出频率可以通过外部编程改变,频率范围是2 700~3 500MHz,并且输入输出阻抗为50Ω。芯片内部集成了鉴相器、环路滤波器、VCO。鉴相器是ADI公司的ADF4106,其中包含可编程分频器R、可编程计数器A、B和1个双模前置分频器(P/P+1)。通过改变ADF4106的分频器、计数器就可以达到改变频率的目的。ADF4106的控制是通过SPI串口完成的。

图3 DSN-3500A-119+功能框图

由于DSN-3500A-119+集成了环路滤波器,而环路滤波器直接影响环路输出的相噪和跳频时间,所以环路的可调试性不强,但对要求不高的场合,同样设计也被简化。还有就是参考输入要求是10MHz的方波,10MHz晶振是标准值,购货周期可以更快,在体积和成本上也有一定优势。VCO输出对应频点的相位噪声如表2所示。

表2 VCO输出对应频点的相位噪声

从表2可看出,DSN-3500A-119+集成VCO的指标并不差,在频偏为100kHz时,其输出相位噪声在-104dBc/Hz以上。通过鉴相器、环路滤波器、VCO的集成,使整个环路的集成度大大提高,对现在体积小的要求是一种很好的选择,这也是该芯片的优势之一;同时使得设计简化,设计周期缩短。

3 设计实例

3.1 硬件设计

本射频终端接收机本振使用了集成锁相环芯片DSN-3500A-119+,该芯片已经集成了大部分功能模块,使得设计变得比较简洁。本设计首先从电源入手,该芯片需要+5V和+16V2个电源 ,电流大小对应为50mA和16mA。

输入220V,接变压器降压后,通过桥堆,整流成8V和28V直流电源,再通过稳压块,输出5V和24V直流电源。5V可以直接接入该芯片,24V电源再次稳压,得到16V电源。因为通过功能框图可以看到16V电源要供给环路滤波器使用,而环路滤波器的运放电源直接影响VCO的控制端,即直接进入环路。

通过前期试验可以证实:当16V只经过一次稳压,环路会被外界影响,甚至失锁;而且16V和5V尽可能分开,如果16V用电阻分压的方式提供5V,输出射频会有大量杂散。

在电源处理好之后,是晶振的选择。依据技术资料要求,必须选择10MHz方波晶振,同时在频偏1kHz处相噪要在-145dBc/Hz以上。在工作原理推导中知道,锁相环在锁定状态时,频率误差为零,只有一个固定的相位误差,所以输出的频率精度主要由晶振保证。根据需要,选择晶振的频率稳定度为±2ppm(百万分之一)。根据以上条件,可以在温补晶振和恒温晶振中选择。温补晶振和恒温晶振都完全满足上述要求,恒温晶振虽指标更好,但体积大、成本高,所以最后选择温补晶振作为参考。

最后是控制器的选择,由于控制信号线只需时钟(CLK)、数据(DATA)、使能(LE)等3条信号线,而且时序简单,所以选择价格便宜、编程简单的单片机。在本设计中选择的是ATMEL公司的AT 89C2051单片机。

3.2 软件设计

本设计使用单片机AT 89C2051对频率合成器进行控制,如图4所示。

图4 时序控制

用C语言进行编程,以下程序是对DSN-3500A-119+进行初始化编程的主函数部分(输出频率为2 900MHz):

#include<AT 892051.h>

#include<math.h>

#define uchar unsigned char

#define uint unsigned int

sbit LE=0x92;//初始化管脚

sbit DI=0x93;sbit CK=0x94;

void set_L0(uint freq);//频率设置函数void delay_us(uchar time);//延时函数main()

{

DI=0;

CK=0;

LE=0;

set_L0(2900);设置频率点2 900MHz

while(1)

{

}

}

4 试验及测量结果

用频谱仪对输出的杂散进行测量,结果如图5所示。

图5 PLL输出频率2 900MHz(Ref为10dBm)时的频谱

频谱宽度(span)为20MHz,参考电平(Ref)为10dBm时杂散抑制约为60dBc。用频率计对输出的频率测量,测量结果为2 900 000.8kHz。由于条件所限,没有测试相噪。

5 结束语

本文对数字锁相频率合成器进行了研究,用DSN-3500A-119+设计了一个雷达频率综合器。由于DSN-3500A-119+集成度很高,使得设计变得非常简单,设计周期大大缩短,程序稍加更改即可以实现跳频,获得一个多个频点的频综系统,而且功耗也很低,具有很大的实用价值,能降低成本,在雷达设计研究上得到了很好的应用。

[1]吴春华,许富强,周笛青,等.一种单相锁相环的数字实现[J].电气传动,2012,42(6):13-16.

[2]陈鑫,吴宁.数字锁相环的最优化设计[J].南京航空航天大学学报,2012,44(1):87-92.

[3]龚锦霞,解大,张延迟.三相数字锁相环的原理及性能[J].电工技术学报,2009,24(10):94-99.

[4]李鹏,于洪珍,徐小民,等.基于锁相环技术的频率合成器的研究[J].硬件纵横,2009(9):27-29.