垂直集成——延长摩尔定律的有效途径

2012-08-08童志义

童志义,赵 璋

(中国电子科技集团公司第四十五研究所,北京 101601)

摩尔定律一直是驱动半导体发展的金科玉 律,半个世纪以来,半导体的发展始终徘徊在这条定律左右。不过,摩尔定律始终是个有着物理极限的构想,而随着技术不断前行,这个极限已经在人们触手可及的不远处。

当大部份芯片厂商都感觉到遵循摩尔定律之途愈来愈难以为继时,3DIC成为了该产业寻求持续发展的出路之一。然而,整个半导体产业目前也仍在为这种必须跨越设备、制程、设计端并加以整合的技术类别思考适合的解决方案。

随着目前平面化的芯片开始出现多层式结构,半导体制造的基础将在未来几年发生转变。在全球主要的半导体工程领域花费近十年的时间致力于使得这种结构实现可制造化之后,立体的三维芯片(3DIC)的商用化可望在近期开始。

3DIC犹如一幢晶片大楼,如何在既有地基向上搭建与接合仍有许多难题。因此,只有IC设计、晶圆代工及封测厂之间须通力合作,才能确保各个生产环节顺遂无误。

将处理器、逻辑与记忆体等异质晶片以立体堆叠形式做结合的3DIC,具有整合度高的优势,可大幅推升运算效能,并降低耗电量及印刷电路板(PCB)占位空间,因而成为产业竞相布局的新市场。然而,其设计复杂度却远高于传统晶片,无论是技术及成本的挑战皆多如繁星;其中,最大的问题在于如何接合不同类型的晶片,以及晶圆磨薄后如何精确穿孔和对位,方能打造出有效运作的立体堆叠晶片。

目前包括英特尔(Intel)、高通(Qualcomm)、博通(Broadcom)、三星(Samsung)及尔必达(Elpida)等全球十八家晶片大厂,以及掌握晶片最后一道封装关卡的日月光均着眼于异质晶片接合标准对推动3DIC的重要性,已组成JEDECJC11.2标准委员会,快马加鞭地推动逻辑与记忆体晶片接合的介面标准——WideI/OMemoryBus,并可望于年底尘埃落定。如此一来,除能透过标准的依循与协助,加快厂商开发时程,促使3DIC尽早展开量产之外,并可进一步以量制价,一并解决目前3DIC生产成本居高不下的问题。

早期获得3D封装的途径主要是通过先进基板技术来实现的。第一种形式是在多层基板内或多层布线介质中埋置电阻、电容、芯片,基板表面贴装各类片式元器件,这又被称为埋置型3D结构;第二种形式是使用硅集成电路圆片作为基板,在其上进行多层布线,在最上层再贴装片式元件,称之为有源基板型3D结构;第三种形式是在2D的基础上将每一层的封装上下面叠装起来,称之为叠装型3D结构。

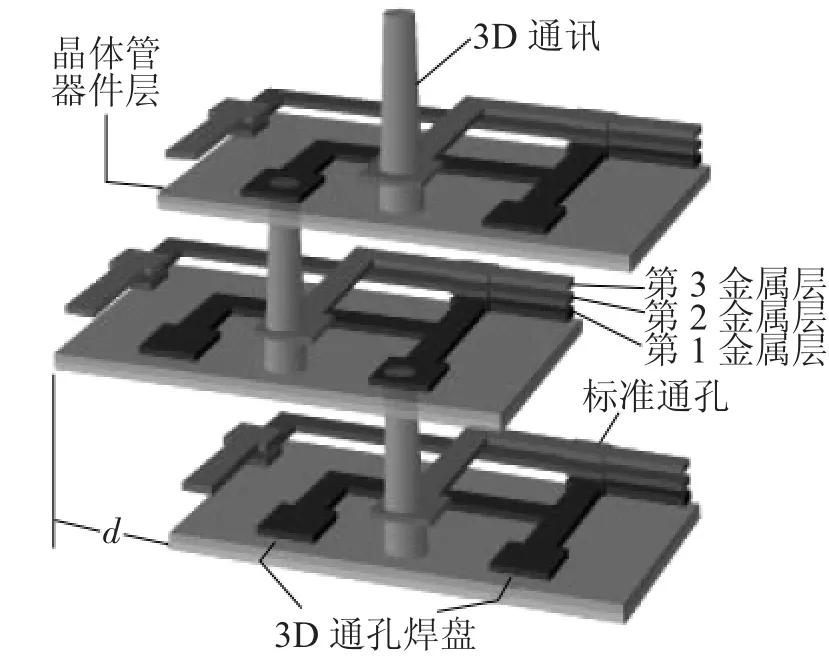

硅通孔(TSV)是三维集成电路(3D IC)的一种主流技术。它是一种系统级架构的新方法,内部含有多个平面器件层的叠层,并经由TSV在垂直方向实现相互连接。采用这种方式可以大幅缩小芯片尺寸,提高芯片的晶体管密度,改善层间电气互联性能,提升芯片运行速度,降低芯片的功耗、设计难度和成本。

目前的3D IC集成被描述为一种系统级架构,内部含有多个平面器件层的叠层,并经由TSV在z方向相互连接。最先的3D应用将会是CMOS图像传感器(CIS),接着是DRAM、逻辑电路上存储器。伴随这一过程,TSV尺寸将不断变小,而硅层厚度也将不断变薄。今天,3D集成被定义为一种系统级集成结构,在这一结构中,多层平面器件被堆叠起来,并经由穿透硅通孔(TSV)在z方向连接起来(见图1)。

图1 采用STV互连的晶圆级叠层

为制造这样的叠层结构,已经开发了很多工艺,其关键技术主要有:

(1)TSV制作:z轴互连是穿透衬底(硅或者其他半导体材料)而且相互电隔离的连接,TSV的尺寸取决于在单层上需要的数据获取带宽;

(2)层减薄技术:初步应用需减薄到大约75~50 μm,而在将来需减薄到约 25~1 μm;

(3)对准和键合技术:或者芯片与晶圆(D2W)之间,或者晶圆与晶圆(W2W)之间。

通过插入TSV、减薄和键合,3D IC集成可以省去很大一部分封装和互连工艺。然而,目前还未完全明确,这些在整个制造工艺中需要集成在什么位置。似乎对于TSV工艺,可以在IC制造和减薄过程中,经由IDM或晶圆厂获得,而键合可以由IDM实现,也可以在封装操作中由外部的半导体组装和测试提供商(OSATS)实现,但这有可能在技术成熟时发生变化。

2011年所发布最令人惊喜的3DIC消息来自于IBM公司。该公司最近透露已经秘密地大规模生产可用于大量消费电子设备的成熟3DIC,不过使用的仍是低密度的TSV技术。由于累积了相当的技术经验,IBM声称目前已掌握了3D的其它工程障碍,并预计能在2012年时克服这些挑战。

3D集成是指将多层平面器件堆叠起来,并通过穿透硅的Z方向通孔实现互连的系统级集成方案。当前,3DIC制造技术的发展正在沿着两大主线向垂直集成拓展。

第一条主线是“超越摩尔”(More than Moore),以技术多元化为研发重点,在一个系统封装内整合不同类型的技术,即通过TSV互连实现的3D集成技术。这条主线还包括克服技术挑战,例如,在系统封装内的裸片间连接、测试和热管理。此外,未来的制程研发计划还包括我们称之为“增值衍生技术”,例如,模拟器件、影像芯片、嵌入式非遗失性存储器、智能功率、量子技术和我们取得巨大成功的MEMS技术。

图2 堆叠芯片

第二条主线是“跟随摩尔定律”,我们称之为“更摩尔”(More Moore)。在晶圆上集成更小的晶体管,降低临界尺寸。在实现28 nm节点后,随后就是采用3D晶体管技术的20 nm和14 nm节点。

1 3D-TSV技术

三维集成封装的一般优势包括:采用不同的技术(如 CMOS、MEMS、SiGe、GaAs等)实现器件集成,即“混合集成”,通常采用较短的垂直互连取代很长的二维互连,从而降低了系统寄生效应和功耗。因此,三维系统集成技术在性能、功能和形状因素等方面都具有较大的优势。最新的3D叠层芯片技术采用FC互连或直接穿过有源电路的多层互连结构,从而能显著提高系统性能。目前正由二维向三维封装技术过渡,包括通过硅通孔(TSV)技术的晶圆级,或者芯片级的堆叠式封装。即便芯片和封装级堆叠技术才刚开始几年,但从制造工艺角度,PoP堆叠式芯片或者TSV等己成为二维封装向三维封装技术过渡的主流形式。

采用硅通孔TSV技术的3D集成方法能提高器件的数据交换速度、减少功耗以及提高输入/输出端密度等方面的性能。存储器件的制造商采用同系列芯片的TSV集成技术来生产芯片堆叠型的动态随机存储器件(DRAM),可提高单位电路板面积/体积上的器件存储容量。这种方法能减少存储器芯片和处理器芯片间信号传输的延迟并能增加带宽。对不同系列芯片进行集成的主要应用是移动设备中的图像传感器和通信芯片。采用TSV技术也可以提高器件的良率,因为大尺寸芯片可以分割为几个功能模块的芯片(小尺寸芯片具有更高的器件良率),再将它们进行相互堆叠的垂直集成(见图2),或者将它们在同一插入中介层上进行彼此相邻的平面集成(见图3)。

图3 硅通孔互连

最近,有两家公司同时发布了在芯片封装方面的革命性突破:一个是意法半导体宣布将硅通孔技术(TSV)引入MEMS芯片量产,在意法半导体的多片MEMS产品(如智能传感器、多轴惯性模块)内,硅通孔技术以垂直短线方式取代传统的芯片互连线方法(无需引线键合),在尺寸更小的产品内实现更高的集成度和性能。另一个则是赛灵思宣布通过堆叠硅片互联(SSI)技术,将4个不同FPGA芯片在无源硅中介层上并排互联,结合TSV技术与微凸块工艺,构建了相当于容量达2000万门ASIC的可编程逻辑器件。虽然同样是基于TSV技术,前一种垂直堆叠业界称为3D封装;后一种互联堆叠称为2.5D封装。这两种不同TSV封装技术的成功量产商用,将会带来一种新的游戏规划——在摩尔定律越来越难走、新的半导体工艺迈向2x nm越来越昂贵的今天,封装上的革命已是一种最好的超越对手的方式。

1.1 硅通孔TSV方案

许多方法都可以实现硅通孔TSV集成工艺。最为简单的一种方法是采用一个硅中介层(如图3所示),在该中介层上先刻蚀出通孔并用金属(通常是用金属铜)进行填充。这种中介层也可以具有镶嵌工艺形成的多层互连结构,用来对彼此相邻放置的芯片形成电互连。采用中介层的方法使得终端产品设计者能迅速地把两个芯片集成在一起,而无需在单个芯片上制作TSV。迄今为止,TSV的发展主要集中在了中通孔(via-middle)方式和后通孔(via-last)这两种方式上,这两种方式都是在有源芯片上制作形成TSV。在中通孔方案中,它是在金半接触/晶体管形成以后,但是在后端工序(BEOL)之前,在晶圆上刻蚀制作出TSV。在后通孔方案中,它是在后端工艺(BEOL)之后,再在减薄晶圆的背面刻蚀制作出TSV。

1.2 异质集成

3D架构从包含 DSP、SRAM、DRAM 等具体功能芯片的圆片开始的。这些圆片经由减薄、对准并垂直连接(芯片对圆片或者圆片对圆片)在一起,成为一个具有整体功能的器件。由于可以集成互不兼容的工艺,3D概念在性能、功能和尺寸上具有巨大优势。在一些分支领域,这被称为“异质集成”,图4为这一概念的示意图。其他还可以添加的器件包括叠层的天线、传感器、电源管理和能量存储器件等。

图4 用于异质集成的3D叠层方案,描述了相互不兼容技术间的集成。(来源:Zycube)

2 3D晶体管技术

3D晶体管技术,实际上是将传统的晶体管二维的平面结构变成三维立体结构,实现了半导体工艺技术中又一次重大的革命。它是由英特尔于2011年5月4日成功开发的世界首个名叫Tri-Gate的3D晶体管。

英特尔称为Tri-Gate的3D晶体管,从技术上讲,应该是三个栅极的晶体管。传统的二维栅极由较薄的三维硅鳍(fin)所取代(见图5),硅鳍由硅基垂直伸出。3D三栅极晶体管实现晶体管的革命性突破。传统“扁平”的2D平面栅极被超级纤薄的,从硅基体垂直竖起的3D硅鳍状物所代替。

栅极包围着硅鳍。硅鳍的三个面都由栅极包围控制,上面的顶部包围一个栅极,侧面各包围一个栅极,共包围三个栅极。在传统的二维晶体管中只有顶部一个栅极包围控制。英特尔对此作了十分简单的解释:“由于控制栅极的数量增加,晶体管处于‘开’状态时,通过的电流会尽可能多;处于‘关’状态时,电流会尽快转为零,由此导致能耗降至最低。而且晶体管在开与关两种状态之间迅速切换,能够显著地提高电路性能。这就像摩天大楼通过向天空发展而使得城市规划者的可用空间一样,英特尔的3D三栅极晶体管结构提供了一种管理晶体管密度的方式。由于这些鳍状物本身是垂直的,晶体管也能更紧密地封装起来——这是摩尔定律追求的技术和经济效益的关键点所在”。

由于3D晶体管结构能够使芯片在电压较低、漏电流较少的环境下运行,较之前的英特尔芯片性能更高、能效更好。据英特尔介绍说,Tri-Gate晶体管能够支持技术发展速度,它能让摩尔定律延续数年。它的22 nm3D晶体管技术芯片从功能上相比32 nm的二维晶体管结构提高37%,而在相同性能下3D晶体管的能耗减少50%,该技术能促进处理器性能大幅提升,并且可以更节能,新技术将用在未来22 nm设备中,包括小的手机到大的云计算服务器都可以使用。

图5 Intel 22 nm的3DTri-Gate晶体管结构

要在22 nm制程时代延续摩尔定律是一项导常复杂的技术。英特尔科学家们在2002年发明了三栅极晶体管,这是根据栅极有三面而取名的。得益于英特尔高度协同的研究-开发-制造技术的集成作业,2010年5月4日宣布的技术突破是多年研发的成果,也标志着3D三栅极晶体管成果开始进入批量生产阶段。

目前,国际上领先的逻辑器件制造商正在探索多栅晶体管(如Fin FET)作为延续摩尔定律的可行途径。通过用多栅极围绕晶体管沟道,这些设计能提高开关速度和抑制漏电流,提供功耗更低、速度更快的逻辑器件。只是按英特尔院士Mark Bohr看法,英特尔至少领先3年,如台积电计划在14 nm时才准备采用Fin FET结构(见图6)。

称为Fin FET的鳍式场效晶体管(Fin Field-effect transistor;Fin FET)是一种新的互补式金氧半导体(CMOS)晶体管,闸长已可小于25 nm,未来预期可以进一步缩小至9 nm,约是人类头发宽度的1万分之1。由于此一半导体技术上的突破,未来芯片设计人员可望能够将超级计算机设计成只有指甲般大小。Fin FET源自于目前传统标准的晶体管-场效晶体管 (Field-effect transistor;FET)的一项创新设计。在传统晶体管结构中,控制电流通过的闸门,只能在闸门的一侧控制电路的接通与断开,属于平面的架构。在Fin FET的架构中,闸门成类似鱼鳍的叉状3D架构,可于电路的两侧控制电路的接通与断开。这种设计可以大幅改善电路控制并减少漏电流(leakage),也可以大幅缩短晶体管的闸长。

图6 IBM Fin FET双栅晶体管

据参加了比利时微纳米电子技术研究机构IMEC召开的技术论坛的消息来源透露,与会的各家半导体厂商目前已经列出了从平面型晶体管转型为垂直型晶体管(以Intel的三栅晶体管和IBM的FinFET为代表)的计划。

其中来自半导体代工巨头台积电公司负责研发的高级副总裁蒋尚义在会上发言称,台积电公司已经决定在14 nm制程节点转向使用垂直型晶体管结构。

欧洲半导体技术研究组织IMEC最近比较了使用一种平面型晶体管以及两种Fin FET垂直结构(分别使用了体硅和SOI衬底)晶体管制程技术分别制造同样的六晶体管结构SRAM电路的结果,这次实物比较的目的是研究平面型晶体管与Fin FET垂直结构晶体管在尺寸微缩能力以及制程变差控制方面的差别。IMEC这次对比测试的结果是Fin FET在制程变差控制方面以及产品良率方面要优于平面型结构晶体管。IMEC表示,根据实验结果显示,两种Fin FET结构晶体管(分别基于体硅衬底和SOI衬底)在用于制造中大规模SRAM阵列时,其产品的良率均相对平面型晶体管更高。

据Business wire网站报道,东芝、IBM和AMD日前宣布,三方采用Fin FET共同开发了一种静态随机存储器(SRAM)单元,其面积仅为0.128 μm2,是世界上最小的实用SRAM单元。

3D三栅级晶体管代表着从2D平面晶体管结构的根本性转变。随着摩尔定律推进到新的领域,3D结构将帮助人们打造令人惊叹且能改变世界的电子设备。摩尔本人对此评价:“在多年的探索中,我们已经看到晶体管尺寸缩小所面临的极限,今天这种在基本结构层面上的改变,是一种真正革命性的突破,它能够让摩尔定律以及创新的历史步伐继续保持活力。”

在将来很有可能发生的是,3D IC集成技术会从IC制造与封装之间的发展路线发生交叠时开始。

3 全球半导体联盟打造3D集成电路计划

台湾地区是世界重要的半导体芯片制造和封装基地,具有开展TSV 3D IC技术研发的基础条件。2008年7月,台湾工研院发起成立“先进堆栈系统与应用研发联盟(Ad-STAC)”。联盟成员包括台湾力晶集团智旺科技、台积电、日月光、南亚、硅品科技、力鼎科技、德国SUSS MicroTec、巴斯夫(BASF)、日本住友精密工业会社等12个国家的30余家半导体厂商,涵盖了材料、设备、EDA工具、IC设计、IC制造、IC封装测试等产业。该联盟主要任务为:共同开发3DIC技术、产品及应用市场;参与国外相关组织,掌握世界发展趋势;结合政府科技发展资源,创造台湾地区产业的竞争优势;促进产业资源共享,包括技术、专利及验证测试等。

Ad-STAC已在台湾新竹建成全球第一条300 mm晶圆3DIC演示生产线,专门用于3DIC研发。该生产线适合多种工艺材料试验,凡是对三维开发有兴趣的机构均可使用该设施,测试新技术、开发新产品。2010年Ad-STAC的工作重点是聚焦平台模块研发与系统层级设计,推动3D IC共通技术与设计平台建设,将与工研院共同开发一套完整的3D IC成本结构分析与动态仿真工具。工研院2010年还将与美国应用材料公司合作,在台湾地区建立全球首座3DIC实验室。作为开放式的工艺研发平台,该平台将整合双方TSV 3DIC工艺技术,开展定制化核心制程设备的合作开发,同时对外提供流片服务,协助半导体厂商降低初期投资,缩短相关集成电路芯片开发时间,迅速地将先进芯片3DIC设计导入市场。

全球半导体产业代言者全球半导体联盟(GSA)2010年年底宣布,将在全球范围提升3D IC技术以及相关教育计划的认知度和可见性。

2010年,GSA在多场全球性行业展会上发表了诸多有关3D IC的学术报告,提高了3D IC技术的认知度。在德勒斯登举行的2010欧洲设计自动化与测试学术会议(DATE)中,GSA成功举办了一次3D教程会议,吸引了欧洲40多家系统与IC的设计师以及EDA代表。DAC期间,GSA 3D IC会议共招待了大约100名与会者。GSA还在美国西部半导体展(SemiCon West)和GSA新机遇展会上举行了其他研讨会和座谈会。由GSA3DIC计划的倡导者、半导体行业的资深专家、Herb Reiter先生领导的3DIC计划工作团队,聚集了几大主要半导体公司及供应链的重要力量,包括EDA、封装和代工。此外,GSA还与IMEC、ITRI、SEMI、SEMATECH 和 Si2 联手,共同指导并参与该项计划。

GSA的宗旨是通过协力合作、整合和创新来培育更加有效的fabless体系,进而担负着加速全球半导体行业发展,提高该行业投资回报率的使命。GSA积极应对包括知识产权(IP)、EDA/设计、晶圆生产、测试及封装在内的供应链所面临的挑战,并提出解决方案。该联盟将为重要的全球化合作提供平台,鉴别并确定市场机会,鼓励和支持企业家,为会员提供全面、独一无二的市场调查报告。其会员包括来自全球25个国家的供应链上下游企业。

当前,全球主要的的半导体组织都为3D技术展开各种标准建立工作。国际半导体设备材料产业协会(SEMI)成立了4个致力于3DIC标准制定的工作小组。此外,其3DS-IC标准委员会包括SEMI会员 Globalfoundries、HP、IBM、英特尔、三星与联华电子(UMC),以及 Amkor、ASE、欧洲的IMEC、台湾工研院 (ITRI)、Olympus、高通(Qualcomm)、Semilab、TokyoElectron 与赛灵思等公司。

半导体制造联盟(Sematech)已经成立了一个3D芯片设计中心。参与成员包括Altera、ADI、LSI、安森美半导体(Semiconductor)和高通等公司。Sematech联盟还在纽约州立大学阿尔巴尼分校科学与工程院设置一条300 mm的3DIC试产线。

比利时微电子研究中心(IMEC)与CascadeMicrotech公司合作为3DIC进行测试与特征化。德国研究机构FraunhoferIZM表示可望在2014年以前将处理器、内存、逻辑、模拟、MEMS和RF芯片整合于单片式3DIC中。

4 垂直集成技术的工艺设备已基本成熟

在过去的1年中,对3D晶体管结构的优化已经取得了相当进展。在刻蚀方面,对刻蚀的速率、剖面结构形貌,以及它们与相关工艺参数之间的优化均已有了很好的了解,从4∶1到12∶1深宽比结构的刻蚀已显示出了极佳的性能。TSV通孔中介质层的淀积工艺在深宽比达到12∶1,其淀积介质层的台阶覆盖率已能做到>60%,并能在深通孔侧壁上淀积厚度大于1 μm的氧化层,该能力使该氧化层可成为大范围深宽比通孔中一种通用型的薄膜层。还将钛/钽阻挡层、PVD铜籽晶层与电化学淀积工艺一起共同进行了工艺优化,以确保能进行无空洞的通孔金属填充。对于后通孔工艺来说,由于器件晶圆需要经过相关的热工艺处理,来将其粘结到临时性的载体圆片上,所以热预算成了一个最为重要的问题。对所淀积的介质层和PVD层都要进行低于200℃的致密化处理,以获得所期望的薄膜的力学和电学性质及其工艺性能。

根据所采用的硅通孔TSV的工艺步骤,介质层(氧化层、氮化层)或金属层(铜层、阻挡层)必须用化学机械抛光来进行去除。近来的工作已经采用了必要的工艺控制对CMP的去除速率实现了优化,以实现层与层之间实现精确的过渡,并能保护好原有的表面形貌。在其它方面的进展也进一步改进了该工艺步骤的效益成本比,这将为降低器件制造工艺的总成本做出贡献。

在经生产验证的300 mm晶圆工艺平台上已经开始对上述工艺步骤(从刻蚀到CMP工序)进行了主要的开发工作,由此大大地降低了与新添设备相关联的传统性风险。晶圆代工厂和独立的器件制造商们通过最小限度的新投资(因此能以低的成本)以及对现有设备的再利用,已在2008年开始了这方面的研发工作。因此,似乎可以推测这些工艺技术可能会获得迅速的提升,进一步发展应用到市场所需产品的试生产中,并且在2012年的后期将会达到满负荷的生产能力。

5 结 论

进入2012年后,半导体产业技术持续进行变革,其中3DIC便为未来芯片发展趋势,将促使供应链加速投入3DIC研发,其中英特尔(Intel)在认为制程技术将迈入3D下,势必激励其本身的制程创新。半导体业者预期3DIC有机会于2013年进入量产,预估2013年应视为是3DIC量产的元年。

对大规模批量生产而言,终端产品的价值必须要与硅晶圆成本之间相权衡。终端产品的价值随应用领域的不同而有着很大的波动,由此其成本的阈值也可能产生变化。实现一个器件芯片堆叠的总成本可以分成两个部分,一部分是晶圆级硅通孔TSV的制作成本(刻蚀、介质衬里层、阻挡层/籽晶层、电化学淀积ECD金属填充、以及化学机械抛光CMP等),另一部分则是晶圆级减薄(粘结、减薄以及剥离等)和芯片级加工处理(切割划片、堆叠、组装以及测试)的成本。当前,后一部分工序的成本占到了总成本的50%以上,产业的标准化(或至少是大家形成共识)将有助于减少材料的成本和加快具有更高产能工艺设备的上市步伐。

从供应链的角度看,加工处理好的硅晶圆需要在TSV工厂和外包组装/测试工厂之间进行运输,此时它们要么是以粘结后的晶圆来运输,要么是将它们安放在载带上进行运输。对于前一种方法,对应的粘结和剥离工艺需要与其成套工艺设备相匹配,这对晶圆厂和组装厂间的供给链产生了约束因素。载带式运输可能是一种可接受的运输方式的选择,但是还需要经过整个供给链的验证。对此,产业界有必要将载体基片、粘结剂以及进行粘结/剥离的相关工艺实现标准化,才能使这些特定的单元工艺能在图像类型的测试中加以实际运用,并能过渡到高效益成本的生产中。为了推动这种“标准化”的进程,当前需要加快材料和设备供应商与用户间的合作,以产生一个对临时性载体基片管理的商业性解决方案。

[1] Jean-Christophe Eloy,3DIC trendsand mid-end foundries growth are changing the rules of IC packaging,[C].SEMICON Taiwan 2011市场趋势论坛Taiwan:SEMI,2011,75-81.

[2] John H.Lau.TSV and Other Key Enabling Technologies of 3D IC/SiIntegrations[C].43rd InternationalSymposium on Microelectronics Raleigh-USA,Raleigh Convention Center,2010.232.

[3] Philip Garrou.3D集成电路将如何实现?[J].集成电路应用,2009(3):39-41.

[4] Philip Garrou.3D集成电路进入商业化领域[J].集成电路应用,2009(5):37-40.

[5] 莫大康.英特尔发布3D晶体管技术延伸摩尔定律[EB/OL].www.21ic.com/news/embed/201105/82518.htm 2011-05-06/2011-11-26.

[6] 王丽英.3D晶体管为摩尔定律注入新活力[J].今日电子,2011(6):22-26.