ECC专用指令处理器软硬件协同设计

2012-07-25徐劲松王志新严迎建

徐劲松,王志新,严迎建

(解放军信息工程大学 电子技术学院,河南 郑州450004)

0 引 言

椭圆曲线密码体制 (ECC)是一种基于代数曲线的公开密码体制,需要进行高强度的密码学运算,而通用处理器在运算性能上有明显的局限性,难以满足实际应用需求。因此,一般使用硬件加速的方法来实现ECC。传统的硬件加速方法是用专用集成电路实现ECC算法,对特定的ECC算法进行硬件优化来获得高性能,这种方法处理速度快,但只能针对特定ECC算法,可配置性和可扩展性十分欠缺,且成本较高。目前专用指令集处理器 (ASIP)作为一种新的硬件加速方案,得到了广泛的研究[1-3],出现了多款各具特色的ECC专用指令集处理器[4-6]。本文设计了一款能实现多种ECC算法的ASIP,能够完成160~576-bit二元域和素数域上的有限域运算。

1 软硬件协同设计流程

ASIP设计通常分为4个关键步骤:应用分析、体系结构设计、代码综合和硬件综合[7]。本文对此4个关键步骤进行了细化与扩展,采用了软硬件协同的方法设计了一款专用指令ECC处理器,具体流程如图1所示。设计采用自顶向下的设计方法,从系统验证、RTL硬件仿真和FPGA硬件原型测试3个不同的层次对处理器的设计工作进行了验证。

设计一款ECC专用指令处理器,要综合考虑不同ECC算法的对性能、面积、功耗等参数的需求,对软硬件进行合理地划分,硬件方面主要进行处理器指令集体系结构(ISA)模型设计,包含指令设计、寄存器设计等;软件方面主要进行ECC算法程序设计以及与处理器配套的软件开发、调试工具的设计,包括指令集模拟器 (ISS)、汇编器等。ISS、汇编器不仅可以作为处理器的开发、调试工具,而且还可以作为处理器的仿真器来使用。系统设计完成后需要对处理器进行系统验证,并根据仿真结果重新对软硬件进行划分,调整处理器体系结构,优化指令集,修改寄存器堆大小,使系统满足设计需求和约束。系统验证通过后可进行硬件RTL设计,将汇编程序编译后的机器码作为激励,对电路结构进行仿真,并进行优化。RTL仿真通过后,建立FPGA硬件模型,对整个系统进行完备性验证。

图1 处理器设计流程

2 处理器指令集结构模型设计

椭圆曲线有加密、解密、数字签名、签名认证等多种应用协议,定义的有限域通常采用素数域和二元域,且运算长度可变。为了满足ECC多种运算形式的需要,结合硬件的约束,对软硬件进行了划分,采用了硬件实现ECC底层运算,软件实现ECC算法流程的形式。

2.1 指令系统设计

ECC各种应用协议都以点加、倍点以及点乘运算规则为基础,具有层次性[8],如表1所示。上层算法可以通过调用下层的算法来实现,点乘运算可以由多次调用点加和倍点操作完成,而点加、倍点运算则可以通过调用有限域上的模运算而实现,包括模加/减、模约减、模乘、模平方及模逆等运算。在此基础上,增加了移位、逻辑运算、比较等指令,从而构成了处理器的运算指令。此外还设计了数据传输指令、控制指令、配置指令等,共4大类指令。其中配置指令为运算单元重构而设计。

表1 ECC算法层次结构

ECC算法具有计算密集型的特点,而且在调用有限域上的模运算来实现点加、倍点运算的过程中,有限域上的模运算操作存在较大数据并行性[9]。超长指令字(VLIW)体系结构是目前常用的一种指令级并行处理方案[10],广泛地应用于DSP等计算密集型的处理器设计。VLIW结构中硬件提供若干个运算单元,各运算单元可并行执行处理器指令,通过编译器静态分析程序中指令的依赖关系将可并行的指令一起发射执行,把通常由硬件实现的功能交由软件实现。VLIW一次发射的最大指令条数由处理器内部运算单元的数量决定,运算单元越多,其对应的寄存器结构就越复杂。因此,运算单元的个数需要根据处理器应用范围来合理设置,做到成本与效率的平衡。

由于ECC底层运算指令较少,基于有限域操作的各种ECC算法流程比较固定,其运算流程的数据并行性可利用编写汇编代码的形式手动挖掘。因此,处理器采用VLIW结构可简化硬件设计,使处理器能够达到较高的并行性能。

在各种ECC算法中,点乘是最主要的运算,决定了ECC算法的实现效率。设计对 Double-and-Add、m-ary、Montgomery、窗口NAF、固定基窗口、固定基的Comb等多种点乘调度算法进行了数据相关性分析,研究了运算单元数量对运算速度、资源消耗的影响,计算出不同并行度下时间开销与资源开销,表2列出了不同并行度下Montgomery点乘算法一轮迭代的时间与资源开销。

表2 不同并行度下Montgomery点乘算法的时间和资源开销

从表2可以看出,用4个运算单元的时间和资源的开销分别是用2个运算单元的1/2和2倍。同时由于运算过程中的数据相关性约束,当运算单元增加时,并不能减少时间开销。

2.2 相关寄存器设计

在现代高性能的微处理器设计过程中,设置适当的存储空间为处理器中的多条指令流提供充足和连续的数据,成为提高处理器性能的关键。存储容量的大小从根本上影响着各运算处理单元之间的数据交互速度,在某种程度上也决定了处理器的灵活性和性能提升空间。这里根据ECC运算数据占用空间的大小,设计了两类寄存器:

(1)静态配置寄存器:主要存储模数/不可约多项式、运算长度、有限域类型、模乘运算常数、功能单元的模式等。这类数据所需存储容量较小,且一旦算法确定,数据一般不会发生变化,因此寄存器端口设置、寻址模式比较简单。

(2)通用寄存器:主要存储外部输入,椭圆曲线相关的常数值,计算过程中的临时数据,输出的数据等。这类数据需要较大的存储容量,主要是运算过程中的临时数据,且某些数据在运算完毕后,就很少再次使用,可以直接覆盖,因此寄存器端口设置、寻址模式比较复杂。对应设计中的4个功能单元,将通用数据寄存器分成4组,每组设有1个写端口,2个读端口;支持直接寻址、增量寻址、寄存器间接寻址等寻址模式。通过对ECC算法进行统计,可以确定通用数据寄存器的容量。表3列出了二元域上部分坐标系下点加/倍点运算所需要的最大储存容量,其中Len表示模运算的数据位宽。

表3 不同坐标系下存储容量需求

2.3 处理器整体结构

依据上面的设计,处理器的结构图如图2所示,主要有控制单元、接口单元及数据通路等3部分组成。控制单元主要完成指令存取、指令译码、指令存储器地址生成等过程中的信号生成工作,负责协调处理器内部指令和外部用户命令的正确执行。接口单元则主要完成外部指令/命令及运算数据的输入以及运算结果的输出。数据通路是ECC处理器的数据执行部分,包含FU0~FU3共4个可并行执行的功能单元、通用向量寄存器堆、静态配置寄存器、回写单元等4个主要部分。4个功能单元是处理器执行指令运算的核心,其功能是可配置的,由静态配置寄存器提供必要的配置参数,来完成不同参数下的运算处理。

图2 ECC专用指令处理器整体结构

3 软硬件协同验证

软硬件协同验证[11-12]是一种在硬件设计确认制造之前,验证软件能在设计硬件上正确运行的过程,需要软硬件同时进行设计验证,及时在硬件和软件之间交换需要的数据。由于ECC专用指令集处理器规模庞大、结构复杂,为了确保设计的正确性,需要从系统验证、RTL硬件仿真和FPGA硬件原型测试等不同层次对处理器的设计工作进行验证。

3.1 系统验证

系统验证是处理器设计过程中不可或缺的重要环节,进行系统验证就是在系统仿真验证平台上运行算法程序的过程。系统级验证一方面用来验证算法的正确性以及该算法在硬件结构上实现的可行性,另一方面用来对处理器的设计空间进行探索研究[13],例如修改功能单元设置,优化指令集,调整寄存器堆容量等。

算法程序设计根据处理器的体系结构,对ECC算法进行并行调度算法研究,充分挖掘运算流程的数据并行性,用设计的专用指令编写并行调度算法作为目标程序代码。仿真验证平台主要是指用C++进行对系统的功能和性能进行描述,建立系统中处理器的虚拟原型;通过汇编器、调试器和仿真器来模拟处理器体系结构,实现算法程序的验证。在本设计中,仿真器主要通过ISS来实现。ISS建立了处理器的ISA模型,通过模拟每条指令在目标处理器上的执行效果来模拟目标机程序[14],能满足处理器在指令精确级的仿真验证,同时配合汇编器、调试器,能够实现处理器配套的软件开发工具。

系统验证的过程如图3所示。算法程序经过汇编器编译得到二进制指令文件,将该文件输入到ISS,对系统进行验证。在验证过程中,通过ISS可以查看目标处理器的内部状态,例如寄存器、程序计数器值等。将输出结果与Certicom Research提供的 测试向 量文件 Test Vectors for SEC1比对,可以验证算法是否正确以及硬件设计是否可行,同时可以根据验证过程中的一些统计数据,对系统进行调整。

图3 系统验证过程

3.2 RTL硬件仿真

在系统验证过程中,采用了ISS逐条模拟用户指令的形式,只能够提供精确到指令边界的处理器状态,无法确定处理器在每个时钟周期的状态。因此,在系统级验证通过之后,有必要进行软件代码与硬件RTL代码的协同仿真验证,通过RTL硬件仿真,来观察电路运行的时序,做到时钟周期精确级的仿真。

进行RTL硬件仿真,需要将系统级设计的ISA模型以硬件描述语言的形式表示出来,同时编写RTL仿真验证的测试文件。测试文件调用与汇编程序相对应二进制文件,作为RTL仿真中的测试向量,通过ModelSim对系统进行硬件代码仿真验证,如图4所示。同时将ModelSim的输出结果与系统验证得到的结果进行比对,以确保RTL描述与ISA模型的设计一致。

图4 RTL仿真过程

3.3 FPGA硬件原型测试

在RTL硬件仿真中,只对设计的RTL硬件描述代码进行仿真,它无法确定设计真实的物理实现与设计描述之间的区别,和硬件实际工作状态还有很大的差别。FPGA硬件原型测试将通过RTL硬件仿真的RTL代码经过综合,下载到FPGA系统中,利用FPGA系统为处理器提供硬件环境,使硬件工作状态更真实,速度更快[15]。

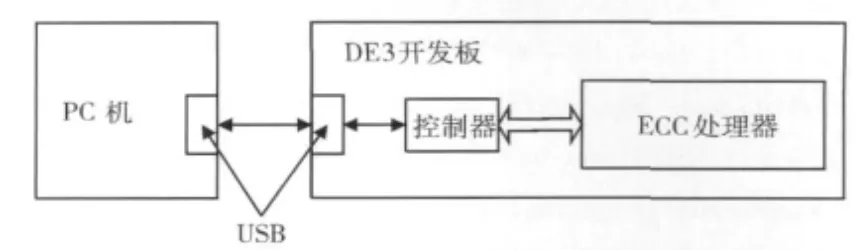

这里采用基于Altera公司EP3SL340H1152C3N芯片的DE3开发板,PC机通过USB接口发送命令,控制器作为开发板上的控制逻辑,通过USB接口接收命令,并对命令进行解析后传给ECC处理器,处理器根据命令对数据进行ECC运算处理,并将最终的运算结果存储到ECC处理器中或将数据通过USB接口传回PC机。如图5所示。

图5 FPGA验证系统组成框架

4 结束语

本文提出了一种软硬件协同设计方法,完成了不同设计阶段的仿真验证,并使用该方法设计了一款专用指令ECC处理器。该处理器可配置性强、速度快、灵活性高,能够完成160~576bit二元域和素数域上的有限域运算,能实现多种ECC应用协议,在不同的应用条件下具有良好的适应性。使用DC工具,采用SIMC 0.18μm CMOS工艺标准单元库,对所设计的ECC处理器进行逻辑综合,在4ns的约束条件下,处理器规模达到了225.89万门,最高时钟频率可以达到250MHz。

[1]Kimmo Puusaari.Application specific instruction set processor microarchitecture for UTMS-FDD cell search [C].Tampere:Proceedings International Symposium on System-on-Chip,2005:46-49.

[2]SHEN Bilong,ZHAO Peng,CHEN Xucan,et al.Research and realization on analysis method of application features faced instruction set design of specific processor [J].Computer Engineering & Science,2009,31 (A01):115-119 (in Chinese).[沈弼龙,赵鹏,陈旭灿,等.面向专用处理器指令集设计的应用特征分析方法研究与实现 [J].计算机工程与科学,2009,31 (A01):115-119.]

[3]REN Kun,YAN Xiaolang,SUN Lingling.An ASIP compiler design and implementation [J].Journal of Circuits and Systems,2009,14 (6):59-62 (in Chinese). [任坤,严晓浪,孙玲玲.ASIP编译器设计和实现 [J].电路与系统学报,2009,14 (6):59-62.]

[4]LAI Jyuyuan,HUANG Chihtsun.Elixir:high-throughput cost-effective dual-field processors and the design framework for elliptic curve cryptography [J].IEEE Transaction on VeryLarge Scale Integration Systems,2008,16 (11):1567-1580.

[5]Tim Guneysu,Christof Paar.Ultra high performance ECC over NIST primes on commercial FPGAs [C].Berlin,Heidelberg:Proceeding Sof the 10th International Workshop on Cryptographic Hardware and Embedded Systems,2008:62-78.

[6]CAI Liang,DAI Zibin,CHEN Lu.Design and implementation of general ECC coprocessor [J].Computer Engineering,2009,34 (4):140-142 (in Chinese). [蔡亮,戴紫彬,陈璐.一种通用ECC协处理器的设计与实现 [J].计算机工程,2009,34 (4):140-142.]

[7]YANG Jun.Research on application specific instruction set processor (ASIP)architecture design [D].Hefei:University of Scinece and Technology of China,2006 (in Chinese). [杨君.专用指令集处理器 (ASIP)体系结构设计研究 [D].合肥:中国科学技术大学,2006.]

[8]ZHANG Jun.Research on technology of application specific instruction and reconfigurable unit of Eliptic curve cryptography processor [D].Zhengzhou:PLA Information Engineering U-niversity,2010 (in Chinese).[张军.ECC处理器专用指令与可重构单元设计技术研究 [D].郑州:解放军信息工程大学,2010.]

[9]CAI Liang.Research and design of the dual-field ECC coprocessor architecture [D].Zhengzhou:PLA Information Engineering University,2008 (in Chinese).[蔡亮.双域ECC协处理器体系结构研究与设计 [D].郑州:解放军信息工程大学,2008.]

[10]SHEN Zheng,SUN Yihe.Architecture design of simultaneous multithreading VLIW DSP [J].Acta Electronica Sinica,2010,38 (2):352-358 (in Chinese). [沈钲,孙义和.一种支持同时多线程的 VLIW DSP架构 [J].电子学报,2010,38 (2):352-358.]

[11]ZHAO Gang,HOU Ligang,LIU Yuan.Methodology of SoC design using hardware/software cosimulation [J].Microelectronics & Computer,2006,23 (6):24-26 (in Chinese).[赵刚,侯立刚,刘源.基于SoC设计的软硬件协同验证方法学 [J].微电子学与计算机,2006,23 (6):24-26.]

[12]BAO Hua,HONG Yi,GUO Erhui.Design of HW/SW coverification platform for SoC [J].Computer Engineering,2009,35 (8):271-273 (in Chinese). [鲍华,洪一,郭二辉.面向SoC的软硬件协同验证平台设计 [J].计算机工程,2009,35 (8):271-273.]

[13]SHAO Yang,LIU Hongjin,HE Xing.A system level methodology for ASIP design [J].Microelectronics & Computer,2007,24 (7):102-104 (in Chinese). [邵洋,刘鸿瑾,何星.专用指令集处理器系统级设计方法 [J].微电子学与计算机,2007,24 (7):102-104.]

[14]YAN Yingjian,YE Jiansen,LIU Junwei.VLIW processor ISA modeling and aided software optimization technology [J].Computer Engineering and Design,2009,30 (11):2727-2729(in Chinese).[严迎建,叶建森,刘军伟.VLIW处理器ISA建模与辅助软件优化技术 [J].计算机工程与设计,2009,30 (11):2727-2729.]

[15]WANG Peidong,LI Fengwei,YANG Juncheng.Hardware/Software coverification solution integrated FPGA and ISS [J].Computer Engineering and Application,2009,45 (30):73-74(in Chinese).[王培东,李锋伟,杨俊成.一种融合FPGA和ISS技术的软硬件协同验证方法 [J].计算机工程与应用,2009,45 (30):73-74.]