基于PCIE的数字信号处理板设计与实现

2012-07-25聂彬彬

聂彬彬,解 放

(中国电子科技集团公司第四十七研究所,沈阳110032)

1 引言

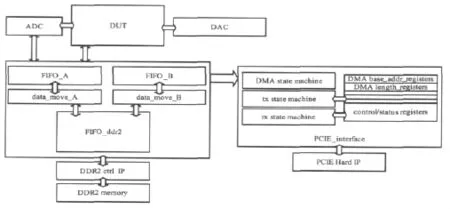

为满足科研项目需求,本文设计了一种可应用于数字上/下变频、FFT等数字信号处理算法评估验证的通用数字信号处理卡,该板卡可将处理后的数据在计算机上显示和分析处理。该板卡主要由模拟数据输入/输出模块,数据存取模块、数字信号处理模块和数据通讯模块构成。模拟数据输入/输出模块主要由模数转换芯片和数模转换芯片构成。该板卡的数字逻辑部分全部在ALTERA公司生产的Arria GX2系列的EP2AG125EF29芯片内部实现,其中数据存取模块由FPGA内部的RAM资源和外接DDR2存储器共同组成,数据通讯模块利用FPGA器件内部提供的hard IP实现本设计所需的PICE接口,并利用WinDriver软件完成PCIE驱动的设计和API封装。本文介绍的板卡内部功能框图如图1所示。

图1 通用数字信号处理板卡功能框图

2 模拟数据输入/输出模块

(1)模数转换芯片使用精度为14位、采样率65MSPS的AD9244,可满足较高的模数转换精度和速度需求。AD9244无需配置,输出数据格式为14位并行数据,便于与FPGA的接口连接,本设计配置2块 AD9244。

(2)数模转换芯片采用精度为16位、采样率为1Gsps的AD9779A。AD9779A为双通道DAC,采用SPI串行总线接口进行配置。由于本文侧重点为通用数字信号处理卡的设计,故对AD9779A的内部寄存器具体内容不作介绍。使用AD9779A需要注意2组16位并行数据输入由FPGA驱动,两组16位数据在布线时要按数据总线处理,尽量确保等长。而AD9779A输出的DATACLK可以作为数据参考时钟接入FPGA的时钟输入管脚。FPGA输出并行数据添加TCO约束后,可以保证并行数据的每一位均几乎同时到达DAC的输入。设置AD9779A内部寄存器以使DATACLK是否反相,未反相或反相的DATACLK中必有一种配置可以使并行数据满足于DATACLK的建立与保持时序关系。这样可以简化当FPGA输出的数据率为100MSPS或更高时的时序设计。

AD9779A的数据经过滤波等环节后可以作为AD9244的输入,为本数字信号处理卡提供信号源。

3 数字信号处理模块

本板卡的设计目的是用于评估数字信号处理算法,故本文不介绍具体数字信号处理模块的实现。Altera公司的Arria GX2 125芯片内部的逻辑资源可用于实现不同的算法。

4 数据存取模块

在评估数字信号处理算法时需要分析数字信号处理前/后以及处理过程中各节点输出的数据,由于FPGA内部RAM空间有限,故本设计采用内部RAM与外扩DDR2内存相结合的方式来完成大容量数据的缓存。为了便于用户使用DDR2内存,本设计将DDR2实现的大容量FIFO_ddr2与由内部RAM实现的FIFO_A和FIFO_B进一步封装为一个模块pseudo_fifo。用户进行FIFO写操作时,数据写入FIFO_A中,用户进行FIFO读操作时,数据从FIFO_B中读出,pseudo_fifo内实现由FIFO_A向FIFO_ddr2的数据搬移逻辑A和由FIFO_ddr2向FIFO_B的数据搬移逻辑B。在DDR2实现大容量FIFO时使用了DDR2内存控制器IP,在FIFO_ddr2内部利用格雷码计数器来生成读/写地址,根据读/写地址的关系来生成FIFO_ddr2的空/满以及近空/近满等标志。数据搬移逻辑A完成写地址递增操作,数据搬移逻辑B完成读地址递增操作。数据搬移逻辑A对FIFO_A的读操作和FIFO_ddr2的写操作、数据搬移逻辑B对FIFO_ddr2的读操作和FIFO_B的写操作,工作在高速时钟200MHz。这样的设计使用户仅需按照FIFO的写时序,就可将待观测的各个信号加入数据存取模块进行缓存,而数据通讯模块也仅需按照FIFO的读时序将缓存中的数据读入,简化了数据通讯模块的设计。

本设计采用容量为2GB的内存,该内存数据位宽为64位,配置内存控制器时使用half rate模式,则FIFO_ddr2的内部数据宽度为256位(64位X4)。则FIFO_A和FIFO_B的数据宽度也设为256位。这样可同时对256路数字量进行采集,采集深度约为64M,由此可知,该板卡具有普通逻辑分析仪无法比拟的数据处理能力。

5 数据通讯模块

PCIE插槽正逐渐取代计算机主板上的PCI插槽,故本设计采用了PCIE协议作为与计算机间的通讯协议。文中数据通讯模块的设计包括固件和软件两个方面。

5.1 固件设计

Arria GX2器件支持PCIE的hard ip实现,对比soft IP实现节省了FPGA的内部资源。为了使PCIE的ip core能与数据存取模块进行通讯,本设计在数据通讯模块内部实现PCIE_interface逻辑。软件可发出读/写寄存器的命令到本板卡上,PCIE_interface逻辑负责对命令进行解释和执行。本板卡上实现了如下寄存器用于控制和观测板卡的工作:

(1)两个寄存器用于控制板卡数据采集的开始和结束;

(2)两片AD9244采集的数字信号在数字信号处理模块进行正交变换时会产生两组同相(I)/正交(Q)分量共四组数据,每组256个共4组FIR系数寄存器用于加载板卡上数字滤波器的系数;

(3)抽取率寄存器可用于设置抽取率;

(4)组DMA基址寄存器、传输字节数寄存器用于设置4组DMA通道,以完成4组数据的上传;

(5)一组状态寄存器用于表示板卡各子模块的工作状态,如FIFO的空/满、近空/近满、FIFO写入/读出数据个数。

(6)一组寄存器组用于设计数控振荡器(NCO)的频率控制字等。

对于寄存器读写操作实现较为简单,即将来自计算机的MWr数据包中的地址进行译码并取出数据包中的数据完成寄存器写操作,将MRd数据包中的地址进行译码并以CPld数据包返回查询的寄存器内容。

为了将数据存取模块中的海量数据上传至计算机,不能采用软件查询操作方式,而需使用中断方式。即通过由本板卡发起的DMA操作,将数据存取模块中的数据以MWr数据包的方式写入计算机内存空间。定义如下状态完成DMA操作:

DMA_IDLE:总线空闲

DMA_REQUEST:板卡请求DMA传输

DMA_ACK:允许本次DMA传输

TX_LENGTH:确定本次传输的数据长度

MWR_REQ:MWr数据包desc准备

MWR_DV:MWr数据包数据传输

MWR_DONE:本次DMA传输结束

DMA_INTERRUPT:所有DMA操作完成产生中断

DMA_WAIT_INTERRUPT_ACK等待计算机软件处理中断

5.2 软件设计

利用WinDriver软件可以简化驱动程序的开发,该公司网站有试用版可供使用。该软件可自动生成驱动程序框架,提供可以访问板卡硬件资源的API,用户只需调用API对板卡固件中实现的寄存器进行读/写,即可完成板卡配置和查看板卡状态。基本的寄存器读写较为简单不做介绍,下面简单介绍如何由软件来初始化和完成一次DMA传输。

(1)通过读取板卡状态寄存器组中的FIFO写入数据个数寄存器,来获得本次DMA一共需要传输的数据字节数。

(2)在计算机内存中分配存储空间供本次DMA使用。

(3)将分配的内存起始地址和待传输字节数写入板卡相应的寄存器。

(4)板卡根据DMA基址寄存器和DMA传输的字节数寄存器的内容来使固件中的DMA状态机开始工作。

(5)当所有数据上传完毕后,板卡发起中断。

(6)软件在中断处理函数中清除板卡中断,准备开始下一次DMA数据传输。

6 结束语

此板卡可进行数字滤波器、上/下变频、FFT等算法的硬件仿真测试,通过外接存储器的方法增加了板卡的数据存储能力,并通过PCIE协议将采集到的数据转储到计算机内存,在计算机上可通过对比MatLab等软件仿真的结果与板卡的数据处理结果来分析数字信号处理算法的有效性。还可以灵活的修改软件和固件使其能够满足科研项目对通用数字信号处理实验平台的需求。

[1] Altera International Limited.Arria II Device Handbook[J/OL].http://www.altera.com.

[2] Altera International Limited.IP Compiler for PCI Express User Guide[J/OL].http://www.altera.com.

[3] Jungo Ltd.WinDriver.PCI/PCMCIA/ISA Low-Level API Reference[J/OL].http://www.Jungo.com.